4GS/s 6位低功耗内插模数转换器设计

谢 莉,余 胜,肖 奔,张艳蕾

(湖南人文科技学院 物理与信息工程系,湖南 娄底417000)

随着半导体技术的连续发展和器件技术尺寸的持续缩小,数字电路部分的速度越来越快,这就要求模数转换器具有高的采样率、高的分辨率和低的功耗。特别是在雷达、无线通信、高数据采集系统等应用领域[1],要求模数转换器具有的采样率达GHz以上。

本文设计了一个采样率达4GHz分辨率为6位的内插低功耗模数转换器,以下是设计构想。

一 总体电路结构

采用并行的结构可以使模数转换所需时间为一个时钟周期,是模数转换器结构中转换速度最快的一种结构,但并行结构的模数转换器功耗大,分辨率低,为此,本文在并行结构的基础上,结合内插技术,使模数转换器转换时间也是一个时钟周期,但由于大大减少了预放大器电路的个数,功耗和芯片面积大大降低,与此同时也大大降低了模数转换器的输入电容,使模数转换器的线性性非常好。图1为本文设计的6位内插式模数转换器结构框图,整个系统由模拟电路部分和数字电路部分组成,模拟电路部分包括内插预处理电路和比较电路,数字电路部分由解码电路组成。内插预处理电路由参考电阻网络、内插电阻和内插预放大器组成。电阻内插与有源(比较器)内插级联的2级内插方式,使其内插因子达到4[2]。

图1 6位内插式模数转换器结构框图

参考电阻网络通过阻值相同的16个电阻对低端和高端参考电压进行分压,得到的17个基准电压分别与输入信号Vin做为17个内插预放大器的输入。17个内插预放大器的差分输出信号通过内插因子为4的内插电路,得到65组差分信号,把低端和高端的2组差分信号用于冗余,剩下中间的63组差分信号分别作为比较器的输入,得到63组差分的温度计码。解码电路首先将温度计码转换成格林码,再将格林码转换成6位二进制码。而达到同样分辨率的并行结构,参考电阻需63个,预放大电路需63个,因此内插技术大大降低了模数转换器的输入电容、功耗与芯片面积,提高了其线性性。

二 模拟电路部分的设计

模拟电路部分包括:参考电阻网络、内插预放大电路、内插电阻和比较电路。

(一)参考电阻网络

当参考电阻的阻值较小时,电流较大,从而导致电阻网络消耗的功耗较大;反之,当电阻阻值较大时,电流较小,电阻网络产生的功耗较低。但在高频模拟输入信号下,预放大器输入对管的栅源寄生电容会耦合到基准电阻梯,出现馈通电压,影响基准电压的准确性,其馈通电压的计算公式[3]为:

U=2n-2πfinRC

(1)

其中U为馈通电压,fin为输入信号频率,C为总输入电容,R为总输入电阻,n为ADC的位数。由公式(1)可知,当电阻阻值较大时,馈通电压增大,从而使电阻网络产生的基准电压发生偏差也大。因此电阻阻值必须在功耗和误差之间折中。

本文设计的6位模数转换器,假设总输入电容为1pF,馈通电压1LSB,输入频率为102MHz的信号,通过公式(1)可知,允许的最大参考电阻值为200,两端参考电压差为0.4V,因此电阻串上功耗0.804mW,功耗极小。

(二) 内插原理

引入内插技术,减少了并行模数转换器中预放大电路的数目,减少了芯片面积,降低了功耗,同时也减少了其输入电容、降低了非线性性。

图3 内插对线性范围的要求

本文采用的内插方式如图4所示,内插放大器输出的差分信号,经过电阻内插与比较器内插的两级内插方式,使内插因子达到4。

图4 两级内插方式

内插电阻阻值不能太小,太小阻值的内插电阻内插放大器很难驱动,要驱动阻值小的电阻,需设计复杂的内插放大电路;内插电阻阻值也不能太大,太大的内插电阻会产生严重的馈通效应,使比较器难以正确比较。所以设计时这些因素要综合考虑。

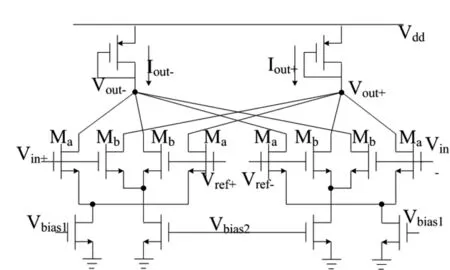

(三)内插预放大器

由内插原理可知,内插预放大电路要求有较宽的带宽和线性范围,但对增益的要求并不高。本文设计的内插预放大电路如图5所示,设计时, PMOS管做为放大器的负载,与采用电阻做负载相比,有较宽的带宽;其次采用两个共源差分电路获得了良好的线性范围,其中Mb管是低负跨导,Ma管是正跨导。其负载电流与电压的输出输入曲线如图6所示,Mb的跨导gmb对Ma的跨导gma非线性部分进行了补偿,使其传输特性呈线性特性,增大了线性范围。

图5 内插放大电路

图6 内插放大电路传输特性

(四)比较电路

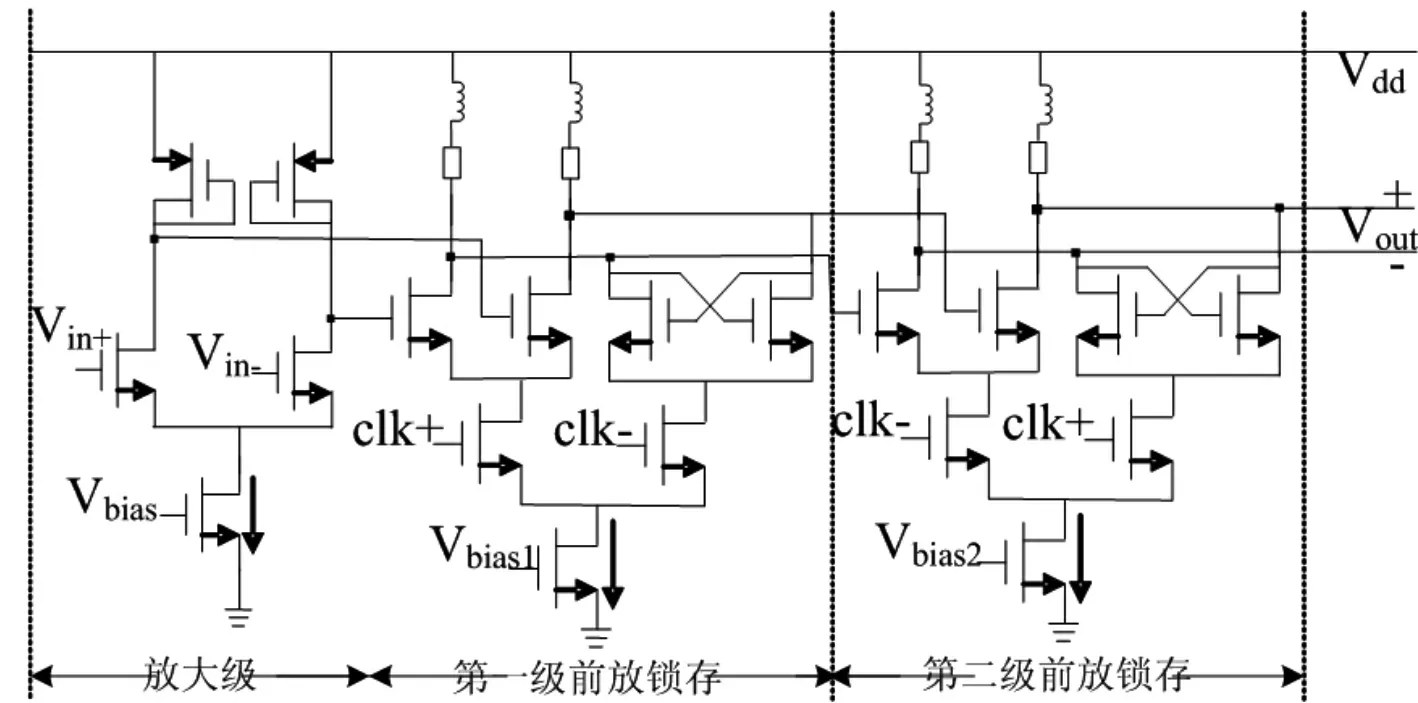

为了使比较器有较宽的带宽、较大的增益和比较速度,在设计时采用多级级联可以达到大带宽和高增益[7]的要求,但一般电路在实现的时,其总的比较时间等于各级电路的时间之和,从而使比较器总比较所需的时间增大。

本文用时钟对各级电路进行控制,使其工作在流水线的工作方式下,因此,整个比较所需的时间就是一个时钟周期,即其中一级电路所需的时间;同时采用电感技术[4],使各级电路比较所需时间降低,从而进一步降低整个比较器比较的时间。

本文设计的比较电路如图7所示,它由前置放大电路、第一级前放锁存和第二级前放锁存三部分构成。在前放锁存电路之前增加了前置放大电路,隔开内插电阻电路与比较电路,有效降低了电路的回程噪声,并将输入信号放大使后级比较电路所需比较的时间减少。同时,两级前放锁存电路由两个相位相反的外部时钟clk+和clk-控制,使电路工作在流水线的工作方式下[5]。当clk+处于高电平时,前级电路为前置放大阶段,此时后级电路为锁存放大阶段,反之,当时钟clk+处于低电平时,前级电路为锁存放大阶段,后级为前置放大阶段。因此比较器比较得到温度计码所需要的时间为2级前放锁存电路中转换时间最大的一级所需时间。

图7 比较电路

三 数字电路部分的设计

本文采用的是基于门级的解码电路,比较器产生的63对差分的温度计码作为解码器的输入信号。解码器对63对差分的温度计码Tn解码为6位格林码Gn,再将格林码转换成6位二进制码Bn。通过格林码的相邻的码之间仅有1位不同的特点,有效地抑制了火花码和亚稳定性产生[6-7]。

由编码理论可知,温度计码、格林码、二进制码之间的关系如公式(2)、(3)所示。本文为了简化电路设计,消除解码电路中G0、G1、G2、G3所用的加法电路,对表达式(2)进行逻辑变换,得到公式(4),由公式(4)可知整个解码电路设计不需用到加法电路,只用异或门与与门实现解码,其解码结构图如图8所示。

同时,为了使减小解码电路解码的时间,通过两级锁存电路(Latch),使解码电路工作在流水线的工作方式下,这样提高了电路的速度[5]。同时,各门级采用电流模式逻辑电路形式[8],及差分低摆幅的信号,降低了电路的噪声影响,具有较低的电路功耗。

G5=T32

(2)

B5=G5

B4=G4⊕B5

B3=G3⊕B4

B2=G2⊕B

(3)

B1=G1⊕B2

(4)

图8 6位解码器逻辑电路图

四 仿真结果

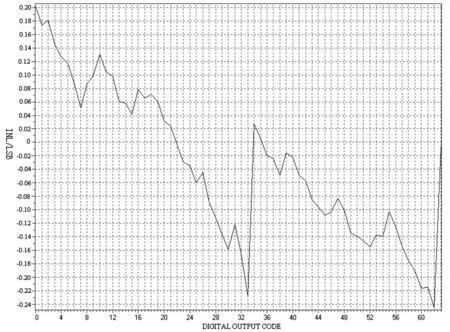

图9—图12是本文设计的模数转换器电路的仿真结果。图9和图10分别为,当模数转换器输入正弦信号和斜波信号时,用HSPICE对其进行瞬态仿真的波形图。参考电压1.0~1.6V,采样频率4GHz,即比较器、解码器的时钟频率,正弦输入信号频率为100MHz,幅值为2/3满量程,斜波信号为满量程,电源电压为1.8V。由仿真结果可知,六位二进制位的差分输出摆幅是±0.4V。且通过MATLAB对6位模数转换器的性能进行仿真,得到其积分非线性和微分非线性如图11和图12所示,由仿真结果可知微分非线性和积分非线性分别小于0.124LSB和0.243LSB,很显然具有良好的线性性能;同时正弦输入信号的频率为100MHz时,在4GHz的采样率下,其有效比特数为5.02bits,且功耗小于220mW。

图9 输入正弦信号的6位模数转换器仿真结果

图10 输入斜波信号的6位模数转换器仿真结果

图11 积分非线性

图12 微分非线性

五 结论

基于0.18μm CMOS工艺上,本文设计了一个6位采样速率达到4GHz的内插模数转换电路。电阻与有源内插级联的内插方式、流水线的工作方式、差分低摆幅的工作状态以及电感技术,使得模数转换器采样速率达到4GS/s,微分非线性和积分非线性分别小于0.124LSB和0.243LSB ,输入100MHz的正弦信号下,有效比特数达到5.02bits,功耗小于220mW。因此本文设计的模数转换器具有合适的分辨率、较高的采样率、较好的线性性及较低的功耗,适用于转换速度要求较高的系统。

参考文献:

[1]PARK S. Design techniques for high performance CMOS flash ananlog-to-digital converters[M]//The degree of Doctoral of Philosophy in the University of Michigan. United States: Electrical Engineering in the University of Michigan,2006:2-4.

[2]NAKAJIMA Y. A Background self-calibrated 6b 2.7 GS/s ADC with cascade-calibrated folding Interpolating architecture [J]. IEEE Journal of Solid-State Circuits, 2010, 45(4):707-718.

[3]莫太山,马成炎,叶甜春.用于低中频GPS接收机的CMOS闪烁型模数转换器[J].微电子学与计算机,2008,25(2):71-75.

[4]PARK S, YORGOS P, MICHAEL P. A4-GS/s 4-bit flash ADC in 0.18μm CMOS[J]. IEEE Journal of Solid-State Circuits. 2007,9(42):1865-1872.

[5]谢莉,王春华.4位5GS/s 0.18μm CMOS并行A/D转换器[J].微电子学,2009,3(39):315-319.

[6]RAZAVI B, Principles of data conversion system design[M].IEEE Press, 1994:12 :272.

[7]艾伦,等.CMOS 模拟集成电路设计[M]. 冯军,等译. 电子工业出版社,2005:557-571.

[8]SCHOLTENS P, VERTREGT M. A 6-b 1.6-Gsample/s flash ADC in 0.18μm CMOS using averaging termination[J]. IEEE Journal Solid-State Circuits,2002, 37(4):1599-1609.