基于FPGA和ARM的图像采集系统设计

钟磊 韩进

摘要:为解决图像数据采集过程中对准确性和实时性的要求,给出了基于ARM和FPGA的图像数据采集系统的设计方法。系统利用CMOS图像采集传感器把外界的图像模拟信号转化为数字信号,采用FPGA控制图像传感器完成图像采集工作,通过ARM对FPGA采集的数据进行处理,并且利用嵌入式操作系统Linux实现对FPGA的实时控制。该系统功耗低、性能稳定,提高了图像采集的准确性和实时性。

关键词:ARM;FPGA;图像采集;CMOS;Linux

中图分类号:TP391文献标识码:A文章编号:1009-3044(2012)01-0211-03

The Design of Image Acquisition System Based FPGA and ARM

ZHONG Lei, HAN Jin

(Shandong University of Science and Technology, Qingdao 266590, China)

Abstract: In order to solve the question of accuracy and real-time in image data acquisition process,the method that designing image acquisition system based FPGA and ARM is put forward.This system uses CMOS image sensor to capture image analog signals outside into digital signals,and uses FPGA to control image sensor to complete the work.It is to do with acquisition data through the control from ARM to FPGA,and use embedded Linux operation system to achieve real-time control of FPGA.This system is low power,high performance,do improve the accuracy and real-time.

Key words: ARM;FPGA; image acquisition; CMOS; Linux

图像处理技术的快速发展,使得图像采集处理系统在提高工业生产自动化程度中的应用越来越广泛。目前的图像采集系统有的基于CCD摄像机、图像采集卡和计算机,有的基于CCD摄像机、解码器、FPGA和DSP,而有的基于CMOS图像传感器芯片、FPGA和DSP,但在准确性和实时性方面都不理想[1]。本文结合实际系统中的前端图像处理和图像数据传输需要,充分利用ARM的灵活性和FPGA的并行性特点,设计了一种基于ARM和FPGA的图像快速采集传输系统,采用基于Marvell的PXA310处理器和Linux的开发平台,而FPGA采用Xilinx公司的Spartan-3XC3S1000来实现本系统的设计。

1系统的总体设计

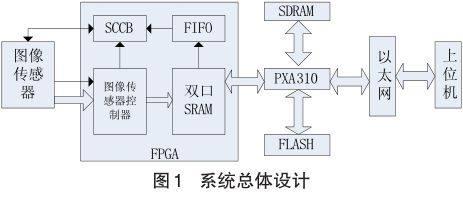

本系统的总体设计如图1所示,其中图像传感器模块负责图像采集,FPGA用来控制CMOS图像传感器芯片,PXA310负责图像数据的交换、以太网芯片的控制及UDP/IP协议的实现,以太网模块主要实现以太网数据传输,SDRAM用于存储图像数据,FLASH为程序存储器。

系统工作时,先由FPGA将CMOS传感器采集的数据存储到双口SRAM,再由PXA310从FPGA的双口SRAM中读取数据并存储到SDRAM,存满一帧图像数据后,PXA310便通过以太网芯片将数据发送给上位机。

2系统硬件设计

2.1图像采集模块

本系统采用OV9650作为图像采集传感器。OV9650是Omni Vision公司的彩色CMOS图像传感器,可支持SXVGA,VGA,QV? GA,QQVGA,CIF,QCIF,QQCIF模式和SCCB接口,并具有自动曝光控制、自动增益控制、自动白平衡、自动带通滤波、自动黑级校准等功能。OV9650的最大帧速率在VGA格式时为30 fps,在SXVGA格式时为15 fps。本系统采用VGA格式[2]。

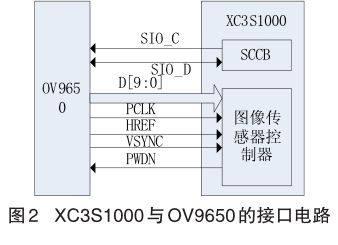

FPGA主要用于图像传感器的控制、图像数据的缓存及外围芯片时序的产生。考虑到图像处理算法的实现需要,本系统选用了Xilinx公司的XC3S1000,它属于SPARTAN-3系列,容量为100万门。在本设计中,FPGA通常运行于80 MHz,XC3S1000与OV9650的接口电路如图2所示,FPGA的内部结构包括CMOS控制单元、SC-CB接口单元、双口RAM单元、FIFO单元等,其中CMOS控制单元又包括帧同步模块、场同步模块、像素时钟模块等。

2.2 ARM处理器模块

本系统的ARM处理器选用PXA310,用于实现图像数据交换和以太网数据传输等功能。PXA310是Marvell公司推出的基于In? ter-XScale架构的微处理器,运行频率最高为625MHz,带有丰富的串行外设接口,并可支持各种存储器芯片[3]。

本系统采用两片SDRAM和两片FLASH存储器,其中SDRAM用于图像数据暂存,选用SAMSUNG公司的K4S561632C-TC75,容量为32 MB。而FLASH程序存储器则选用Intel公司的E28F128J3A-150来作为NOR FLASH,容量为16 MB。

2.3以太网传输模块

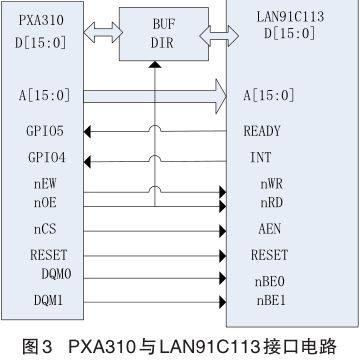

本系统的以太网芯片选用LAN91C113,这是SMSC公司推出的快速以太网10/100 Mbps控制器,支持多种嵌入式处理器主机接口。LAN91C1B内部有8 KB的FIFO,可用于接收和发送数据的存储。此外,LAN91C113芯片还集成了CSMA/CD协议的MAC(媒体访问控制层)和PHY(物理层),IEEE802.3/802.3u-100BASE-TX/10Base-T规范。本系统中,LAN91C113的串行EEPROM接口与AT93C46相连。PXA310访问LAN91C113采用异步静态存储器方式,LAN91C113的地址使能信号AEN与PXA310的静态芯片片选四相连。PXA310与LAN91C113接口如图3所示。

3系统主要模块的软件实现

3.1 FPGA图像采集的实现

OV9650的数据输出采用Bayer原始数据输出格式,每个象素同时只输出一种颜色,奇数扫描行输出RGRG…,偶数扫描行输出GBGB…,FPGA负责图像传感器数据的采集。上电后,系统首先对CMOS图像采集芯片进行初始化,以确定其工作模式,这些参数受OV9650内部相应寄存器值的控制,FPGA通过控制SCCB总线来完成参数的配置。

为控制FPGA实现数据采集,需要一个FPGA模块的驱动程序,在系统中FPGA模块会在新采集的数据量达到阀值后向PXA310发出中断信号,驱动程序接受并处理这个中断。

驱动程序实现的主要功能有初始化FPGA模块,注册FPGA设备,申请中断号;接受FPGA模块的中断信号,并进行中断处理;通过DMA通知应用程序有新数据到达;将FPGA的存储空间映射到用户进程空间。

我们使用Linux内核中提供的两个宏module_init()和module_exit()来对模块[4]进行注册于卸载:

module_init(FPGA_init);

module_exit(FPGA_exit);

首先,我们需要对FPGA模块进行初始化:

struct file_operations fpga_fops = {

.open = fpga_open,

.ioctl = fpga_ioctl,

.fasyne = fpga_fasync,

.release = fpga_release,

.mmap = fpga_mmap,

};

然后,我们需要对FPGA设备进行注册:

register_chrdev_region(devno,1,”fpga_fops”);

cdev_init(&dev.cdev,&fpga_fops);

dev.cdev.owner = THIS_MODULE;

cdev_add(&dev.cdev,devno,1);

最后,在驱动程序结束时我们需要对设备进行卸载:

cdev_del(&dev.cdev);

unregister_chrdev_region(MKDEV(fpga_major,0),1);

3.2 FPGA与ARM的数据交换

FPGA内部用一个8 KByte双口SRAM作为图像存储区。为了实现图像数据的实时采集

与处理,应使图像数据的采集与外部图像数据的读取同时进行,因此本系统采用双缓存结构。

实现方法是把8 KB的SRAM划分成两个大小为4 KB的SRAM(设为SRAM1和SRAM2),每片SRAM一次存储六行图像数据,这样,在同一时刻,一片可用于存储图像数据,另一片可用于外部ARM对图像数据的读取。两块SRAM存储区乒乓式切换,当图像数据写满SRAM1时,FPGA向ARM发送一个中断信号,ARM响应中断并读取SRAM1中的图像数据,同时将其写入到SDRAM中。之后,图像传感器的数据将写入SRAM2,当图像数据写满SRAM2时,FPGA也向ARM发送一个中断信号,ARM响应中断并读取SRAM2中的图像数据,同时将其写人到SDRAM中。之后,图像传感器的数据将再次写入SRAM1。

3.3以太网数据传输的实现

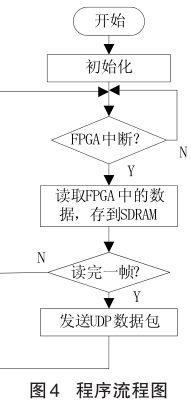

为实现图像数据的网络传输,本系统基于PXA310开发了UDP/IP协议实现程序,以将图像数据存储在SDRAM中。一个完整的数据帧格式包括以太网头、IP头、UDP头和一行图像数据,其系统工作流程图见图4所示。

上电后,系统将等待FPGA中断,如果中断产生,则由PXA310读取FPGA中的数据并写到SDRAM中。然后判断是否读完一帧图像数据,若读完,则发送UDP包,并将图像数据通过以太网发送到上位机,否则继续等待FPGA中断。

4结束语

本文给出了基于ARM和FPGA的实时高数据图像采集系统,ARM具有成本低、功能丰富、开发简单,FPGA可以设计为各种逻辑功能,设计灵活并且并行处理,因此运行速度快,适合于高速场合。利用两者的优点所构建的ARM和FPGA平台具有更好的处理速度和处理能力,可以满足实时性的要求。随着ARM和FPGA综合激活素的发展,ARM和FPGA综合技术正在向着并行运算技术以及分布式运算技术方向发展。

参考文献:

[1]朴现磊,熊继军,沈三民.基于FPGA的高速数据采集系统的设计[J].微计算机信息,2008,24(2): 209-211.

[2]梁志毅.基于ARM Linux的高速数据采集技术研究[D].北京:北京交通大学,2006.

[3]杨庭栋.多媒体处理器PXA310在智能手机中的应用研究[D].上海:上海交通大学,2010.

[4]弓雷.ARM嵌入式Linux系统开发详解[M].北京:清华大学出版社,2010:38-88.

[5]宋宝华.Linux设备驱动开发详解[M].北京:人民邮电出版社,2008:75-111.

[6]冯忠岭,童英华.嵌入式Linux的设备驱动程序设计及交叉编译[J].计算机工程与应用,2008,44(6):121-123.

[7]王洪辉.嵌入式系统Linux内核开发实战指南(ARM平台)[M].北京:电子工业出版社,2009:43-54.

[8]刘淼.嵌入式系统接口设计与Linux驱动程序设计[M].北京:北京航空航天大学出版社,2006:350-359.