超大规模集成电路可靠性评估综述

朱旭光

摘要:为适应系统级芯片(SoC)高性能的要求,超大规模集成(VLSI)电路的密度和复杂度不断增加,从而为SoC芯片的可靠性带来了严峻的挑战。因此,准确评估VLSI电路的可靠性成为一个重要问题。该文主要从不同的层面和角度综合概述了前人及本课题组对VLSI可靠性进行评估的方法和策略及其解决的问题,最后结合作者的实际工作,描述了应进一步完善的工作并指出了当前工作的不足和困难。

关键词:超大规模集成电路;系统级;寄存器传输级;逻辑级;晶体管级;可靠性评估

中图分类号:TP311文献标识码:A文章编号:1009-3044(2012)01-0204-03

An Overview of the Reliability Evaluation of Very Large Scale Integrated Circuits

ZHU Xu-guang

(Department of Computer Science and Technology, Tongji University, Shanghai 201804, China)

Abstract: To meet the high performance requirements of SoC (System on Chips), the density and complexity of VLSI is increasing contin? ually, and these have negative impacts on circuit reliability. Hence, accurate reliability estimation of VLSI has become an important issue. This paper has introduced the problems and the existing reliability techniques of reliability estimation based on the early achievements. Fi? nally, this paper described the further work, the deficiency and difficulties of the current work combined with the authors working.

Key words: VLSI; system level; register transfer level; logic level; transistor level; reliability evaluation

超大规模集成(very large-scale integrated, VLSI)电路及其相关技术是现代电子信息技术迅速发展的关键因素和核心技术,对国防建设、国民经济和科学技术的发展起着巨大的推动作用。人们对信息技术产品(主要指数字计算系统)的依赖程度越来越大,这直接牵涉到人们的生活质量,甚至关系到人类生命、财产的安全问题。因此,当前人们在应用这些产品的同时,必然会提出更高的要求,即除了传统意义上的要求和标准以外,还提出了更重要的评价体系---系统所提供服务的“可靠性”标准问题[1]。

目前,军事电子、航空航天、工业、交通、通讯,乃至普通人的个人生活都对VLSI电路和系统提出了越来越高的可靠性要求,而同时随着集成电路技术的发展,尤其是深亚微米、纳米工艺的应用、电路规模不断扩大,特征尺寸不断缩小,电路密度不断提高,给芯片的可靠性带来了严峻的挑战。因此,对VLSI电路的高可靠性研究变得越来越重要。可靠性技术研究一般包括可靠性设计与模拟、可靠性试验与评估、工艺过程质量控制、失效机理与模型研究,以及失效分析技术等五个主要的技术方向。

传统上对VLSI电路可靠性的研究主要是针对制造过程的,内容包括成品率计算模型、缺陷分布模型、软(硬)故障影响的可靠性模型、电路的串扰与延迟、电路可靠性与成品率的关系等。在集成电路制造过程中,由于各种工艺扰动会不可避免地在硅片上引入缺陷,从而引起集成电路结构的局部畸变。这些局部畸变可能改变电路的拓扑结构,导致集成电路成品率下降。因此,缺陷的几何模型、粒径分布是影响成品率的重要因素之一。另外,在深亚微米和纳米工艺下,软故障的干扰越来越严重,相关的研究包括软故障影响下导线可靠性模型、故障关键面积计算等。已有的研究表明可靠性和成品率存在正相关关系,其正相关性需要考虑线宽、线间距等版图的几何信息和与工艺相关的缺陷粒径分布等参数。面向制造过程的可靠性研究准确性好但存在较大的计算开销。

于是在制造出集成电路产品后,通过筛选和可靠性试验估计其可靠性,并采用加速寿命试验确定产品的平均寿命。如果发现可靠性不满足要求,就要从设计和工艺角度进行分析,并加以改进。长期以来,评价器件质量和可靠性的方法分为三类[2]:(1)批接收抽样检验,检验该批产品是否满足产品规范要求;(2)可靠性寿命试验,评价产品的可靠性水平;(3)从现场收集并积累使用寿命数据,评价相应产品的使用质量和可靠性。

近年来,VLSI电路集成度不断提高,同时可靠性水平也迅速提高,传统的评价方法暴露出了各种各样的问题,如批接收抽样检验方法因分辩能力有限而不能有效区分高水平产品质量之间的区别;可靠性寿命试验方法因要求的样本数太多而导致成本上升;基于现场数据收集的方法因存在“滞后性”而不能及时对产品质量进行评价等,这就促使人们开始研究新的评估技术。

当前对可靠性研究主要的数学模型有[3]:可靠性框图模型、故障树模型、马尔科夫模型、Petri网模型、状态空间分解模型及概率模型等。

虽然这些模型较好的解决了一系列的问题,但是在对VLSI电路进行分析时,由于没有涉及到电路的具体逻辑结构,也就是说只是粗略的分析了一下电路的可靠性,这是不够准确的,当然也是具有现实参考价值的。

在下一步工作中,作者将深入到电路的具体逻辑层和现实的环境当中,对其进行更加深入和具体的研究,以便给出更加准确和更有价值的计算值。

1不同层面可靠性评估

对数字VLSI电路进行模型化或设计描述,按照抽象级别由高到低大致可以分为行为级、寄存器传输级、逻辑级、电路级、晶体管级。目前,可靠性评估方法的研究主要集中在电路逻辑级以上,通过故障注入或模拟的方法分析信号可靠性。

一般而言,电路可靠性分析基于抽象级别越高,时间开销越少,能用于大规模电路或者处理器系统的评估,但是由于远离物理实现,准确性低。反之,分析的抽象级别越低,必然考虑低层实现中的缺陷分布,环境因素等参数,越接近芯片制造的真实过程,所以更加准确,但是存在一个普遍问题是耗时大,无法用于复杂电路。

1.1行为级可靠性评估

在高层测试可以及早地发现设计错误,便于及时修改,减少设计成本,缩短研发时间。当前集成电路高层测试所面临的最大困难是:缺少能准确描述高层故障实际类型的故障模型,并且模型的评估方式也较单一。

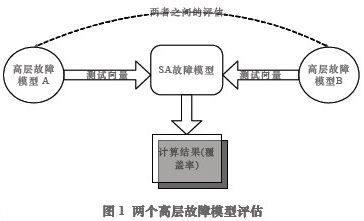

目前,国内外学者对高层故障模型的研究已做了许多有益的工作,如:模仿软件测试的覆盖方法(包括状态覆盖、语句覆盖、分枝覆盖等)、基于电路结构提出的故障模型等。这些故障模型在处理某类电路时都表现出了一定的优势,但是并非对所有类型电路都有效。这也表明,当前高层故障模型依然不够成熟;高层故障模型与门级网表中的SA(固定型故障模型)故障之间的关系依然不清晰;模型的评估也有待于改进。现存的故障模型中,比较成功的有:传输故障模型[4],变量固定型模型[5]。对模型的评估,常用的方法是覆盖率评估,一般分为两步,如图1所示:(1)依提出的故障模型作测试生成,得到测试向量;(2)将测试向量在门级网表作模拟,计算其对SA故障的覆盖率。另外还有一些是考虑电路的可观测性的测试生成与评估方法[6]。总之,这些评估方法,都是基于对SA故障覆盖率的计算。

图1两个高层故障模型评估

1.2逻辑级可靠性评估

正如上文所述,评估方法所对应的电路抽象级别越高,其准确性则越低。而同一抽象层次上不同类型的方法相比,解析方法最为省时。逻辑级的解析模型方法相对准确,且易于理解和操作。

由于逻辑电路对差错具有一定的屏蔽作用,作为瞬时故障的软差错并非一定会导致电路锁存错误内容或者输出错误结果,因此,建立概率模型来评估逻辑级电路可靠性是合理的。

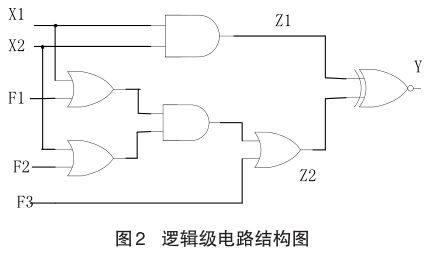

逻辑级概率模型通过计算发生在电路逻辑门或线节点差错传播到原始输出的概率来衡量其失效率,考虑了电路的拓扑结构和传播路径信息,并与组成电路的各个门类型和连接方式有关,如图2所示,目前典型的方法包括:计算单个输出节点软差错率的TP方法[7],通过计算差错传播率表征电路软差错率的EPP方法[8],以及通过概率转移矩阵模型评测整个电路可靠度的PTM方法[9]。其中,TP方法和EPP方法只计算部分电路的失效率,而PTM可以度量整个电路的可靠性。但是,未经优化的TP、PTM算法的计算时空开销较大,只能适用于小规模电路。基于PTM方法具有良好的完备性,并且模型简单而准确,为解决其因时空复杂度大而不能直接用于大规模电路的问题,文献[2]对PTM方法进行了深入的研究,并提出了合理的改进方法。

1.3晶体管级可靠性评估

超深亚微米下的CMOS电路可靠性是由MOSFET的微观失效机制来决定的,对CMOS电路可靠性的评估和改善应该在失效模式分析和对基本物理失效机制正确理解的基础上进行。因此在对电路可靠性进行评估时,需要进行下面四方面的工作:

1)对MOSFET栅氧层退化机制进行建模。MOSFET中热载流子注入效应、负偏置温度不稳定性、栅氧可靠性的经时击穿效应这三种失效机制是影响到超大规模CMOS电路长期工作可靠性的最主要因素。它们都是由氧化层陷阱电荷作用或界面态积累作用而导致了栅氧层作用的退化而造成器件特性的退化。

2)对产生局部氧化层损伤的MOSFET器件行为进行建模。MOSFET中的HCI和NBTI效应都会对器件的主要I-V特性参数产和程度不同的影响。

3)在电路长时工作条件下,对器件栅氧层退化进行仿真。正常的电路中器件一般都是处在AC应力条件下,要对电路的可靠性进行准确的评价,必须先要能够对AC应力下MOSFET长时间工作后的器件性能进行评价。

4)评价处于失效应力作用下的整体电路的性能。

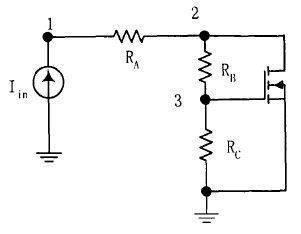

电路可靠性研究的一个重要部分集中在器件级设计[10],其包括:对失效机制更好的理解和建模;圆片级测试结构的革新以改善可靠性控制;阻止器件退化的结构的研究。其中,器件退化对电路性能的影响受到了更多的关注。在设计阶段预测电路可靠性的方法有着非常大的价值。随着可靠性仿真技术的逐渐成熟,芯片的可靠性设计概念被提上了日程。对最终的电路可靠性评价在IC设计阶段完成,大大降低了芯片设计风险。图3为晶体管级电路的结构。

图3晶体管级电路结构图

从以上可知,可以从不同层面来对VLSI电路进行可靠性评估,不同层面的可靠性评估有其不同的优势与不足。较低层次的可靠性分析通常比较准确,但是其功耗和时间开销大,只能对中小型电路进行分析。高层次的可靠性分析由于远离物理实现,准确性低,但是可处理性好。根据作者的研究认为,兼顾准确性和可处理性是对可靠性研究的突破点,这就要将电路的不同层次间相互映射,以尽可能贴近电路的真实行为。从而在电路的设计阶段就能够比较准确地估计其可靠性,尽早调整改进,避免出现因结构设计上的不足而导致的芯片缺陷,从而提高芯片的可靠性和成品率,缩短芯片的设计和生产周期。

2结论

由IBM、Sony、Motorola等多家知名半导体公司最新研究进展表明,可靠性问题始终伴随着半导体器件与大规模集成电路的发展和应用,随着集成电路技术的发展,VLSI电路的可靠性问题变得越来越突出。加强对半导体器件与集成电路的可靠性分析、模拟、评估和改进已经成为超大规模集成电路发展中的重要课题。目前VLSI电路的可靠性研究得到广泛的关注,对越来越多的失效模式和机理进行了研究,并且从理论和实践上不断提出了改进方法,这些研究成果为可靠性增长提供了评价标准与依据。

参考文献:

[1]徐拾义.可信计算系统设计和分析[M].北京:清华大学出版社,2006.

[2]王真,江建慧.基于概率转移矩阵的串行电路可靠度计算方法[J].电子学报.2009,37(2):241-247.

[3]肖杰,梁家荣.具有失效结点和链路的E-2DMesh网络可靠性研究[J].计算机应用研究,2009,23(3):201-204.

[4] Yi Zhigang, Min Yinghua, Li Xiaowei, et al. A Novel RT-Level Behavioral Description Based ATPG Method [J]. Journal of Computer Sci? ence and Technology, 2003, 18(3): 308-317.

[5] Corno F, Prinettp P, Reorda M S. Testability Analysis and ATPG on Behavioral RT-level VHDL[C]. Proceeding of International Test Con? ference, Washington, 1997: 753-759.

[6] Fallah F, Devadas S, Keutzer K. OCCOM-efficient Computation of Observability-based Code Coverage Metrics for Functional Verifica? tion [J]. Computer-aided Design of Integrated Circuits and Systems, 2001, 20(8): 1003-1015.

[7] Kim J S, Nicopoulos C, Vijakrishnan N, et al. A probabilistic model for soft-error rate estimation in combinational logic[A]. In: Proc. of the 1st Int`l Workshop on Probabilistic Analysis Techniques for Real Time and Embedded Systems[C]. Italy, Elsevier Science, June 2004, pp. 25-31.

[8] Asadi G, Tahoori M B. An analytical approach for soft error rate estimation in digital circuits[A]. In: Proc. of the IEEE Int Symp on Cir? cuits and Systems[C].Kobe, John Wiley & Sons, May 2005, pp. 2991-2994.

[9] Krishnaswamy S, Viamontes G F, Markov I L, et al. Accurate reliability evaluation and enhancement via probabilistic transfer matrices[A]. In: Proc of the Design, Automation and Test in Europe Conference and Exhibition[C].Orlando, IEEE CS Press, March 2005, pp. 282-287.

[10]李康.超深亚微米集成电路可靠性设计与建模方法[D].西安电子科技大学博士学位论文,2005.