基于FPGA的行间转移型面阵CCD驱动电路设计

杨 凯, 李钟慎, 吕素英

(华侨大学 机电及自动化学院,厦门 361021)

基于FPGA的行间转移型面阵CCD驱动电路设计

杨 凯, 李钟慎, 吕素英

(华侨大学 机电及自动化学院,厦门 361021)

分析行间转移型面阵电荷耦合器件(CCD)ICX055AL的工作原理和驱动时序,以现场可编程门阵列(FPGA)为硬件设计载体,采用Verilog硬件描述语言(HDL)设计CCD驱动时序,结合CCD时钟驱动芯片CXD1267AN和2片74HC04构建出CCD驱动电路。通过QuartusⅡ软件对其进行仿真分析,并对芯片EP2C5Q208C8进行配置。结果表明,所设计的驱动电路可以满足ICX055AL的各项性能要求,能够产生准确的脉冲信号驱动ICX055AL工作。

面阵电荷耦合器件;ICX055AL;驱动电路;现场可编程门阵列

电荷耦合器件(Charge Coupled Device,CCD)作为光电转换式图像传感器,以其灵敏度高、动态范围大、光谱响应宽、体积小、功耗低、分辨率高和采样速度快等一系列特点[1],成为现代电子学和现代测试技术中最活跃的传感器,被广泛运用于机器人视觉、安全保卫系统、智能交通系统以及Internet接入装置[2-3]。而在各种各样的CCD应用技术中,CCD驱动电路的设计已成为最为关键和重要的技术。驱动时序电路性能的优劣直接决定了CCD的应用品质,而驱动时序电路是根据CCD芯片的类型和自身参数来设计的[4-5]。CCD驱动电路设计一般有2种方案:① 用现场可编程门阵列(Field Programmable Gate Array,FPGA)或复杂的可编程逻辑器件(Complex Programmable Logic Device,CPLD)产生CCD正常工作所需的时序驱动信号[6-9];② 用专用的CCD驱动芯片,实现对CCD的驱动[10-11]。前者要求开发者熟悉硬件描述语言,且实现灵活、方便的功能扩展和系统升级,而后者只需对寄存器进行设置,编程简单,但可扩展性差。综合考虑系统的性能要求和灵活性,本文CCD驱动电路的设计采用第①种方案。

1 行间转移CCD驱动时序发生器原理

1.1 面阵CCD图像传感器ICX055AL

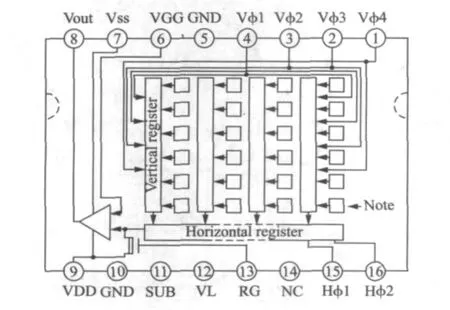

ICX055AL是SONY公司生产的一款面阵图像传感器。该器件为垂直四相驱动、水平三相驱动的行间转移型面阵CCD,它增加了可调电子快门的功能,具有极低的暗电流及很低的像元读出噪声。如图1所示,ICX055AL由空穴积累二极管(Hole Accumulated Diode,HAD)传感器构成的光敏单元阵列、CCD移位寄存器阵列、水平模拟移位寄存器等3部分构成[12]。驱动该芯片正常工作需要7路时序驱动脉冲,分别为垂直时序驱动脉冲Vφ1,Vφ2,Vφ3和Vφ4,水平时序驱动脉冲为Hφ1,Hφ2和Rg,这些时序驱动脉冲均由CCD驱动时序发生器产生。

图1 ICX055AL芯片结构图Fig.1 Structure of ICX055AL

1.2 ICX055AL的驱动时序分析

ICX055AL的一个工作周期分成两个阶段:转移阶段和感光阶段。转移阶段主要完成光积分区积累的电荷向垂直移位寄存器的转移,同时将相邻行信号电荷包合并。感光阶段主要实现3个功能:① 信号电荷在光积分区的积累;② 将垂直移位寄存器内的信号电荷包逐行转移到水平模拟移位寄存器;③ 信号电荷包从水平模拟移位寄存器向输出放大器串行输出给后续电路[12]。其具体的工作过程如下:

1.2.1 转移阶段 四相垂直驱动脉冲按一定顺序依次变化实现信号电荷包的转移。在信号电荷包转移时,电荷包从感光单元转移到电极Vφ1和Vφ3下面。根据奇数场和偶数场相邻行电荷包的合并关系不同,当奇数场输出时,在时序脉冲Vφ1和Vφ3的上升沿感光电荷包从感光阵列全部转移到垂直移位寄存器阵列当中,如图2所示;在Vφ2上升沿到来时,将1、2、3、4…光敏单元列的电荷包合并,经后续脉冲作用存储在Vφ1和Vφ2电极下。如图3所示,当偶数场输出时,同样在Vφ1和Vφ3的上升沿,信号电荷包从光积分区全部转移到垂直移位寄存器当中,在Vφ4上升沿开始时,将2、3、4、5…光敏单元列的信号电荷包合并,经垂直驱动脉冲作用存储在Vφ1和Vφ2电极下。当Vφ1和Vφ3信号处于次高电平状态或低电平状态时,光积分区与垂直移位寄存器处于阻断态,信号电荷包不会发生转移。

1.2.2 感光阶段 在光积分区接受外界光源照射积累电荷的同时,光积分区和垂直移位寄存器之间为阻断态,两者之间不会发生电荷转移现象。如图4所示,当垂直驱动时序脉冲Vφ1,Vφ2,Vφ3,Vφ4完成一个周期变化后,垂直移位寄存器的所有电荷包均下移一行,最下面一行信号电荷包下移到水平移位寄存器 Hφ1电极下,此后Vφ1,Vφ2,Vφ3,Vφ4暂停变化。

图2 奇数场信号电荷包转移时序Fig.2 Charge packet transfer timing of odd field signal

图3 偶数场信号电荷包转移时序Fig.3 Charge packet transfer timing of even field signal

图4 感光阶段垂直驱动脉冲时序Fig.4 Vertical pulse driving time during photostage

此时,在水平时序驱动脉冲 Hφ1,Hφ2,Rg驱动下,水平移位寄存器开始向输出端串行输出信号电荷包。如图5所示,当Hφ1为高电平、Hφ2为低电平时,信号电荷包储存在Hφ1电极下面;当Hφ1为低电平、Hφ2为高电平时,最前端的Hφ1电极下的电荷包输出到Vout端,新的电荷包存储在Hφ2电极下;当Hφ1又变为高电平时,Hφ2的电荷包存储到Hφ1电极下面。此时Rg的高电平脉冲将Vout端的电荷包清除,并准备接受下一个信号电荷包,Vφ1,Vφ2,Vφ3,Vφ4每变化一个周期,Vout端就输出一个电荷包,直到所有的信号电荷全部输出,Hφ1,Hφ2,Rg暂停变化。此后垂直驱动脉冲Vφ1,Vφ2,Vφ3,Vφ4每变化一个周期,信号电荷就向下移动一行,垂直移位寄存器中的像元电荷包可以移到水平模拟移位寄存器当中。如此循环,直到一场信号电荷包全部输出,脉冲信号完成一个工作周期。

2 CCD驱动脉冲时序设计

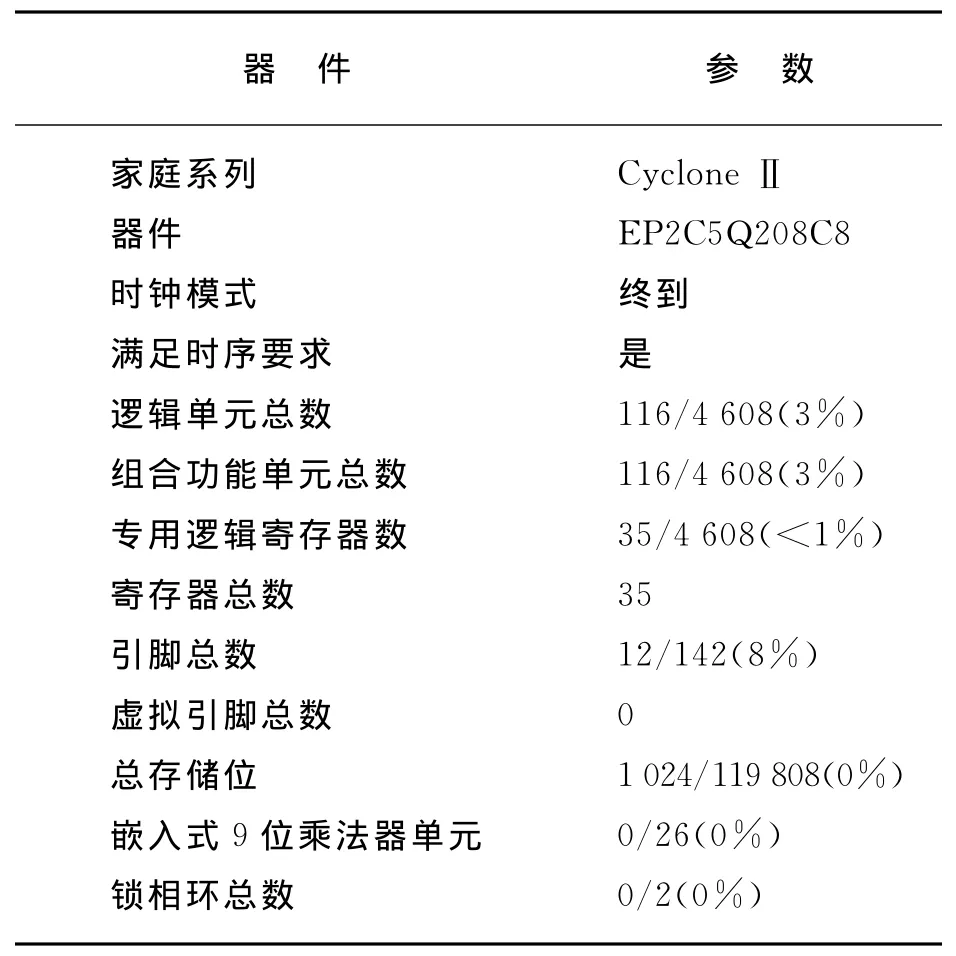

2.1 FPGA器件EP2C5Q208C8

由于本设计需要通过计数以达到各时序的要求,为防止软件计数中出现丢数现象,采用Altera公司FPGA器件EP2C5Q208C8来实现硬件计数。EP2C5Q208C8采用300mm晶圆,以TSMC公司成功的90nm工艺技术为基础,提供了4 608个逻辑单元(Logic Element,LE),并具有一整套最佳的功能,包括嵌入式18bit×18bit乘法器、专用外部存储器接口电路、4Kbit嵌入式存储器块、锁相环(Phase Locked Loop,PLL)和高速差分输入/输出(Input/Output,I/O)能力[13]。灵活多变的行列连线资源可作全局时钟使用,以最大限度地减少时钟到各功能丰富的I/O引脚触发器的延迟,尽量使各时序脉冲同步。

图5 信号电荷包输出期间水平驱动脉冲时序Fig.5 Horizontal pulse driving time during outputting the charge packet

2.2 驱动时序设计

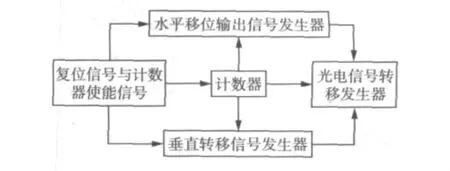

由于面阵CCD驱动时序的复杂性,在Quartus II软件设计环境下,使用Verilog硬件描述语言(Hardware Description Language,HDL)设计CCD驱动时序。为了节省FPGA器件资源,采用多进程描述方式来实现具体的功能,由2个计数器进程计数完成一个工作周期的计数。计数器通过信号向各信号发生模块发出启动命令,这些信号发生模块在规定的时间内产生设计好的信号;当一个信号发生模块工作时,其余几个信号发生模块被冻结;最后将多个信号发生模块所产生的信号进行总和,就得到实际需要的驱动信号,程序的实现框图如图6所示。

设计复杂的CCD驱动时序发生器,关键要用Verilog HDL来描述CCD驱动时序的关系。首先定义驱动时序发生器的输入、输出端,驱动时序发生器共有3个输入端,即时钟输入CLK_100M、复位信号RST、计数器使能端CCD_EN;输出端有9个,分别是 H1,H2,RG,XSG1,XSG2,XV1,XV2,XV3,XV4,如图7所示。

图6 CCD驱动程序结构框图Fig.6 Structure of CCD drivers

图7 CCD驱动时序发生器Fig.7 Driving time generator of CCD

CCD的驱动时序是通过2个计数器循环嵌套来实现的。在一帧图像从曝光到转移的过程中,感光阶段与转移阶段构成了一个外循环计;在一行信号电荷包逐个串行输出的过程中,行信号垂直移位过程与行信号水平输出过程构成一个内循环,2个循环过程通过对输入主时钟CLK_100M进行分频、计数来实现[14]。其中高10位计数器控制外循环,低12位计数器控制内循环,至于感光阶段的垂直移位信号发生器和水平移位输出信号发生器,以及转移阶段的光电信号转移发生器,它们输出信号的时序关系分别由各自的进程来实现。

在外循环中,用高10位计数器计从曝光开始到转移结束时的时钟个数,并通过高10位计数器判断内循环进程的运行情况。在内循环中,通过判断低12位计数器的计数信号实时启动内部进程,低12位计数器计从0开始计垂直转移一行信号电荷所需要的脉冲数量,并启动垂直转移信号进程,信号电荷开始向下垂直转移一行,低12位计数器计数时,信号电荷垂直转移一行完成。结束垂直转移信号进程后,低12位计数器继续计数;当低12位计数器计数到14时,启动水平移位输出信号进程,低12位计数器计数,设定完成一个像元信号输出,消耗4个时钟脉冲的时间;当低12位计数器计数到2 305时,一行信号电荷包全部输出,屏蔽水平移位输出信号进程,此时完成了一个内循环,低12位计数器计数清零,高10位计数器加1。若高10位计数器小于298,又开始下一个内循环计数;若高10位计数器等于298,则低12位计数器计数从0开始计数,并启动光电信号转移进程,信号电荷从光积分区转移到垂直寄存器中,当低12位计数器计数到12时,信号电荷完成光积分区垂直寄存器的转移和信号的合并、高10位计数器和低12位计数器计数清零,准备下一帧图像输出。

3 CCD驱动电路

CCD驱动电路主要由CCD驱动时序发生电路、CCD垂直脉冲驱动电路、CCD水平脉冲驱动电路等部分组成,其中CCD驱动时序发生电路在FPGA器件EP2C5Q208C8中已通过Verilog HDL设计实现。从FPGA中输出的信号为晶体管-晶体管逻辑(Transistor-Transistor Logic,TTL)电平,而CCD垂直驱动脉冲信号Vφ1,Vφ2,Vφ3,Vφ4要求高电平为+15V、次高电平为0V、低电平为-8.5V,故从FPGA输出的信号不能直接加到CCD芯片上。为解决这一问题,选用SONY公司的CXD1267AN作为垂直驱动脉冲驱动器,选用74HC04组成水平脉冲驱动电路。

CCD垂直脉冲驱动电路是CCD连接到FPGA的接口电路之一,如图8所示,由可调电阻R103、零电阻R104和滤波电容C110构建一个电压可调电路,作为衬底电压的可调输入信号源。输出的衬底电压信号VSUB_O通过保护二极管输入给CCD的SUB_V端,C106是滤波电容。当启用CCD电子快门时,快门脉冲XSUB_O叠加在衬底电压上,输入给CCD的SUB_X端,这样,通过CXD1267AN就可以将FPGA产生的垂直驱动脉冲信号的TTL电平转变成CCD正常工作所要求的电压幅值。CCD水平脉冲驱动电路如图9所示。FPGA产生的水平驱动脉冲信号H1,H2,RG接入到2组74HC04中,经2次非门变换之后,得到时序和电平均符合行间转移型面阵CCD器件ICX055AL正常工作所要求的信号。

图8 CCD垂直脉冲驱动电路Fig.8 Vertical pulse driving circuit of CCD

图9 CCD水平脉冲驱动电路Fig.9 Horizontal pulse driving circuit of CCD

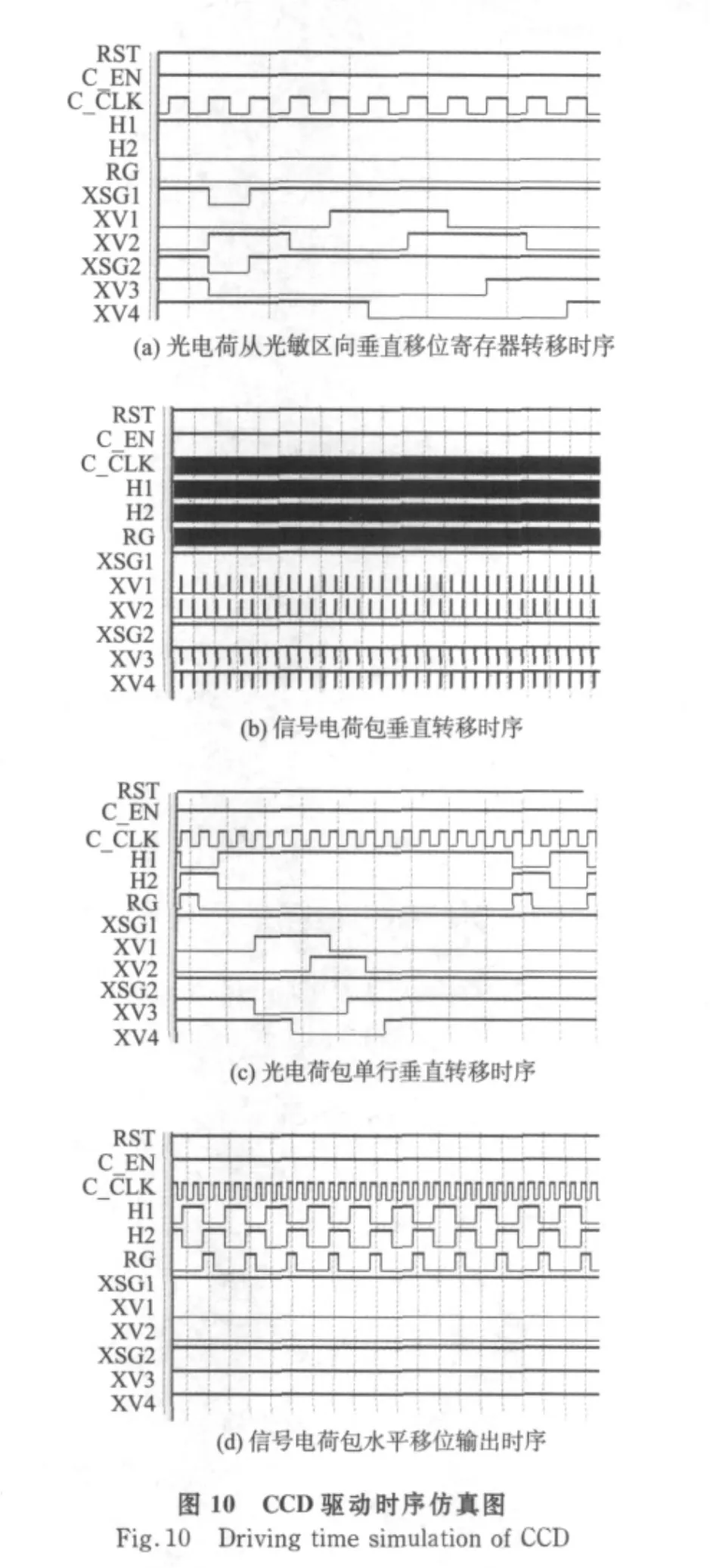

在本系统中,通过可编程逻辑集成开发环境QuartusⅡ对所设计的驱动程序进行了编辑与编译,设置好信号持续时间和主时钟周期,创建仿真波形文件,对系统进行仿真分析,并对EP2C5Q2-08C8进行了配置[15],利用QuartusⅡ编译器对设计项目编译后,器件的资源利用情况如表1所示,仿真波形如图10所示。通过对比行间转移型面阵CCD器件ICX055AL的驱动时序要求,可发现图中所示波形完全可满足ICX055AL正常工作所需要的四相垂直时序驱动脉冲和三相水平时序驱动脉冲的要求,进一步验证了系统的可行性,所设计的基于FPGA的行间转移型面阵CCD驱动电路可用于数码相机、视频捕获设备以及模式识别等领域。

4 结 语

在分析行间转移型CCD器件驱动时序关系的基础上,采用FPGA设计行间转移型CCD的驱动时序发生器,使原来复杂的电路大大简化,只需一片FPGA芯片和简洁的外围驱动电路就可完成,满足了CCD器件在应用上向高速化、小型化、智能化、低功耗化发展的需求,提高了系统的集成度,增强了系统的抗干扰能力,提高了系统的稳定性和可靠性。经实验验证,此CCD的驱动电路满足了ICX055AL的各项驱动性能要求,能够保证其稳定可靠地工作。

表1 EP2C5Q208C8资源利用情况Tab.1 Resource usage of EP2C5Q208C8

[1]Oda E,Nagano K,Tanaka T,et al.A 1920(H)×1035(V)pixel high-definition CCD image sensor[J].IEEE Journal of Solid-State Circuit,1989,24(3):711-717.

[2]Zheng Jinkun,Bai Yonglin,Wang Bo,et al.Highspeed dynamic spectrum data acquisition system based on linear CCD [J].Chinese Optics Letters,2011,9(suppl 1):S10308.

[3]王福斌,刘 杰,代沅兴,等.履带式挖掘机器人CCD道路识别[J].中国工程机械学报,2010,8(2):230-233.

[4]马 骏,李少毅,孙 力,等.CCD驱动电路设计对航空相机图像质量影响分析[J].测控技术,2011,30(3):5-7.

[5]Bogaart E W,Hoekstra W,Peters I M,et al.Very low dark current CCD image sensor[J].IEEE Transactions on Electron Devices,2009,56(11):2462-2467.

[6]陶明慧,张星祥,张 宇,等.KAI-2093型面阵CCD多模式驱动时序设计[J].液晶与显示,2011,26(1):105-110.

[7]李宁宁,李志农,刘治华,等.基于CPLD的线阵CCD驱动电路的设计[J].机械设计与制造,2011(6):30-32.

[8]常丹华,韦 青,尚 进,等.行间转移型面阵CCD图像采集系统的研究[J].电子技术,2009(1):71-73.

[9]刘 燕,高 伟,陈楚君,等.基于FPGA的 TDICCD时序电路设计[J].现代电子技术,2010(4):180-182.

[10]马 骏,黄 勇,孙 力,等.大面阵CCD图像传感器驱动采集系统设计[J].电子测量技术,2007,30(12):158-160.

[11]魏冬冬,王大勇,李彩霞.CCD时序驱动电路的设计[J].传感器与微系统,2011,30(9):112-114.

[12]SONY Corporation.ICX055AL datasheet[EB/OL].[2011-06-25].http://www.datasheet5.com/product_2272594.html/ICX055-Datasheet.pdf.

[13]刘新云.基于EP2C5Q208的最小NiosⅡ开发板设计[J].荆楚理工学院学报,2010,25(5):16-19.

[14]Lu Hong,Tan Liyong,Lei Bo,et al.A kind of linear array CCD drive frequency regulation technology[J].Advanced Materials Research,2010,139-141:2279-2282.

[15]葛亚明,彭永丰,薛 冰,等.零基础学FPGA:基于Altera FPGA器件&Verilog HDL语言[M].北京:机械工业出版社,2010:103-149.

Design of Driving Circuit of Area Array CCD with Interline Transfer Based on FPGA

YANG Kai, LI Zhongshen, LÜ Suying

(College of Mechanical Engineering and Automation,Huaqiao University,Xiamen 361021,China)

The working principle and driving timing of the interline transfer area array charge coupled device(CCD)ICX055AL are analyzed.Field programmable gate array(FPGA)is chosen for the hardware implementation.The driving timing of CCD is described with the hardware description language(HDL)Verilog.By adding a clock driving chip CXD1267AN and two 74HC04chips,the CCD driving circuit is designed.Function simulation and system analysis are carried out with the software Quartus II.The program is then used to configure EP2C5Q208C8.The result shows that the driving circuit design can meet the demands of ICX055AL,and pulse signals are accurately generated to drive ICX055AL.

area array charge coupled device(CCD);ICX055AL;driving circuit;field programmable gate array(FPGA)

TP 342.3

A

2095-0020(2012)01-0038-06

2011-10-20

华侨大学基本科研业务费专项基金项目资助(JB-ZR1107)

杨 凯(1985-),男,硕士生,专业方向为自动化控制,E-mail:yangkai1@hqu.edu.cn

李钟慎(1971-),男,教授,博士,专业方向为时滞系统的控制、最优控制,E-mail:lzscyw@hqu.edu.cn