基于多路数据并行采集架构的数字存储示波卡

冯国楠,张鹏云,和志强

(河北经贸大学信息技术学院,河北石家庄 050061)

基于多路数据并行采集架构的数字存储示波卡

冯国楠,张鹏云,和志强

(河北经贸大学信息技术学院,河北石家庄 050061)

通过深入研究高速数据采集技术原理和实现方法,设计了基于FPGA的4路并行数据采集架构,利用低速、低成本的A/D转换器件实现了400MSa/s高速数据采集的目标,研发的数字存储示波卡具有高速、大容量的数据采集和示波等功能。

数据采集;示波;FPGA

在电子测量领域,数字存储示波器正在逐渐取代模拟示波器。数字存储示波器与模拟示波器最大的不同在于信号进入示波器后立刻通过高速A/D转换器对前端模拟信号快速采样,并存储为数字化信号。数字存储示波器不仅具有体积小、功耗低、使用方便、可存储波形等优点,而且还具有强大的信号实时处理分析功能[1]。数字存储示波器可以利用数字信号处理技术对所存储的数据进行实时快速处理,得到信号的波形及其参数,并由配套软件及设备显示,从而实现示波功能,并且测量精度高,信号还可以存储下来。因而,数字存储示波器具有存储和调用显示特定时刻信号的功能。

笔者设计的数字存储示波卡是一种基于多路数据并行采集架构的虚拟数字存储示波器,它是一种既具有实时观察特性,又具有波形存储能力;既具有信号处理功能又具有电路分析能力;操作简单,精确度高,可以通过计算机进行程序自动测量的高智能化示波仪器。

1 总体设计

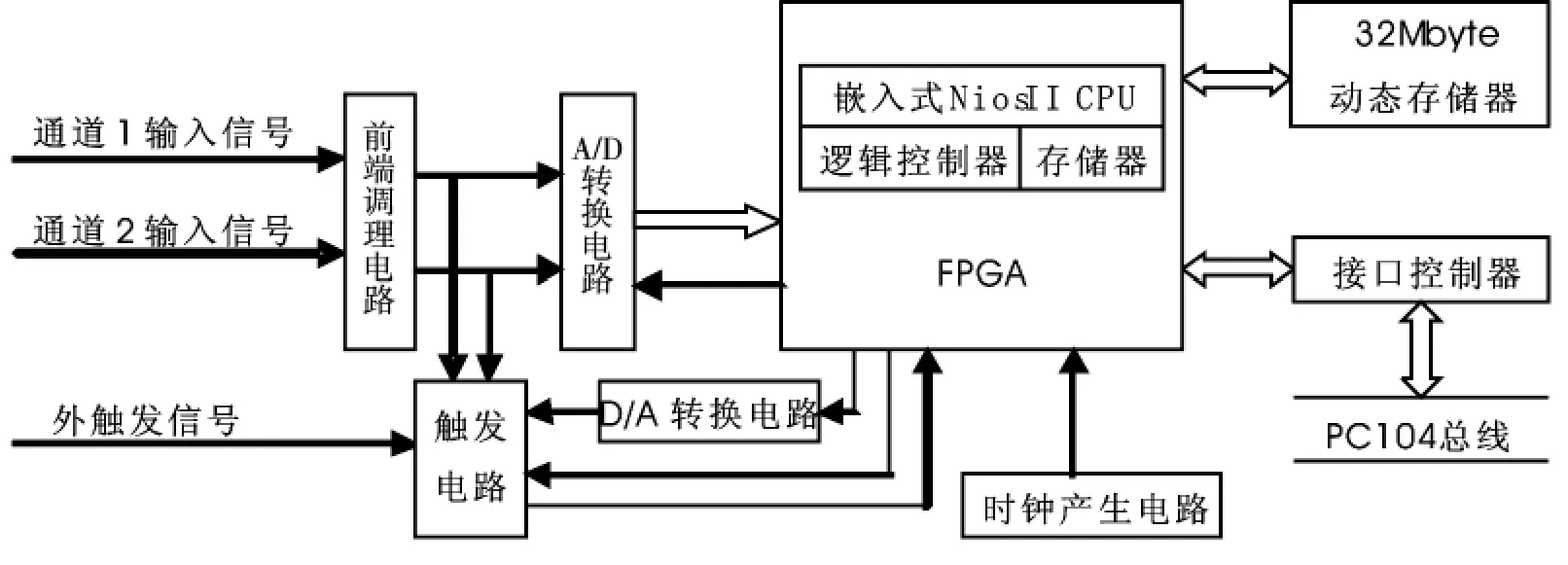

数字存储示波卡的总体结构如图1所示,它由前端调理电路、触发电路、SDRAM存储电路、A/D转换电路、高频时钟及时序产生电路、FPGA芯片、接口控制器等组成,其中,FPGA芯片集成有嵌入式NiosII CPU及逻辑控制器。外界信号经过传感器处理后,通过BCN插座进入示波卡的前端调理电路,前端调理电路对输入信号进行放大或衰减等处理(信号电压过大则衰减,过小则放大),使之适应A/D转换芯片的输入要求,A/D转换电路将信号由模拟量转换成便于计算和存储的数字量。在数据采集模式下,SDRAM控制器将转换后的数字量依次写入SDRAM存储器。在示波模式下,FPGA内部的FIFO负责数字信号的传输工作,数字信号通过PC104总线被上位机载入、处理并显示。接口控制器可以实现完整的PC104接口功能,符合PC104局部总线规范。时钟发生器产生稳定的高频时钟信号,该时钟控制整个示波卡进行有序的工作。

图1 数字存储示波卡总体结构

整个示波卡系统的硬件设计以ADC为界,分为模拟电路和数字电路两部分,前端模拟电路主要是对待测输入信号进行调理,使之便于进行A/D转换和后期的数字处理,而数字部分则是板卡设计的重点,整个数字存储示波卡是一个同步的数据采集系统。数字电路部分主要功能就是对整个板卡进行步调一致的控制,包括对前端模拟通道的控制、继电器的切合、档位的选择、触发信号的控制、内存读写及刷新的控制、A/D转换器的控制、时钟信号的产生以及电源的控制等。

2 前端调理电路

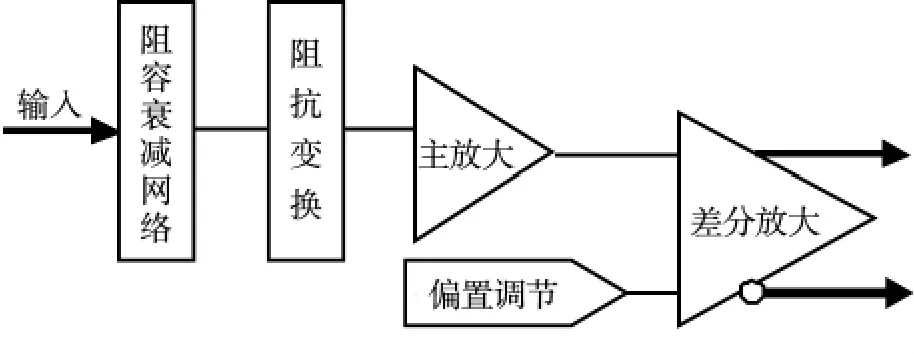

前端调理电路结构如图2所示,在高速数据采集系统中,模数转换器(ADC)的电压输入范围都是有限的,模拟信号过大或过小都不利于ADC的正常工作,信号太大可能会损坏ADC,信号太小则不能充分利用ADC的分辨率,所以在示波卡的模拟前端设计前端调理电路是十分必要的。

前端调理电路能够对输入信号进行调理,使调理后的信号达到模数转换芯片对采样信号的电压要求。设计重点包括从示波卡外部获取信号的能力、对信号范围的适应能力、以及对噪声的抑制等。前端调理电路由衰减网络、阻抗变换、主放大、驱动放大以及偏置调节等组成。

由继电器控制衰减网络,完成10倍或100倍衰减;主放大器选用AD8008,该放大器是一种宽频带运算放大器,具有650MHz带宽,采用负反馈放大方式,与继电器相配合根据需求完成1、2、5倍放大;驱动放大电路采用AD8138,该放大器具有较宽的模拟带宽,而且可以将单端输入信号转换成差分输出信号,这一功能在高速A/D转换电路中具有非常重要的作用,因为几乎所有的高速模数转换芯片的模拟输入端都为差分信号,虽然部分芯片的手册中提到也可使用单端信号,但这样一来会使A/D转换结果的二次谐波增大,降低系统的信噪比(SNR)[2]。AD8138很好地解决了这个问题,不必使用变压器耦合,即可非常容易地将用户端的单端信号转换成差分输出,大大简化了电路结构。偏置调节电平由数模转换器(DAC)输出,并由上位机程控调节。

图2 前端调理电路结构

3 采样电路

3.1 多路拼接采集架构

采样电路采用多路拼接的并行高速数据采集架构如图3所示,利用多个ADC同时对一路模拟输入信号进行采样,最后通过并串转换输出更高速的高精度采样数据。采用这种方案对现有的ADC依赖较小,可满足高速率系统的要求,有利于进一步扩展。

ADC芯片采用AD9288,它的输出完全基于PECL逻辑,两通道输入幅度范围均为1 V峰值,3.0 V单电压供电(2.7 V-3.6 V);输出数据格式为偏移二进制(offset)格式或二进制补码格式,并且功耗低(单通道90m W),体积小(仅为7*7mm)[3],每个通道采用了2片AD9288,每片AD9288含有2个ADC,每个ADC采样率均为100MSa/s,这4个ADC的采样信号相位差均为90°,拼接在一起达到400MSa/s的采样速率。AD9288芯片在数据输出部分采用两个端口乒乓输出的方式,这样每个端口的最大数据传输速率降为100MS/s。在此传输速率下依然可以使用TTL电路来实现对数据的锁存,所以无需再作电平转换即可与后端的存储器接口连接,大大降低了对后续电路的要求。

3.2 模数转换电路实现

本系统采用四片AD9288芯片,每个AD9288芯片都有两路数据采集通道,每个数据采集通道的采样率均为100MSa/s的,采用并行时间交替型数据采集架构,能够实现双信道各自最大400MSa/s的采样电路。

每片AD9288内部包含A、B两个A/D转换器,可以单独进行模数转换工作,也可以同时进行模数转换工作。片上通过数字信号EN1和EN2的电平高低来选择工作模式。

EN1和EN2由FPGA内部数字逻辑控制输出的采集使能信号控制。EN1=EN2=0,则两路都不工作;EN1=0、EN2=1或EN1=1、EN2=0,则只有一路工作;EN1=EN2=1,则两路模数转换器同时采集,数据交叉并行输出,由时钟信号控制,最高采样率可达200MS/s。电路中原始时钟由FPGA内部锁相环倍频处理后,输出时钟再移相得到Clk0和Clk1提供给两路模数转换器。AD9288内部分别为两路模数转换器提供参考电压输入端REFA和REFB,参考电压输出端REFO。实际电路中,将电压输入端和电压输出端相连接,可以节省高精度基准电压,这里为模数转换器提供1.25V的基准电压。AD9288满量程输入电压范围为1.024V,输出数据位宽为8bit,故其最小电压分辨率为:

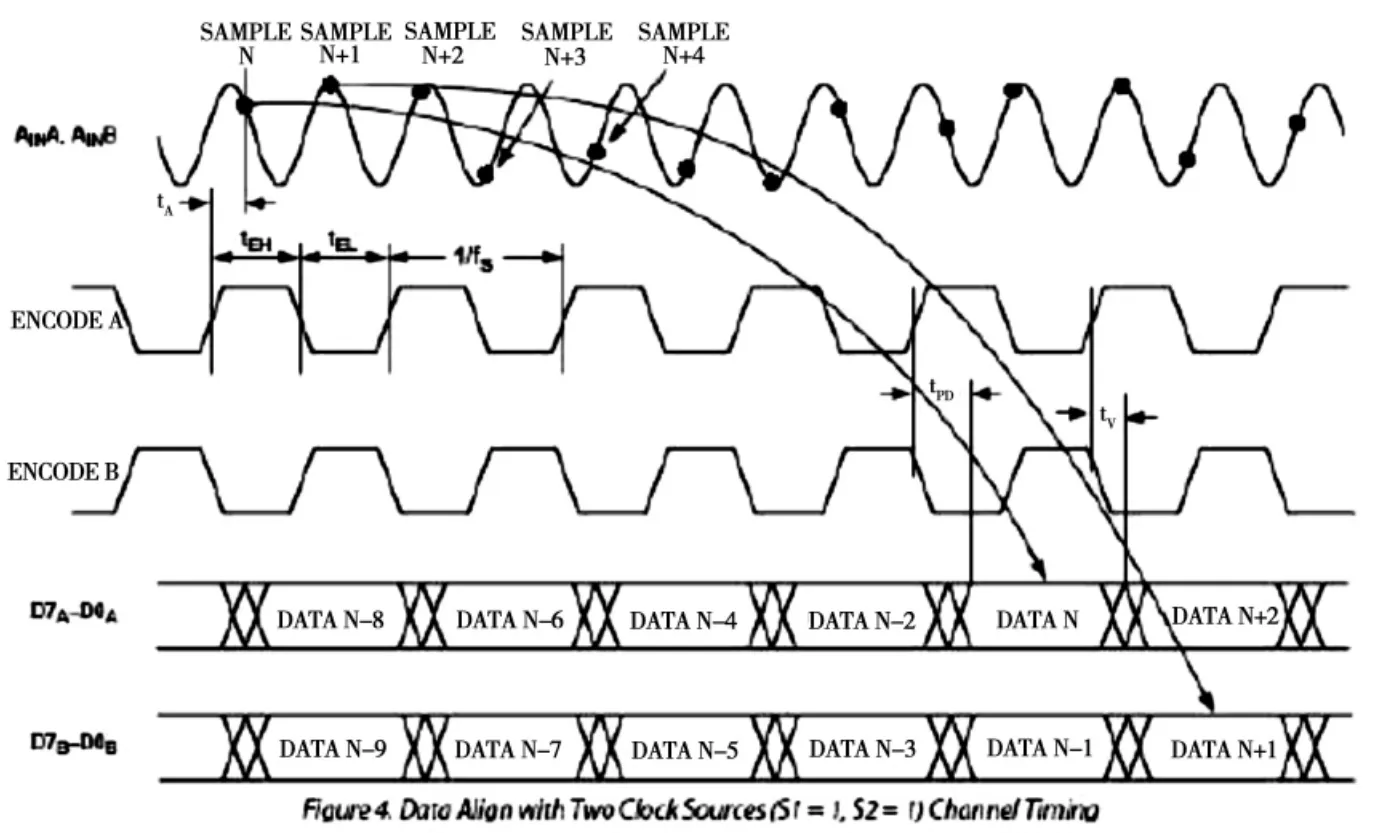

AD9288分相数据采集、数据交叉输出模式的工作时序如图4所示。

数据输出部分选用A、B两个端口进行输出的方式,每个端口的最大数据传输速率为100MS/s。要将4路如此高速的数据准确无误的锁存下来,用常规的办法还是相当复杂的,拼接的通道数越多,电路就越庞大,各通道时钟与数据之间的关系也就越复杂,综合考虑,这里采取了FPGA来锁存。

图3 并行高速数据采集架构

4 供电电路

数据采集部分的电源主要分两部分,一部分给高速A/D转换器供电,另一部分给FPGA供电。本数字存储示波卡系统考虑到成本和实用性等因素,使用比较常见的可调电源LM1117为系统供电。A/D转换器需要的额定供电电压是+3.3V,单片A/D转换器在正常工作的情况下的功率是689m W,故耗费的电流在210m A左右,LM1117的额定供电电流800m A,使用两片可较好满足要求。FPGA供电分为内核供电和IO端口供电。内核供电电压为1.2V,由LM1117供电;IO端口可以进行包括1.5V、1.8V、2.5V、3.0V和3.3V等多种配置其电源也同样由LM1117来提供。示波卡的运算放大器和场效应管等器件所需的负电压由LM2991来提供。LM2991是输出可调低压差稳压器,输出电压调节范围为-2V至-25V(输出电流为1A)[4]。

图4 A/D采样时序图

5 结语

本文针对基于多路并行采集架构的数字存储示波卡的设计展开了研究,通过深入探讨高速数据采集方法和实现机理,提出了基于FPGA的4路并行采集架构,用低速(单路最高100MSa/s)、低成本的A/D转换器件实现了400MSa/s采样率的高速数据采集目标。实际测试表明,基于多路并行采集架构的数字存储示波卡通用性强、成本低、速度快,可广泛用于高速、大容量数据采集、示波的场合。

[1]郭小虎,陈鹏鹏.基于单片机和FPGA的简易数字存储示波器设计[J].国外电子元器件,2008,(06):39-42.

[2]张梦麟.基于Lab Windows/CVI网络虚拟仪器实验室的构建[D].济南:济南大学,2008.

[3]Analog Inc.AD9288芯片参数的电子文献.pdf[EB/OL].http://www.analog.com.

[4]National Semiconductor Inc.LM2991芯片参数的电子文献[EB/OL].http://www.national.com/ds/LM/LM2991.pdf.

The digital storage oscilloscope card based on parallel multi-channel data acquisition architecture

FENG Guo-nan,ZHANG Peng-yun,HE Zhi-qiang

(CollegeofInformationTechnology,HebeiUniversityofEconomicsandBusiness,ShijiazhuangHebei050061,China)

The high-speed data acquisition technology and method are deeply reseacged.The 4-channel parallel data acquisition architecture is proposed based on VHDL.The low-speed,low-cost analog/digital conversion devices are adopted to realized the 400MSa/s high-speed data acquisition.The designed digital storage oscilloscope card has shown high-speed,large capacity data acquisition and oscilloscope functions.

Data acquisition;Oscilloscope;FPGA

TP334

:A

1001-9383(2011)03-0048-04

2011-06-30

河北省应用基础研究计划项目(10963529D)、河北省高等学校科学技术研究项目(ZD2010213)

冯国楠(1985-),男,硕士研究生,主要研究方向:高速数据采集.