一种基于FPGA实现的改进语音端点检测算法

欧阳玲,宋 克

(1.中原工学院,郑州 450007;2.国家数字交换系统工程技术研究中心,郑州450002)

一种基于FPGA实现的改进语音端点检测算法

欧阳玲1,宋 克2

(1.中原工学院,郑州 450007;2.国家数字交换系统工程技术研究中心,郑州450002)

介绍了一种基于FPGA硬件实现的语音端点检测算法,该算法以短时平均能量和短时平均过零率为基础,具有硬件实现简单、资源占用量低、检测效果良好等特点;给出了算法的流程与硬件实现模块,以及采用FPGA综合和仿真的结果.

FPGA;语音端点检测;短时平均能量;短时平均过零

在语音信号系统中,数字语音信号是由语音、静音和各种背景噪音混合组成的.在这种信号中将语音和各种非语音信号时段区分开来,准确地确定出语音信号的起止点,被称为端点检测.语音信号的端点检测在语音信号处理中非常重要.实验表明,端点检测是否准确对语音信号的识别率具有非常重要的影响;另外,准确地检测出语音信号的端点还可以减少后续处理的计算量,提高芯片的处理能力.

端点检测的算法很多,如基于自相关极大值、基于小波变换、基于频带方差、基于倒谱特征、基于信息熵、基于 HMM等等端点检测算法[1],然而这些算法由于算法复杂、计算量大、实时性差,很难应用于ASIC硬件实现.本文介绍一种改进的基于短时平均能量和短时平均过零率的端点检测算法,并将其在ASIC上实现,性能良好.

1 算法描述

基于短时平均能量和短时平均过零率的端点检测算法是一种基于时域的语音端点检测方法.其基本思想是采用测试信号的短时能量或短时对数能量、联合过零率等特征参数及双门限判定法来检测语音端点[2],即利用过零率检测清音,用短时能量检测浊音,两者相配合.首先为短时能量确定2个门限[3]:一个是较低的门限,数值较小,对信号的变化比较敏感,短时能量比较容易超过该门限,但当短时能量超过低门限时,测试信号未必是语音的开始,有可能是很短的噪声引起的,这时需要配合过零率来判断是否是语音帧;另一个是比较高的门限,数值较大,当短时能量超过高门限时,则直接判定语音信号为语音帧.

整个端点检测可分为4段:静音段、过渡段、语音段、结束.在静音段,如果短时能量超过低门限且过零率超过门限值,或者短时能量超过高门限,就开始标记起始点,进入过渡段;在过渡段,如果连续3帧语音被判定为语言帧,即认为进入语音段,否则,将当前状态恢复到静音段;在语音段,如果短时能量超过低门限但过零率未超过门限值,或者短时能量低于低门限,就开始进入过渡段,如果连续3帧语音被判定为静音帧,即认为语音结束,否则,将当前状态恢复到语音段,继续检测下一帧语音数据.

2 算法实现与流程

定义帧平均幅度(短时能量):

为第n帧语音信号的平均幅度;n为帧的编号;N为每帧的点数.

定义帧语言信号的短时平均过零率:

Zj为帧语音信号的短时平均过零率.

首先,为帧平均幅度确定2个门限:一个是较低的门限(AL),数值较小,对信号的变化比较敏感,很容易被超过;另一个是比较高的门限,数值较大(AH).当帧平均幅度超过低门限时,进行过零率检测,超过高门限时直接判定为语言帧.

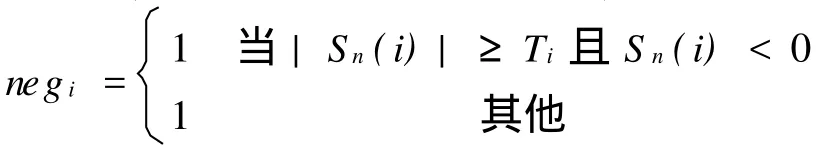

其次,定义3个短时平均过零率门限T1、T2、T3,T1 只要门限值T1、T2、T3和权值w1、w2、w3选得合适,语音帧信号的Z值明显大于静音帧的Z值.通过试验找出一个分界值Z0,当Z>Z0时,判定该帧为语音帧;当Z 算法实现框图和流程图分别如图1和图2所示. 其中:SS=0,表示静音;SS=1,表示语音;VN为连续检测记录是语音的帧数;VS为连续检测记录是非语音的帧数. 图1 算法实现框图 图2 算法实现流程图 本设计的输入为每帧256点16位的有符号语音数据,分别计算每帧语音数据的平均幅度(为简便起见,这里采用幅值和代替)和帧短时平均过零率.然后根据计算结果和设定的各门限值按照一定的规则进行判决,输出每帧语音信号的检测结果(静音或语音).硬件结构框图如图3所示: 图3 FPGA硬件结构图 当VAD使能信号有效时,计数获取每帧256点语音数据,计算每点语音数据的幅值(绝对值),并进行累加.当每帧256点数据处理完成,产生该帧幅值后,送给VSJ模块并置位ARC完成信号. 输入信号:Data(0:15)(16位语音信号);Start(VAD使能信号);CLK100M(工作时钟);RESET(复位信号). 输出信号:A(帧幅度值);ARCVCO_En(ARC完成信号,当该信号为1时,使能下一级操作). 当VAD使能信号有效时,计数获取每帧256点语音数据,计算过零率Z(Z=w1×Z1+w2×Z2+w3×Z3).当每帧256点数据处理完成,产生该帧过零率后,送给VSJ模块并置位ZCN完成信号. 输入信号:Data(0:15)(16位语音信号);Start(VAD使能信号);CL K100M(工作时钟);RESET(复位信号);T1、T2、T3、w1、w2、w3(16位门限值). 输出信号:Z(过零率);ZCNVCO_En(ZCN完成信号,使能下一级操作).该模块流程如图4所示. 图4 ZCN模块算法流程图 将ARC和ZCN模块输出的帧数据处理完成的信号进行与操作,生成VSJ模块使能信号,然后进行判决. 输入信号:ARCVCO_En(ARC完成信号,使能下一级操作);ZCNVCO_En(ZCN完成信号,使能下一级操作). 输出信号:VCOVSJ_En(VSJ使能信号). 读取每帧语音数据幅值和过零率,判断该帧是否为语音,并根据最近3帧的判决结果输出语音/静音判决信号及VAD帧处理完成信号. 输入信号:A(帧幅度值);Z(过零率);AL、A H、Z0(32/16位门限值);VCOVSJ_En(VSL使能信号);CL K100M(工作时钟);RESET(复位信号). 输出信号:VADHAM_Voice(有无语音标志,VADHAM_Voice=1,表示有语音;VADHAM_Voice=0,表示静音);VADHAM_FraEnd(VAD帧判决完成信号). 该模块流程如图5所示. 图5 VSJ模块算法流程图 采用Xinlix公司的Virtex-5系列FPGA对本算法的设计实现进行综合,综合工具为ISE10.1.03,得到的结果如表1所示. 表1 FPGA硬件资源占用率 由表1可以看出,本算法的设计在硬件上占用的资源较少,因此可以很容易地与其他数字语音处理模块一起构成完整的语音处理芯片. 为验证本算法的检测结果,特选取如下一段实际语音进行仿真测试,其中标记部分为有话帧(18帧到28帧),其余均为噪声,如图6所示. 图6 实际语音波形图 仿真结果如图7所示,其中检测为有话帧是19帧到29帧,其余为无话帧. 图7 语音端点检测仿真波形图 本文介绍了一种基于短时平均能量和短时平均过零率的端点检测算法的硬件实现方法. 通过仿真,可以看出该设计可以较好地实现话音信号中的噪音分辨,能够作为预处理部分的端点检测模块,应用于各种语音处理芯片的设计. [1]王炳锡,屈丹,彭煊.实用语音识别基础[M].北京:国防工业出版社,2005:265-269. [2]李祖鹏,姚佩阳.一种语音段起止点端点检测新方法[J].电讯技术,2000(3):68-71. [3]徐大为,吴边,赵建伟,等.一种噪声环境下的实时语音端点检测算法[J].计算机工程与应用,2003(1):115-117. A Improved Algorithm of VAD Based on FPGA Realizing OU YANG ling,SONG Ke This paper introduces a kind of Voice Activity Detection(VAD)algo rithm based on FPGA realizing.The algorithm that based on short-term average energy and short-time average zero-crossing rate,has the virtuesof simp le hardware imp lementation,low resources use and good detection effect.The algorithm p rocess and the realization of hardwaremodulesand FPGA comp rehensive and simulation resultsare given in the paper. FPGA;VAD;sho rt-term average energy;sho rt-time average zero-crossing rate TN912 A 10.3969/j.issn.1671-6906.2011.01.019 1671-6906(2011)01-0070-04 2011-01-20 欧阳玲(1978-),女,安徽池州人,讲师,硕士.

3 算法硬件实现模块

3.1 幅值计算模块ARC

3.2 过零率计算模块ZCN

3.3 控制信号模块VCO

3.4 语音/静音判决模块VSJ

4 FPGA综合与仿真结果

5 结 语

(1.Zhongyuan University of Technology,Zhengzhou 450007;2.China National Digital Sw itching System Engineering&Technology R&D Center,Zhengzhou 450002,china)