用于SVC数控系统的数字锁相环的设计与实现①

张志文, 郭 斌, 罗隆福, 曾志兵, 王 伟

(湖南大学电气与信息工程学院, 长沙 410082)

用于SVC数控系统的数字锁相环的设计与实现①

张志文, 郭 斌, 罗隆福, 曾志兵, 王 伟

(湖南大学电气与信息工程学院, 长沙 410082)

为减少在静止无功补偿(SVC)装置中晶闸管的触发误差,设计了一种基于FPGA(现场可编程门阵列)的全数字锁相环(ADPLL),并进行硬件电路测试。同时分析了全数字锁相环的各模块工作原理并进行了参数设计和电路仿真。最后在实验平台上进行了测试。结果显示,该环路可稳定跟踪电网信号,可为SVC数字控制系统提供快速、稳定、高精度的同步信号。

全数字锁相环; 静止无功补偿装置; 触发误差; 现场可编程门阵列; 同步信号

静止型无功功率补偿SVC(static var compensation)从20世纪70年代初开始发展起来,是一种提高系统电压稳定性,抑制冲击负荷所造成的电压波动的先进技术,在全世界输配电系统得到了广泛的应用[1]。一般由晶闸管控制电抗器TCR(thyristor control reactor)和晶闸管投切电容器TSC(thyristor switch capacitor)组成。其动态补偿容量由晶闸管的触发角α决定,而触发角α又是从晶闸管开始承受阳极电压起到施加触发脉冲止的电角度[2],要减小晶闸管的触发误差,就必须有晶闸管开始承受阳极电压时的准确时刻,即电压信号的过零时刻,如何为SVC装置中晶闸管的触发角α提供精确的过零时刻信号——同步信号成为本文研究的出发点。

传统的SVC控制系统一般都不考虑跟踪电网信号频率波动来调整发出的同步信号,即使考虑也大多数用精度低的模拟锁相环实现。由于模拟锁相环具有直流零点漂移、器件饱和及易受电源和环境温度变化等缺点[3],限制了其发展的前景。

因此,本文将采用数字锁相环来提供同步信号。相对于模拟锁相环,数字锁相环不仅克服了模拟锁相环的缺点而且还有可靠性高、精度高、体积小、价格低等优点,使得其在电力系统自动化、数字通讯及无线电电子学等领域得到了广泛应用。其主要功能有时钟倍频和分频、频率跟踪合成、调制解调等。

由于FPGA与硬件描述语言HDL(hardware description language)的简洁、可靠和可实现性等特点,全数字锁相环电路采用模块化设计,因此本文基于FPGA及其开发软件QUARTUSⅡ,并用高速集成电路硬件描述语言VHDL(very-high-speed integrated circuit hardware description language)设计了一种用于SVC的数字控制系统中的全数字锁相环,作为同步脉冲发生模块。

1 全数字锁相环路原理构成

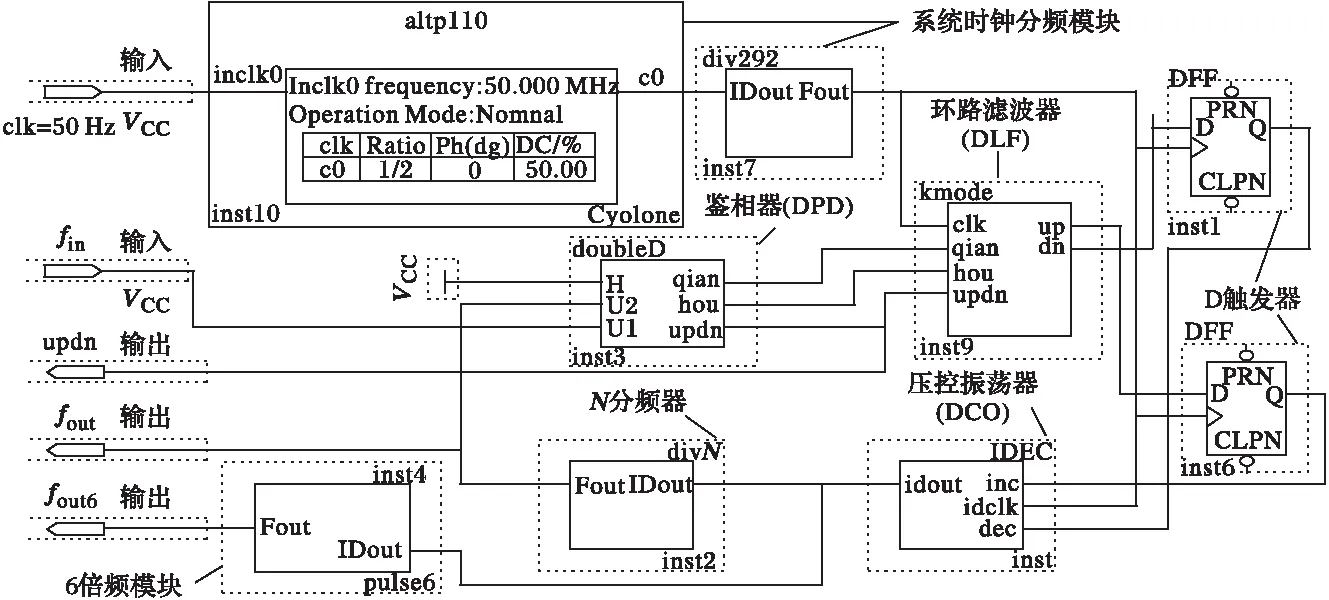

全数字锁相环路指所有部件全数字化实现,一般包括数字鉴相器DPD(digital phase detector)、数字环路滤波器DLF(digital loop filter)、数字压控振荡器DCO(digital voltage controlled oscillator)和除N计数器。而实验输入信号为电网信号,在接入FPGA前要对其进行整形,故加入过零检测电路。因此,整个设计由5部分组成。

如图1所示,输入的电网信号fs信号经过过零检测电路变成方波信号fin,再与同步倍频信号经过分频器N倍分频后产生的锁相信号fout进行鉴相处理,输出相位误差信号。数字环路滤波模块(DLF)具有低通特性,它将相位误差信号转化为稳定的控制信号,从而控制数字可控振荡器模块(DCO),产生稳定的频率信号输出,这个频率信号就是所需的同步倍频信号。如果整个反馈环路锁相稳定,锁相环输出的同步倍频信号的频率就是其输入信号fin频率的N倍。假如fin在输入鉴相模块之前又先被分频了L倍,则锁相获得的同步倍频信号的频率就是fin频率的N/L倍[4]。

图1 数字锁相环原理

2 数字锁相环的设计

由上述原理出发,对数字鉴相器、数字环路滤波器、数字压控振荡器和N分频器进行模块化设计,运用VHDL语言描述各模块硬件功能,再把各个模块链接构成锁相环系统。该全数字锁相环应用于低频信号中,追踪速度比较慢,时钟抖动比较明显,因此在设计的时候要充分考虑这些问题[5]。

2.1 过零检测电路

过零检测电路主要作用是把从电网接入的f=50 Hz,U=220 V正弦信号经过过零检测电路变成FPGA引脚可接受的方波信号。

图2中,电阻R1、R2用于分压;功放J1用于过零比较;光耦TLP521-1模块用于隔离;74HC14P模块用于信号边沿整形,使输出接近理想方波。工作原理是在输入信号的正半周波时,功放模块进行比较,输出为高,光耦发亮产生有效信号,fin输出为高;在负半周波时,功放输出为低,光耦不发光,fin输出为低,最终形成幅值是3.3 V的fin方波。

图2 过零检测电路

2.2 数字鉴相器

数字鉴相器一般有异或门鉴相器和边沿触发型鉴相器,本文采用双D型边沿鉴相器[6]。图3中,fin是输入信号,fout是锁相信号,qian和hou分别是超前和滞后信号,updn是相位误差信号,其高电平宽度反映相位误差大小。其工作原理:当锁相信号fout超前于输入信号fin时,qian信号(高电平)有效,同时相位误差信号updn输出;反之如果锁相信号fout滞后于输入信号fin时,hou信号(高电平)有效,同时相位误差信号updn输出。

图3 双D数字鉴相器

2.3 数字环路滤波器

数字环路滤波器是数字锁相环的重要组成部分,它直接影响数字锁相环路的跟踪捕获速度与跟踪的稳定性[7]。对于其模值选择要适当,模值太大延长锁相时间,模值太小滤波效果不好。

本模块采用随机徘徊滤波器实现,实质相当于一个K变模可逆计数器,模值K由a、b、c、d四个置数端定。该模块具体工作原理:当锁相信号fout超前于输入信号fin时,来自于DPD的qian和updn有效信号,使DLF由预设模值K开始减计数,当计数值达到0时,计数溢出,减脉冲控制信号dn输出;反之当锁相信号fout滞后于输入信号fin时,来自于DPD的hou和updn有效信号,使DLF由0开始加计数,当计数值达到预设模值K时,计数溢出,加脉冲控制信号up输出。部分源代码如下,实现可逆计数器功能。

process(clk,updn,cq,w,qian,hou)

begin

if(clk'event and clk='1') then

w<=m;

if(updn='1') then

if(hou='1' and qian='0') then

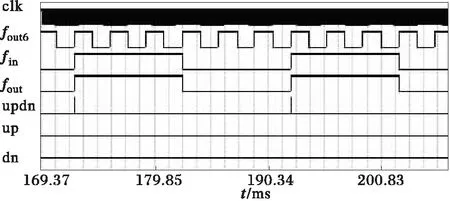

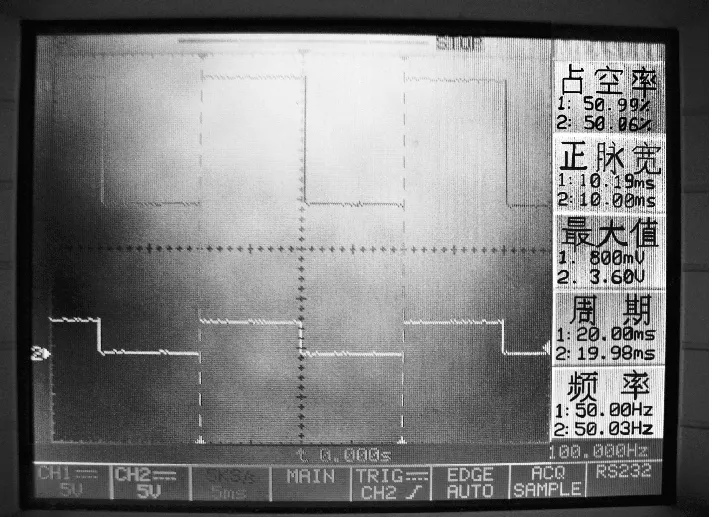

if(cq cq<=cq+1; else cq<=(others=>'0'); end if; elsif(hou='0' and qian='1')then if(cq>0) then cq<=cq-1; else cq<=w; end if; else cq<=cq; end if; else cq<=cq; end if; end if; end process 2.4 数控振荡器 数控振荡器的设计采用脉冲加减式,利用QUARTUS Ⅱ中宏功能模块74297构造。其主要负责相位调整,具体工作原理是在锁相信号fout超前于输入信号fin时,dn脉冲控制的结果,使本地高速时钟序列中的某一个(或几个)脉冲被扣除,被扣除一个(或几个)脉冲的受控本地高速时钟序列经除N分频后,得到相位推后了的锁相信号fout;在锁相信号fout滞后于输入信号fin时,up脉冲控制的结果是在本地高速时钟序列中的塞入一个(或几个)脉冲,经除N分频后,得到相位提前了的锁相信号fout;如果DLF既没有up脉冲又没有dn脉冲控制信号输出,则,DCO输出对本地高速时钟2分频的信号。 2.5 除N计数器 除N计数器是一个简单的分频器,用VHDL语言可方便描述。除N计数器对DCO的输出信号进行N分频,得到整个环路的锁相信号fout。因为fout=clk/2N=fc,所以通过改变分频值N可以得到不同的环路中心频率fc。此外,模值N必须取2的整数次幂。 2.6 数字锁相环各模块链接图 图4中,鉴相器、环路滤波器、压控振荡器及N分频器四个模块构成了全数字锁相环路的总体框架。此外附加模块有系统时钟分频模块、两个D触发器和6倍频模块。其中系统时钟分频模块由FPGA内部锁相环PLL(phase locked loop)和H分频器组成,FPGA内部PLL的作用是对固定频率进行分频,倍频,这里主要是对50 MHz的系统时钟进行分频;另一块H分频器也起分频作用,由于内部PLL的分频系数有一定范围,不足以满足分频要求,故由这两部分完成;两个D触发器的作用是滤除来自于DLF输出的毛刺信号,利用了D触发器对毛刺信号不敏感的特性;6倍频模块的的作用是对输入的电网信号进行6倍频。 图4 ADPLL各模块链接关系 在QUARTUS Ⅱ软件上进行仿真:a、b、c、d是数字滤波器模值K置数端;clk是系统时钟信号,fin是经过零检测电路进来的输入信号;fout是锁相信号;fout6是对输入信号进行6倍频的输出信号;updn是鉴相器输出的相位误差信号;up、dn是送入DCO的控制信号,前者加脉冲信号,后者减脉冲信号;仿真时,H置高。整个仿真时间设置为1 s,为了加快仿真速度,除去图4中系统时钟分频模块,仿真时直接取系统时钟clk=0.051 2 MHz,DLF的模值K取为2,N分频器分频系数N=512,因此可得中心频率 如图5所示,在动态跟踪区域由updn信号的宽度看出锁相信号fout相位大大超前于输入信号fin,此时系统不断地发出减脉冲信号dn,进行相位调整。几个周期后,相位同步。 图5 环路跟踪锁定仿真 在相位同步后,updn信号仍有相差输出,但up和dn信号不在发出控制信号,这是由于此时的相位误差不足以使DLF计数溢出,发出相位控制信号。其最小相位误差由环路滤波器模值K及本地系统时钟clk决定,相位误差近似计算式 K×1/clk=2×1/0.0512=39.06μs 图6是图5相位同步后的局部放大图。 图6 6倍频信号与输入信号相位关系图 从软件仿真上,可以看到所设计的的锁相环路功能已经实现,为了验证其在实际中是否可以正常工作,在实验平台上进行了测试,并在示波器上拍摄下实验波形。由于电网频率比较稳定,波动较小,在截屏拍照时,显示的电网频率基本都是50 Hz,实际上电网频率应该有微小变化。 图7中,频率绝对误差为 图7 输入信号与锁相信号波形 图8 输入信号与6倍频信号波形 50.03-50=0.03 Hz 相对误差为 (50.03-50)/50=0.06% 图8中,频率绝对误差为 302.5-300=2.5 Hz 相对误差为 (302.5-300)/300=0.83% 由以上计算可看出该ADPLL误差率较小。 本文从静止无功补偿(SVC)装置中晶闸管存在触发误差的问题出发,提出了一种用全数字锁相环设计的为触发脉冲提供同步信号的模块,能够方便地与SVC控制系统中的其他模块进行连接。从电路仿真和在实验平台的测试数据可以看到本设计基本实现功能要求,可为SVC数字控制系统提供快速、稳定、高精度的同步信号。 [1] 王智(Wang Zhi).静止无功补偿装置数字控制系统的研究(Research on Digital Control System for Static VAR Compensation)[D].武汉:武汉科技大学信息科学与工程学院(Wuhan: College of Information Science and Engineering, Wuhan University of Science and Technology),2005. [2] 王兆安,黄俊.电力电子技术[M].北京:机械工业出版社,2000. [3] 沈军,郭勇,李志鹏(Sheng Jun,Guo Yong,Li Zhipeng).基于FPGA的DPLL设计与仿真实现(Design and analyze digital PLL on FPGA)[J].微计算机信息(Control & Automation),2007,23(5-2):201-203. [4] 庞浩,俎云霄,王赞基(Pang Hao,Zu Yunxiao, Wang Zanji).一种新型的全数字锁相环(A new design of all digital phased-locked loop)[J].中国电机工程学报(Proceedings of the CSEE),2003,23(2):37-41,131. [5] 张玉梅,杨玉珍(Zhang Yumei,Yang Yuzhen).数字锁相环在低频相位同步控制中的应用(Application of digital PLL circuit in synchronous control of low frequency)[J].仪器仪表学报(Chinese Journal of Scientific Instrument),2004,25(4S):896-898,905. [6] 胡华春,石玉.数字锁相环路原理与应用[M].上海:上海科学技术出版社,1990. [7] 赵杨,王龙,赵群,等(Zhao Yang,Wang Long,Zhao Qun,etal).基于FPGA的全数字锁相环设计研究(Research of digital phase locked loop based on FPGA)[J].光电技术应用(Electro-Optic Technology Application),2007,22(6):63-66. [8] 吕干云,丁屹峰,程浩忠(Lü Ganyun,Ding Yifeng,Cheng Haozhong).一种基于改进锁相环系统的电能质量扰动检测方法(Detection method of power quality disturbance based on an improved PLL system)[J].电力系统及其自动化学报(Proceedings of the CSU-EPSA),2004,16(5):20-25,46. DesignandRealizationofDigitalPhaseLockedLoopforControlSystemofSVC ZHANG Zhi-wen, GUO Bin, LUO Long-fu, ZENG Zhi-bing, WANG Wei (College of Electrical and Information Engineering, Hunan University, Changsha 410082, China) In order to reduce the thyristor triggering error in the static var compensator (SVC),all digital phase-locked loop(ADPLL) is designed based on field programmable gate array(FPGA). Principle of each module is analyzed ,and the parameter design and the circuit simulation are completed.Finally, it is tested on experimental platform .The result shows that the ADPLL can stably track power network signal.It provides fast, stable and accurate synchronized signal for the SVC numerical control system. all digital phase locked loop(ADPLL); static var compensator (SVC); triggering error; field programmable gate array (FPGA); synchronized signal 2009-06-23 2009-09-11 TN742 A 1003-8930(2010)05-0103-05 张志文(1963-),男,博士,教授,硕士生导师,研究方向为电气装备自动化与新技术、电气化铁道谐波抑制等。Email:hdzzw@126.com 郭 斌(1984-),男,硕士研究生,研究方向为交直流电能变换技术与装备、电力电子与电力传动等。Email:gaocaisheng2008@126.com 罗隆福(1962-),男,教授,博士生导师,中国电机工程学会高级会员,研究方向为现代电器设备的设计和优化等。Email:llf@hnu.cn

3 锁相环路仿真

4 实验波形

5 结语