基于工具软件的直接数字频率合成器设计方法

卢一喆,蒙美海,张 峰,张 珂

(1.机电动态控制重点实验室,陕西 西安 710065;2.西安机电信息研究所,陕西 西安 710065)

0 引言

目前频率合成的基本方法主要有以下三种:直接频率合成(DS)、锁相环合成(IS)和直接数字频率合成(DDS)[1]。直接频率合成法输出频谱纯度差、芯片体积大、功耗大,目前已基本不被采用。锁相环合成法使用较广泛,但存在高分辨率与转换速度之间的矛盾,一般只能用于大步进频率合成技术中[2]。而直接数字合成法是采用数字技术的一种新型频率合成方法,该方法的优点是频率分辨率高、频率转换时间快、在频率改变时能够保持相位的连续,很容易实现频率、相位和幅度间的数控调制[3]。直接数字频率合成法一般采用专用芯片或可编程逻辑芯片来实现,专用的芯片产生的信号波形和控制方式比较固定,不便于修改,采用可编程逻辑芯片设计DDS的方法是采用硬件描述语言输入与原理图相结合的方法来设计,但此方法需要编制大量VDHL源程序较为复杂,对设计者的硬件基础要求较高,综合性强。且输出信号不便灵活修改,不能满足具体多变的工程需求。针对上述问题,本文提出了一种基于DSP Buil der软件采用现场可编程门阵列FPGA开发DDS系统的设计方法。

1 DDS的工作原理及实现方法

1.1 DDS工作原理

直接数字频率合成(DDS)是采用数字化技术,通过控制频率和相位的变化速度,直接产生各种不同频率信号的一种频率合成方法。DDS的理论基础是Shannon抽样定理,内容是:当抽样频率大于等于模拟信号频率的2倍时,可以由抽样得到的离散信号无失真地恢复原始信号。在DDS中,这个过程被颠倒过来了。DDS不是对一个模拟信号进行抽样,而是一个假定抽样过程已经发生且抽样的值已经量化完成,通过映射把已经量化的数值送到D/A及后级的LPF重建原始的信号。

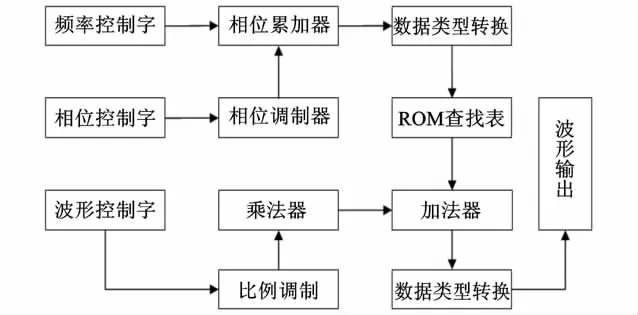

DDS的结构原理图如图1所示,DDS以数控振荡器的方式,产生频率、相位和幅度可控的正弦波。其中包括了相位累加器、正弦ROM查找表、参考时钟、D/A转换器、LDF低通滤波器等组成。

图1 DDS原理框图Fig.1 DDS schematic diagram

DDS的输出频率f0、参考时钟频率fc、相位累加器长度N以及频率控制字K之间的关系为:f0=K×fc2N,DDS的频率分辨率为:Δf0=fc/2N,由于DDS的最大输出频率受奈奎斯特抽样定理限制,所以fmax=fc/2。

1.2 硬件描述语言设计DDS的方法及流程

使用硬件描述语言V HDL或Verilog开发直接数字频率合成(DDS)系统,通常通过硬件描述语言进行系统的结构设计与流程设计。采用硬件描述语言设计DDS系统的开发流程一般需要通过6个步骤实现:需要使用代码编制各结构模块并完成功能配置;执行功能性仿真;编译实现逻辑单元连接网表;完成逻辑网表综合;逻辑网表配置;完成映射与布局布线;并检查有无时序违规现象完成后仿真、下载位流文件并展开编程与调试过程,较为繁琐和复杂。相对于使用DSP Builder软件行系统设计时,设计者需要掌握硬件描述语言并拥有数字电路设计经验,并熟悉现场FPGA硬件和软件开发流程,要求设计者具有较全面的电路设计经验。

1.3 DSP Buil der软件

DSP Builder是Altera公司推出的一个面向数字信号处理(DSP)开发的系统级工具,它在QuartusⅡFPGA设计环境中集成了 Math Wor ks的Matlab和Si mulink DSP开发软件,使用FPGA设计DSP系统完全通过Si mulink的图形化界面进行建模、系统级仿真,设计模型可直接向VHDL硬件描述语言转换,并自动调用Quart usⅡ等EDA设计软件,完成综合、网表生成以及器件适配乃至FPGA的配置下载,使系统描述与硬件实现有机的融合为一体,充分体现了现代电子技术自动化开发的特点与优势[4]。

使用DSP Budilder软件设计数字系统的流程:

1)创建Si mulink设计模型。

2)Si mulink设计模型仿真。

3)完成寄存器传输级(RTL)仿真。

4)Si mulink模型设计的综合与编译。

2 基于DSP Builder的FPGA DDS设计方法

采用DSP Builder软件进行FPGA DDS系统开发设计按照前述4个具体步骤进行,具体方法为:

2.1 创建Si mulink设计模型

调用Matlab/Si mulink软件中DSP Buil der软件的库函数模块,搭建一个DDS系统模型。具体实施时:首先启动Matlab软件,新建一个Model模型文件,利用Si mulink Library中的DSP Builder模型库搭建DDS系统模型框图,如图2所示。系统模型中包含有三个输入控制端、中间级电路和一个波形输出端,输入端分别为32 bit频率控制字、32 bit相位控制字和32 bit波形控制字,中间级主要是累加器、加法器、ROM查找表和数据截断类型转换器和一个波形输出,即10 bit的DDSOUT波形输出。

图2 DDS系统模型Fig.2 DDS system model

如上所述,采用DSP Builder软件进行图形化界面进行系统建模时,只需调用库中相应模块进行连接并对参数赋值,即可完成模型文件的设计,相比硬件描述语言设计避免了程序语言对中间模块进行编写的繁琐性。图形化的模块连接也省去编写大量程序流程代码,使系统流程简洁清晰,进而提高设计开发的效率。

2.2 Si mulink设计模型仿真

针对搭建的该DDS系统模型,在Matlab∕Simulink软件中完成模型的行为级仿真,利用Scope/Wavescope等模块观测其输出仿真波形信号。

2.3 完成寄存器传输级(RTL)仿真

在完成Si mulink软件仿真的基础上,使用DSP Builder软件中的Signal Compiler模块生成可被QuartusⅡ调用的DDS工程文件及可供Modelsi m调用的Test bench测试向量文件,完成在Modelsim下的寄存器传输(RTL)级仿真,该RTL仿真结果验证DDS时域波形输出参数指标并可进行信号频谱质量分析,确认DDS模型输出波形是否达到系统设计要求。

该步骤中DSP Builder软件将自动生成并映射逻辑网表,简化了硬件描述语言系统开发中,须将逻辑网表中硬件原语和底层单元配置到固有硬件结构上完成映射与布局布线和后仿真的过程,因此可弱化仿真过程对硬件的需求,简化了配置操作过程,也为系统的软、硬件分离提供了必要的灵活性。

2.4 Si mulink模型设计的综合与编译

在QuartusⅡ中完成综合、网表配置和生成位流文件的程式设计后,对FPGA进行下载、配置从而完成整个DDS开发设计流程。其中第三及第四步可替代采用硬件描述语言开发DDS系统时应用硬件描述语言代码编制DDS各结构模块之后的所有步骤,并且DSP Builder软件设计完成后的直接数字频率合成器系统只需对模型内部几个模块参数进行配置修改就能输出所需相应的波形信号,可快速实现工程设计对多样波形信号进行修改配置的要求。较之采用硬件描述语言实现DDS方法更为简单灵活,同时省去硬件描述语言开发DDS系统在针对程序代码修改后须再次执行编程调试的步骤。

综上所述,使用该设计方法仅4个步骤就可以完成对DDS系统的设计开发。

3 基于DSP Builder的设计实例

本设计方案采用的现场可编程门阵列FPGA芯片是Altera公司的Cyclone系列芯片EP1C6 Q240C8,其容量6 000个逻辑宏单元,等效于标准15万逻辑门电路,速度等级为“-8”(130 MHz左右),完全可通过单片芯片电路实现DDS。

3.1 DDS系统参数计算及仿真模型构建

系统设计参数计算:

1)输出频率及系统时钟选择。在实际应用当中DDS输出频率不能超过0.4fc,其中fc为系统时钟,以避免混叠而落入有用输出频带内。因此若系统要求输出1 MHz正弦波,则采样时钟不应低于2.5 MHz。

2)累加器位宽计算。按照设计要求输出频率分辨率要达到0.02 Hz,若采用系统时钟为50 MHz,由Δfmin=fc/2N可得,N 近似选为32 bit,即相位累加和相位累加器位宽均为32 bit。

3)对于波形RA M的设计,首先应确定波形RA M的深度和字长,如选择8 bit DAC则RA M字长很明显也应为8 bit,而从噪声功率的角度看RA M的地址线的位数应该等于或者略大于D/A字长加2。在本设计中,波形RA M的字长选为8 bit,地址线为10 bit。

仿真模型构建:

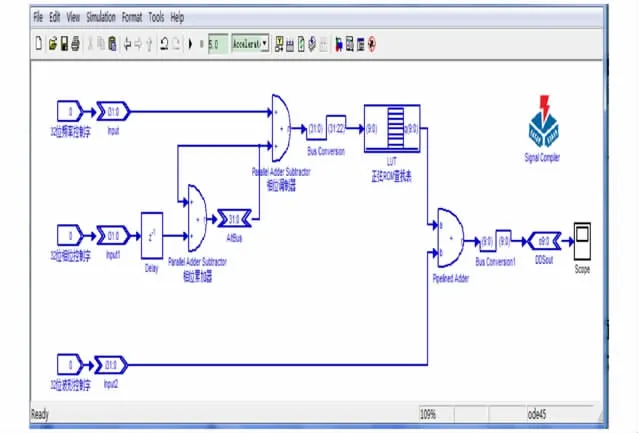

由以上设计参数建立如下基于DSP Builder软件下的DDS系统模型,如图3所示。其中2个Parallel Adder Subtractor分别对应为相位累加器和相位调制器,LUT对应为ROM查找表,LUT通过Bus Conversion转换器完成数据截断与相位调制器连接转换并输出数字波形信号,LUT输出的波形信号与32位波形控制字进行复合,经Bus Conversion转换器调制整形输出。

图3 基于DSP Builder的DDS系统模型图Fig.3 DDS system model base on DSP Builder

3.2 设计模型RTL级仿真及波形分析

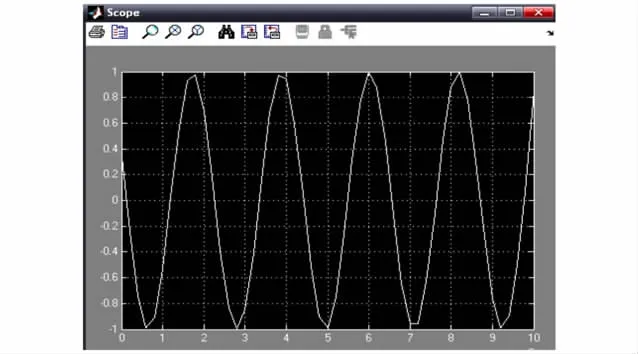

DDS系统的RTL级仿真。首先在Si mulink软件平台下进行功能性验证,在设定系统采样率为50 MHz,累加器位宽32 bit,设置正弦波的最大步长所对应的频率、相位和幅度控制字分别为00100000,0和0的前提下,输出波形的频率为1 MHz,位宽8 bit。如图4所示。

图4 Simulink仿真波形图Fig.4 Si mulink wave diagram

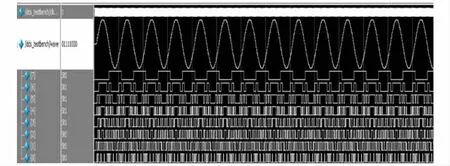

随后Modelsi m仿真软件调用DSP Builder生成的工程文件对输出波形进行时序违规及波形质量分析,如图5所示。

图5 Modelsim仿真波形图Fig.5 Modelsi m wave diagram

由图可见,在不同的参数设置下,如要改变输出波形的的步进精度或需要增加幅度控制等,则只需要在模型中作相应的修改即可,即修改频率控制字、相位控制字便可完成。如需要增加幅度控制,则需要在模型中加入乘法器模块,控制幅度输出,但数字化实现的过程中会存在截断误差以及量化误差,可以使用抖动注入技术等方法提高无杂散动态范围改善输出频谱质量,使输出波形参数满足设计方案的技术指标要求[5]。

3.3 设计综合与编译

针对DSP Builder软件设计完成的DDS系统模型进行编译,通过调用DSP Buil der软件中的Signal Co mpiler模块生成供Quart usⅡ 调用的工程文件,完成综合、网表生成和适配,最后完成FPGA的配置和下载过程。

4 结论

本文提出一种基于DSP Buil der软件的直接数字频率合成的设计方法。该方法在DSP Buil der软件中完成FPGA DDS的模型设计,并在Si mulink软件中完成图形界面下的建模、仿真和系统集成。DSP Buil der软件通过Signal Co mpiler模块生成Quart usⅡ软件中使用的硬件描述语言文件,并且在Si mulink中自动生成RTL测试文件。这些文件是已经被优化的预验证RTL输出文件,可直接用于Quart usⅡ软件中进行时序仿真比较。设计实例表明,设计者无需学习新的设计流程或编程语言,直接使用DSP Buil der和QuartusⅡ软件单独进行硬件设计。该设计方法原理正确,行之有效,使用图形开发界面简单直观,避免了直接数字频率合成设计编制复杂的程序代码语言,并且开发环境与Quart usⅡ软件交互性强,便于修改设计,具有良好的可重配性,从而缩短工程研制周期,为直接数字频率合成设计提供了一种新的设计方法。较之直接模拟合成法、锁相环合成法和直接数字合成法设计直接数字频率合成器的方法更为灵活方便,具有很高的性价比。但数字化实现的过程中会存在截断误差以及量化误差,设计时可通过使用抖动注入技术等方法提高无杂散动态范围,改善频谱质量达到设计指标。

[1]高泽溪,高成.直接频率合成器(DDS)及其性能分析[J].北京航天航空大学学报,1998,24(5):615-618.GAO Zexi,GAO Cheng.Direct digital synthesis(DDS)and perfor mance analysis[J].Jour nal of Beijing Univercity of Aeronautics and Astronautics,1998,24(5):615-618.

[2]王家礼,孙璐.频率合成技术[M].西安:西安电子科技大学出版社,2009.

[3]郭军朝.直接数字频率合成研究及其FPGA实现[D].上海:上海交通大学,2002

[4]杨东,王建业,蔡飞.基于DSP开发工具的自适应滤波器[J].探测与控制学报,2010,32(3):79-82.YANG Dong,WANG Jianye,CAI Fei.The adaptive filter based on the developement tool of DSP[J].Journal of Detection & Contr ol,2010,32(3):79-82.

[5]乐翔,秦士.直接数字频率合成信号的杂散性能分析[J].清华大学学报(自然科学版),2000,40(1):46-48.YUE Xiang,QIN Shi.Analysis of spur property of direct digital synthesis signal[J].Journal of Tsinghua Univercity(science and technology),2000,40(1):46-48.