一种雷达信号处理芯片的8B/10B编码电路设计

王 颖 陈 杰 刘辉华 李 磊

(电子科技大学 成都 611731)

1 引言

雷达作为一种获取战场信息的主要方式,需要探测和接收大量信息。雷达信号处理单元能够迅速可靠的完成雷达信号处理,并及时将结果送到接收机终端。随着集成电路设计与应用技术的飞速发展,复杂的信号处理单元集成在单颗芯片当中,极大的促进了雷达系统的小型化。但是芯片内部大量数据的高速传输成为制约处理器和信号处理系统性能发挥的关键因素。

SerDes是 Serializer/Deserializer(串 行/解 串器)的简称。它是一种流行的基于时分复用(TDM)和P2P技术的高速串行通信方式。在芯片中采用基于SerDes的通信方式,不仅可以提高数据传输速率,还可以减少芯片面积和引脚数量,极大的简化芯片的布局布线和降低成本,很好的解决了数据传输中的码间串扰、直流漂移等问题。其作为高速数据传输通道的起止端,直接影响了系统的数据吞吐量。

2 8B/10B 编码分析[2~7]

首先明确一个概念——代码的不平衡度,即编码结果中0和1的个数之差。若0和1的个数相等,则称编码结果为完美平衡代码,不需要进行直流补偿;若0与1的个数不相等,用一个叫极性偏差(Running Disparity,RD)的参数表示,则需要进行进行直流补偿。在编码得到的10bit数据中0和1的个数只能相等(各是5个)或分别为4和6。这样,编码结果的RD值只能是0、+2和-2三种情况。规定若0与1的个数相等,则RD=0;若0比1的个数少(只能少2个),则 RD=-2,通常用 RD-表示;若0比1的个数多(只能多2个),则RD=+2,相应的就用RD+表示。

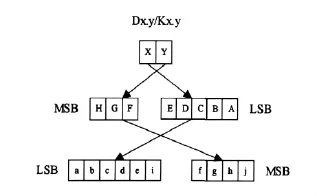

图1 8B/10B编码映射关系

8B/10B编码是一种冗余的编码方式。10bit码字中包含256个数据字符Dx.y和12个特殊字符Kx.y,余下的为无效字符。编码映射关系如图1所示,输入数据的高3位 HGF进行3B/4B编码,低5位EDCBA进行5B/6B编码。值得注意的是,8bit待编码数据和10bit编码结果的高低位顺序相反。

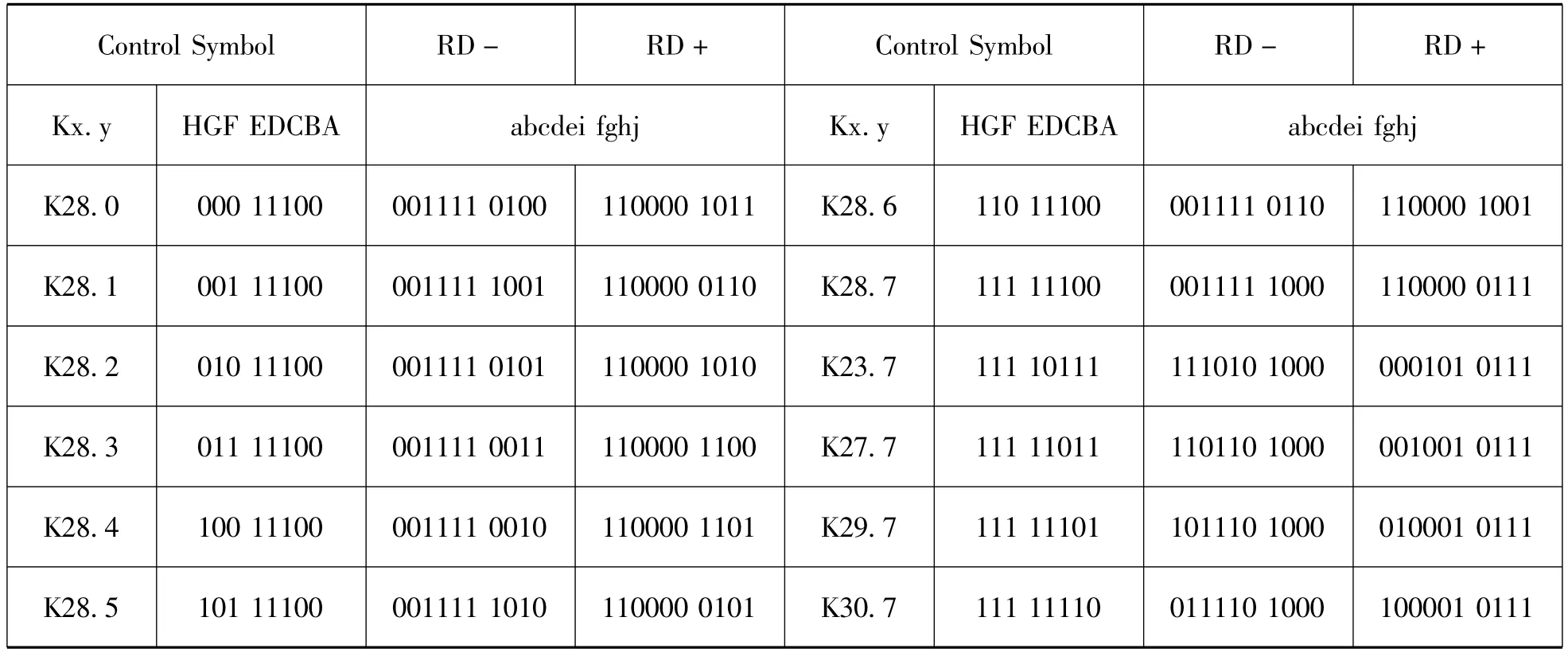

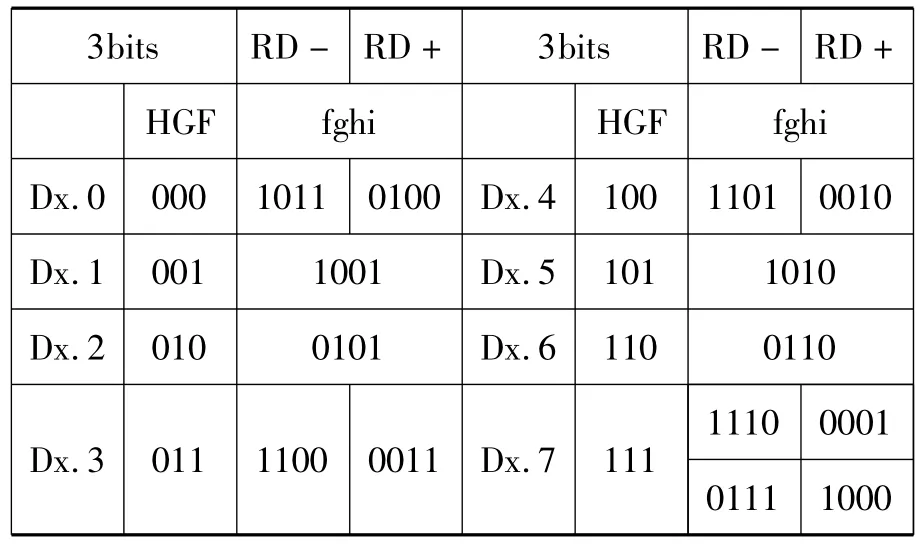

特殊字符Kx.y编码如表1所示,每一个特殊字符编码都有RD-和RD+两种极性。数据字符Dx.y的编码分两部分:5B/6B和3B/4B编码,如表2和表3所示。5B/6B编码结果有三种形式:a.18组唯一的平衡编码;b.1组有极性的平衡编码(D07.y);c.13组有极性的非平衡编码。3B/4B编码结果有四种形式:a.Dx.1、Dx.2、Dx.5和Dx.6的编码输出唯一且平衡;b.Dx.0和Dx.4的编码输出有极性且非平衡;c.Dx.3的编码输出有极性且平衡;d.Dx.7的编码输出有两组四种情况:a.一般情况下Dx.7的编码输出为非平衡且有极性的1110和0001;b.若当前状态为RD-,且前面已编码的6bit码组中e和i位都为1,则3B/4B编码的选择为3B/4B码表RD-列的0111;若当前状态为RD+,且前面已编码的6B码组中e和i位都为0,则3B/4B编码的选择为3B/4B码表RD+列的1000。8B/10B编码时,先设置初始RD极性,再对8bit输入数据进行编码,然后根据此组10bit编码结果决定下一组数据的极性。确定下一极性的规则:如果编码后的10bit码组中0与1的个数相等,则次态极性保持不变;如果0与1的个数不等,则次态的极性为当前极性的反转。无论是普通数据码组、特殊数据码组都符合上述规则。

表1 特殊字符编码表

表2 5B/6B数据字编码表

表3 3B/4B数据字符编码表

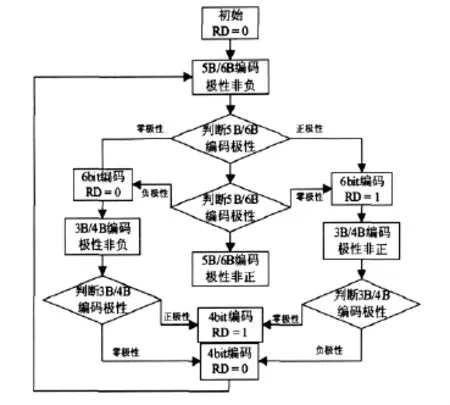

8B/10B编码的核心是基于数据字符和特殊字符编码表的RD极性转换。RD极性转换的目的是避免串行数据流中连“0”或连“1”的数量超过5个。RD极性的计算和对编码的控制流程如图2所示[2]:一般情况下,设置初始极性为 RD-。按照RD-对首个8bit数据的低5位进行5B/6B编码,并判断编码结果的平衡性。若6bit数据平衡,则编码后的RD保持不变,指导高3位数据进行3B/4B编码,此时极性还为RD-;若6bit数据非平衡,则编码后的的RD取反,此时按照RD+指导高3位数据进行3B/4B编码。经过3B/4B编码后,同样要看4bit编码结果的极性。若4bit编码结果平衡,则极性保持不变,仍为RD-;若4bit编码结果非平衡,则极性取反,变为RD+。经过3B/4B编码后的极性就是本组10bit编码结果的极性,按照正负极性交替的规则去指导下一组数据的5B/6B编码。

图2 8B/10B编码RD极性转换流程图[2]

3 8B/10B编码器设计方案

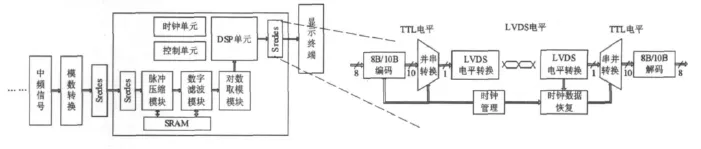

某款雷达信号处理芯片结构如图3所示,经过模数转换的中频信号送入SerDes接口,由并行TTL电平信号转换成高速串行LVDS电平信号送入芯片内部。芯片内部的SerDes模块将LVDS电平信号恢复并解串,再将解串的并行数据送入后续模块进行脉冲压缩、数字滤波,最后通过取模运算将并行数据长度缩短后送入DSP模块进行处理。经DSP单元处理后的雷达信号通过一个双向SerDes通道送入后续的功能单元。单通道SerDes原理框图如图3所示[8,9],发送端经过8B/10B 编码和并串转换后的数据具有了更好的直流平衡特性,然后将TTL电平信号转换为更适合高速串行传输的LVDS电平信号。接收端信号处理过程和发送端相反,这样形成了完整的高速串行传输通道。8B/10B编解码作为高速串行通道的起止端,是SerDes的核心部件。下面将详细介绍该款芯片SerDes接口电路中8B/10B编码器的设计。

图3 某型号雷达信号处理芯片结构框图

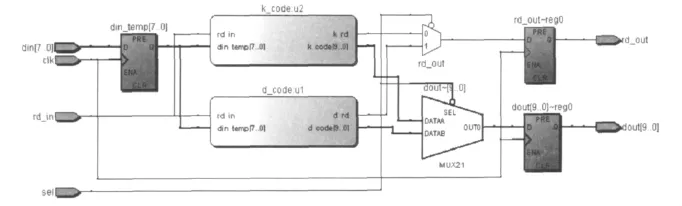

根据8B/10B编码的特点将编码器分成两个模块[2]:特殊字符编码模块 k-code和数据字编码模块d-code。如图4所示为由Quartus II 10.0综合出的8B/10B编码器RTL级电路结构图,输入输出端口如图4所示。

图4 8B/10B编码器RTL级实现框图

din[7:0]为8bit待编码数据输入;clk为编码器时钟信号;rd-in为极性控制信号,0表示RD-,1表示RD+;sel为数据类型选择信号,0表示输入为数据字符,1表示输入为特殊字符;dout[9:0]为10bit编码输出信号;rd-out为下一组数据编码的参考极性,0表示RD-,1表示RD+。

编码器首先将8bit输入信号送入缓存dintemp[7:0],在时钟信号clk上升沿控制下分别送入特殊字符编码模块k-code和数据字编码模块dcode。经过编码的输出接到由sel控制的二选一选择器上,根据sel的值选择编码输出为特殊字符或数据字符,并将结果送到编码器输出端rd-out和dout[9:0]。

3.1 特殊字符编码模块k-code

8B/10B编码规定了12个特殊字符Kx.y。由表1可知12组特殊字符都有RD-和RD+两种编码方式,并且这两种极性的编码互反。对Kx.y编码采用基于ROM的查找表方式,即建立11×12的ROM单元存储RD-极性的Kx.y和编码平衡性信息,其中每组存储单元的最高位为0表示Kx.y编码平衡,为1表示Kx.y编码非平衡;余下的10位存储编码结果。通过输入8bit地址数据在rd-in信号控制下进行查找表操作得到Kx.y的编码。编码后的极性k-rd由存储单元中的平衡信息位和上一组编码极性异或得到。

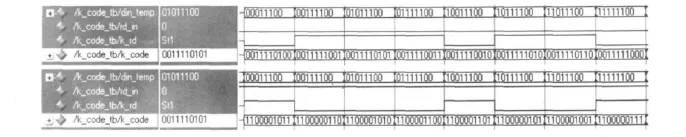

使用Modelsim SE 6.1f对k-code模块进行功能仿真。分别假设初始极性为RD-和RD+,经过固定的延迟后依次输入12组特殊字符。通过观察图5 中 din-temp[7:0]和 k-code[9:0]的波形可知,12组特殊字符和其编码结果一一对应;观察rd-in和rd-k信号波形可知,在初始极性一定的情况下,极性转换逻辑正确。

图5 特殊字符编码仿真图

3.2 数据字符编码模块d-code

数据字编码模块d-code分为三部分:5B/6B、3B/4B编码模块和逻辑输出模块。其中din-temp[7:0]为数据字符输入端,rd-in为输入数据字符编码极性,d-code[9:0]为数据字符编码输出端,rd-d为输出数据字符编码极性。工作原理是首先将8bit数据字符送入 din-temp[7:0];然后分别将 dintemp[7:5]和 din-temp[4:0]作为地址信号输入ROM,通过查找表得到3B/4B和5B/6B的暂时编码,送入寄存器组 code4[4:0]和 code6[6:0],其中code4[4]和 code6[6]分别存储编码结果的平衡性信息。最后,通过四个特定函数在{rd-in,code[6]}信号控制下按照上述极性转换规则得到3B/4B和5B/6B编码的正确变换,并组合成10bit数据输出。逻辑输出模块控制着编码的正确输出,是d-code的核心模块。下面简要介绍d-code各个模块,并对逻辑输出模块的四个函数做详细分析。

5B/6B编码模块

建立一个7×32的ROM存放32个5bit输入的编码结果,默认极性为RD-。每组存储单元的最高位代表编码结果的平衡性,0代表平衡,1代表非平衡;余下的存储6bit编码结果。通过输入缓存输入5bit地址信息来确定6bit编码输出。

3B/4B编码模块

建立一个5×8的ROM存放8个3bit输入的编码结果,默认为RD-极性。每组存储单元的最高位代表编码结果的平衡性,0代表平衡,1代表非平衡;余下的存储4bit编码结果。通过输入缓存输入3bit地址信息来确定4bit编码输出。对于Dx.7,还要增加一个限制条件来确定编码输出,即一般情况下Dx.7的编码输出为1110和0001,但是如果当前状态为RD-,且前面已编码的6bit码字中e=i=1,则3B/4B编码的选择为3B/4B码表RD-列的0111;如果当前状态为RD+,且前面已编码的6bit码组中e=i=0,则3B/4B编码的选择为3B/4B码表RD-列的1000。

逻辑输出模块

作为d-code模块的核心,逻辑输出模块用函数code-0-4、code-1-2-5-6、code-3 和 code-7 实现极性转换和数据的组合输出:

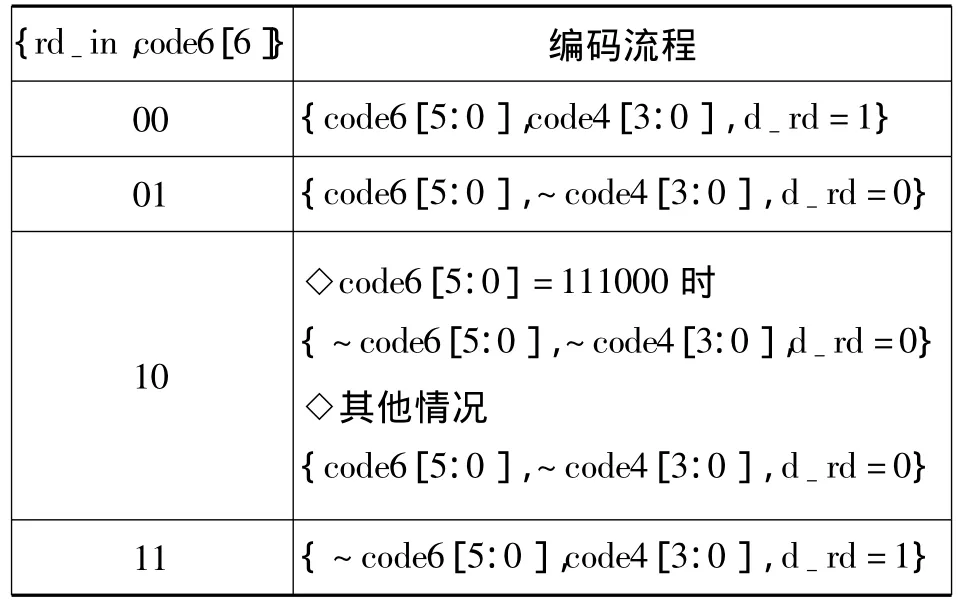

code-0-4函数执行HGF为000和100时3B/4B编码和组合输出。由表2可知,000和100的编码结果有极性且非平衡。编码流程如表4所示。

表4 code-0-4函数操作流程

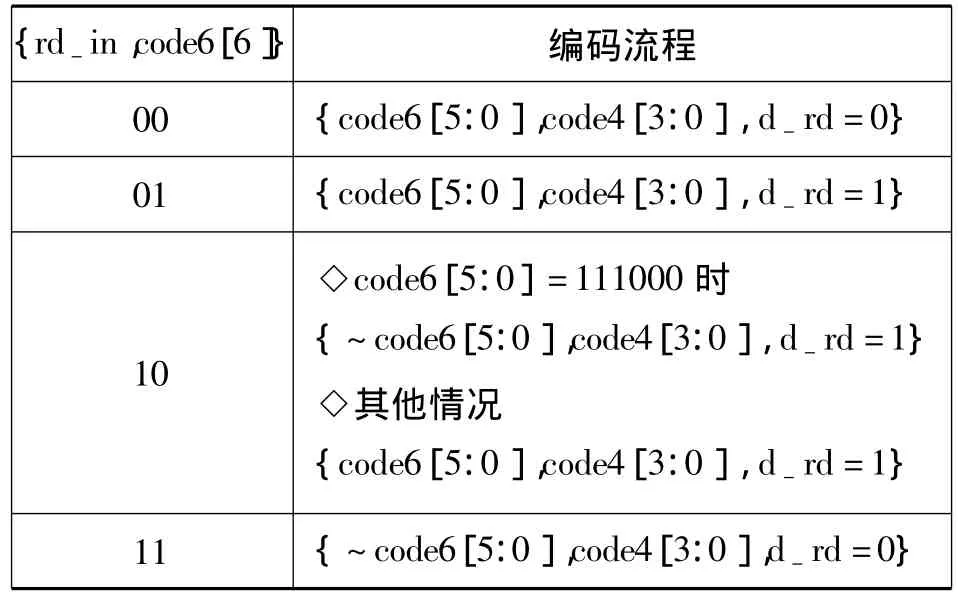

code-1-2-5-6 函数执行 HGF 为 001、010、101和110时的3B/4B编码和组合输出。这些数据的编码唯一且平衡。编码流程如表5所示。

表5 code-1-2-5-6函数操作流程

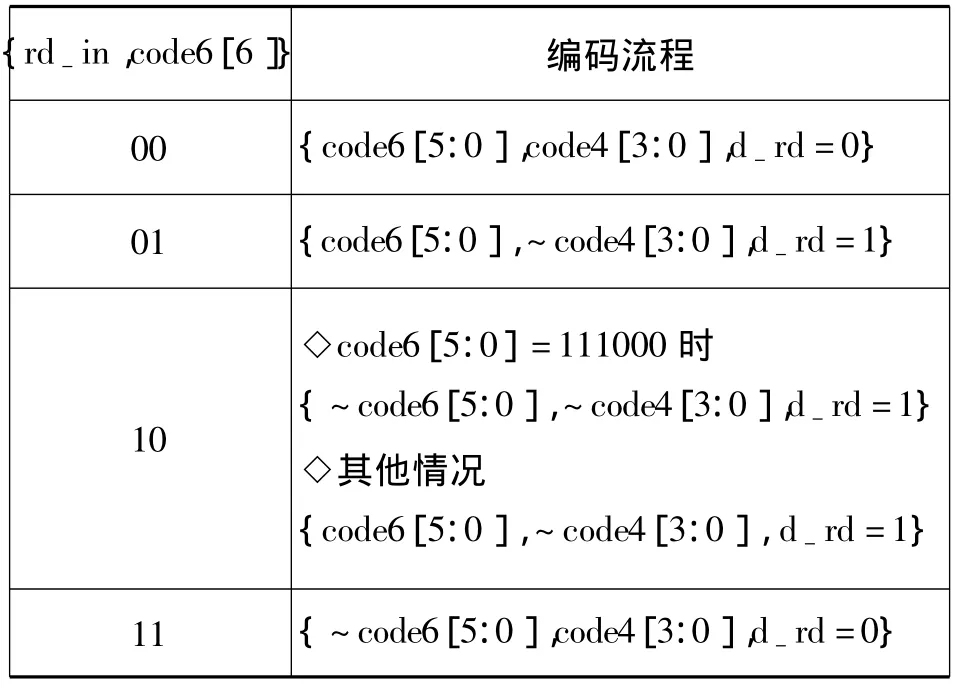

code-3函数执行HGF为011时的3B/4B编码和组合输出。011的3B/4B编码有极性且平衡。编码流程如表6所示。

表6 code-3函数操作流程

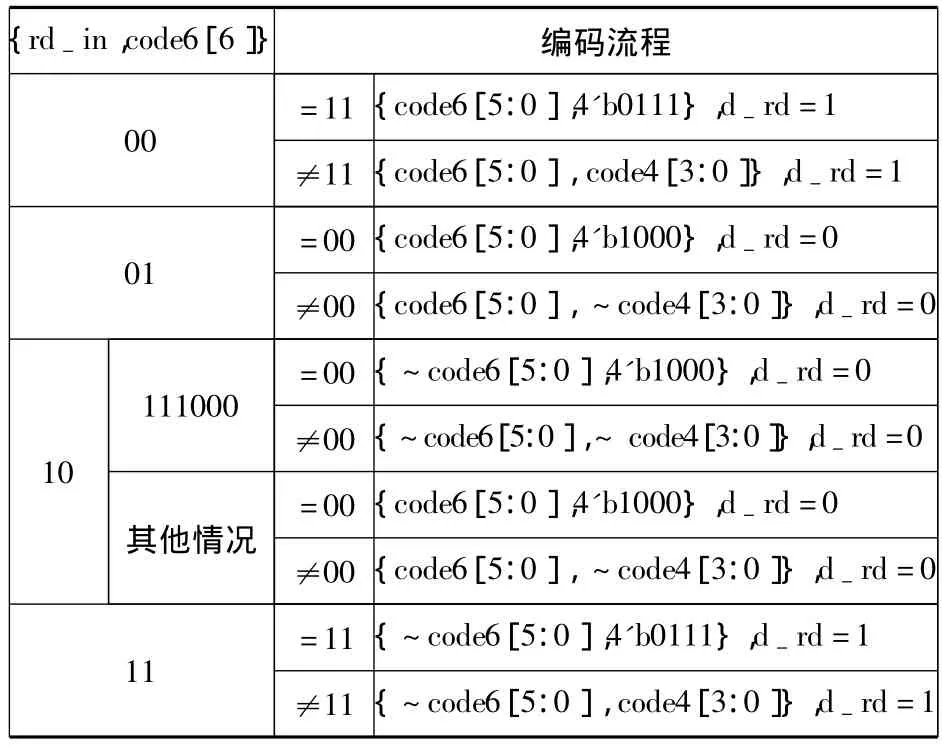

code-7函数执行HGF为111时的3B/4B编码和组合输出。编码流程如表7所示。

表7 code-7函数操作流程

通过遍历性得将256种8bit数据分别在RD-和RD+初始条件下对d_code进行进行功能仿真,部分仿真结果如图6所示。利用四个特定函数实现极性转换和编码组合输出,功能正确且逻辑清晰直观,达到设计要求。

3.3 顶层模块code-top

在完成k-code和d-code后,建立顶层模块code-top。通过数据类型选择信号sel来选择特殊字符或数据字符编码。分别假设rd-in为0和1,通过控制sel为0和1来对数据字符和特殊字符编码。如图7所示由上到下依次为rd-in=0时对数据字符和特殊字符的编码及Dx.7的部分仿真波形,dout[9:0]输出比din[7:0]输入延迟一个周期,在clk信号上升沿采样。经过仿真分析波形正确,电路设计达到目的。本设计工作在125MHz条件下,和并串转换等模块组成2.5Gbps数据率的SerDes发射模块并结合接收端的串并转换及时钟数据恢复模块,组成完整的高速数据传输通道,完成该款雷达信号处理芯片与周围功能单元的高速串行数据通信。

4 结束语

8B/10B编码器是我们设计的高速SerDes接口电路的重要组成部分,在设计中对8B/10B编码器进行了功能仿真、综合和时序仿真。经过与其他模块组成SerDes接口应用到某型号雷达信号处理芯片设计中,成功通过了系统级仿真验证,实现了芯片内和系统级数据高速传输。

[1]Michael D.Ciletti著,张雅绮,李锵译.Verilog HDL高级数字设计[M].北京:电子工业出版社.

[2]李永乾.基于8B/10B编码技术的SerDes接口电路设计[D].电子科技大学硕士学位论文,2010:30-40.

[3]李宥谋.8B/10B编码器的设计与实现[J].电讯技术,2005,6:26-36.

[4]刘智,宁红英,王普昌.一种新的8B/10B编码电路设计[J].通信技术,2009,7:60-61.

[5]袁冰,来新泉,叶强等.一种高速串行数据发生器芯片的设计[J].电路与系统学报,2008,4:79-82.

[6]叶雷,朱红.8B/10B编解码的IP核设计[J].国外电子元器件,2005,11:19-22.

[7]赵文虎.基于逻辑设计的光纤通信8B/10B编解码方法研究[J].电路与系统学报,2003,8(2):48-53.

[8]Dave Lewis.SerDes Architectures and Applications[C].National Semiconductor Corppration.

[9]David R.Stauffer,Teanne Trinko Mechler.High Speed SerDes Devices and Applications[M].Springer,134-158.