TS20XS系列DSP程序优化设计方法及应用

刘 浪 陈伯孝 任腊梅

(西安电子科技大学 西安 710071)

1 引言

在工程实践中为了使复杂的算法能够满足实时性的要求,需要充分发挥DSP的高速处理能力,提高软件的执行效率,使处理器能够以较高的性能实现设计的要求。一般的程序优化的方法主要有[1]:在处理器允许的情况下尽量采用并行指令来实现相应的运算功能;将算法中的循环部分展开,充分利用软件流水线的操作以获得最大的并行性能,尽量避免流水线延时;对算法的数学表达式进行重建,使得重建后的工程实现算法更适合处理器的架构。本文根据TS201S系列DSP内部的结构特点和指令的控制方式,以TS201S为例分别从DSP两组寄存器组的同时使用、IF-DO-ELSE指令的灵活运用、系数存储单元的合理分配、指令间延时的减少、双整型逻辑运算单元的综合运用等方面介绍DSP程序的优化设计方法。

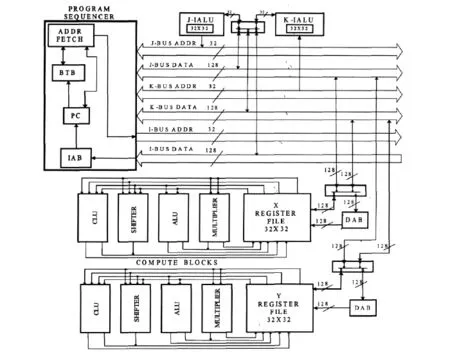

2 TS201S DSP的内部结构

ADSP TS201S DSP内部结构如图1所示[1]。主要特点有:两个独立的双运算模块(X-ALU和YALU),使TS201S DSP具有双核处理能力;两组独立的整型逻辑单元可以同时对核内存储器、外部存储器、其它处理器的共享存储单元寻址;4组相互独立的128位宽度的内部数据总线,借助于交叉连接器与每个内部存储块相连,提供4字长的数据、指令及I/O的访问。

图1 TS201S处理器内核结构[1]

3 程序优化设计方法

在一个程序中,循环体内的指令行(TS201S DSP一个时钟周期执行一个指令行,一个指令行中最多可有四条指令)执行次数最多,程序优化的重点在于如何减少程序中循环体内指令行的执行周期。特别对于多重循环,嵌套越深,循环程序的优化对提高整个程序的执行效率的作用就越大。以一个两层循环为例,若外循环次数为n,内循环次数为m,如果在内循环中通过优化使得循环所需的指令执行周期数减少1个,则整个程序可节省大约(m·n)个指令周期。可见,减少循环体内指令行的执行周期数,整个程序指令执行周期数就会随循环次数成倍的减少。

下面从几个方面介绍减少指令执行周期数的方法。

3.1 DSP两个寄存器组的使用

TS201S处理器内核中有两个运算模块[1],每个模块中各有一组32个32位的寄存器,分别称为X寄存器组和Y寄存器组。在编写程序时要充分发挥DSP的双核处理能力,尽量同时使用X和Y寄存器组,使得循环的执行次数仅为使用单核处理时的一半,可使得运算量减少,在理论上可以使得运算效率提高50%。但是在有些情况下当循环次数减少的同时,循环中也会增加相应的处理,使得循环中的指令行增多,最终会使得运算效率的提高达不到50%。

3.2 IF-DO-ELSE指令的使用

在条件判断时使用该指令,可以使在条件成立或不成立时要执行的指令和条件判断指令在同一时钟周期运行,以此提高指令的并行性[4],从而提高程序的运算效率。在某些情况下还可以省去跳转指令,进而减少跳转指令带来的延时,进一步提高程序的运算效率。

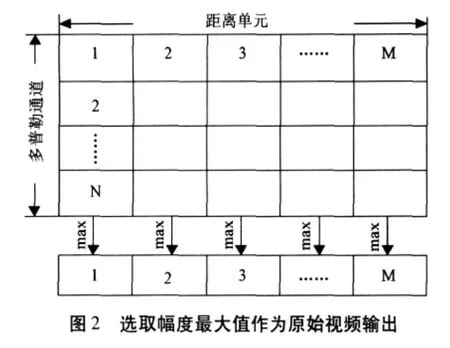

例如,在雷达信号处理中,经常需要从动目标检测(MTD)处理结果中对相同距离单元、不同多普勒通道的信号中选取幅度最大值作为原始视频信号,如图2所示。假定距离单元数为M,多普勒单元数为N。第n个距离单元的输出信号:

式中A(m,n)代表MTD求模后的第n个距离单元、第m个多普勒通道中信号的幅值。

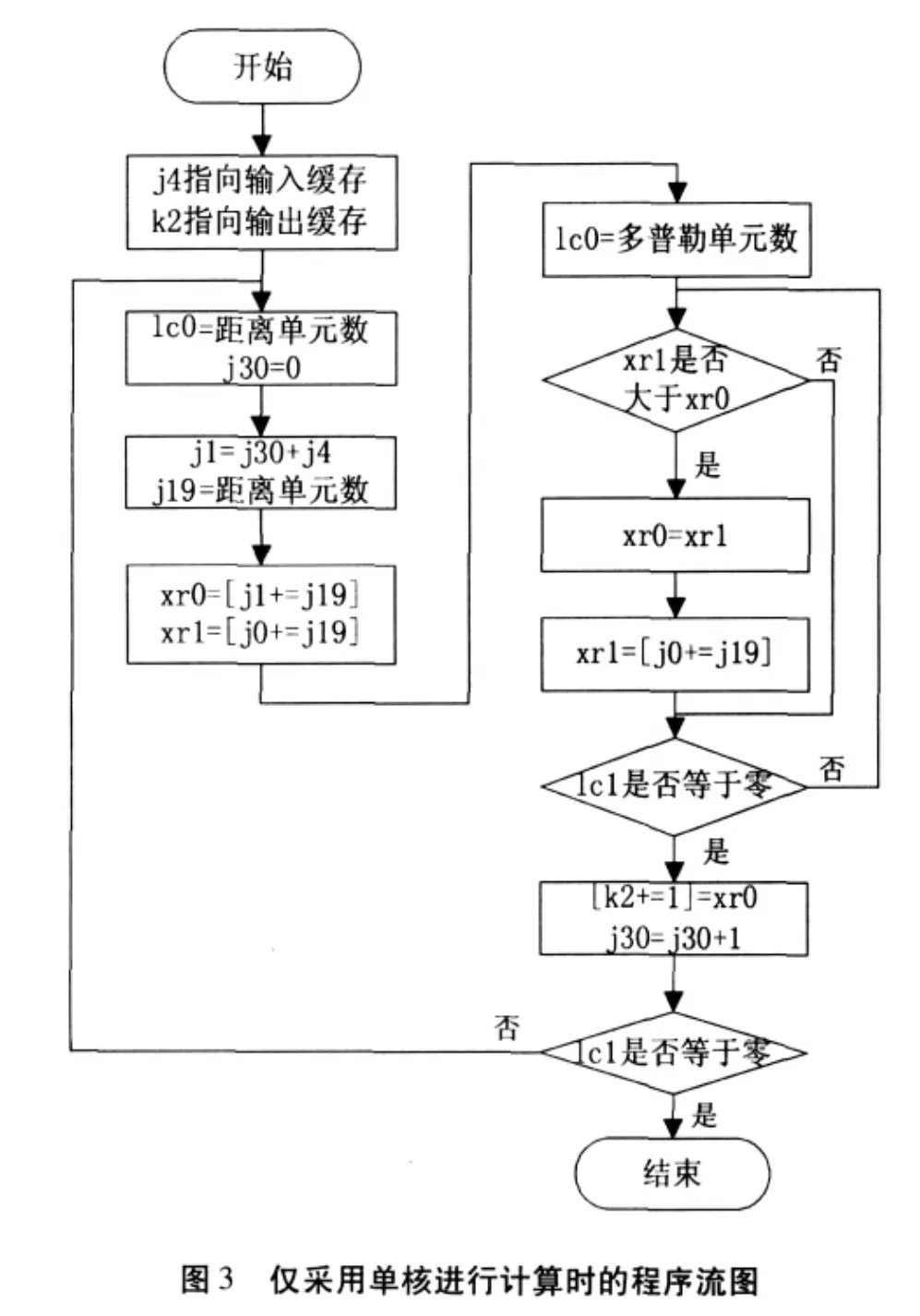

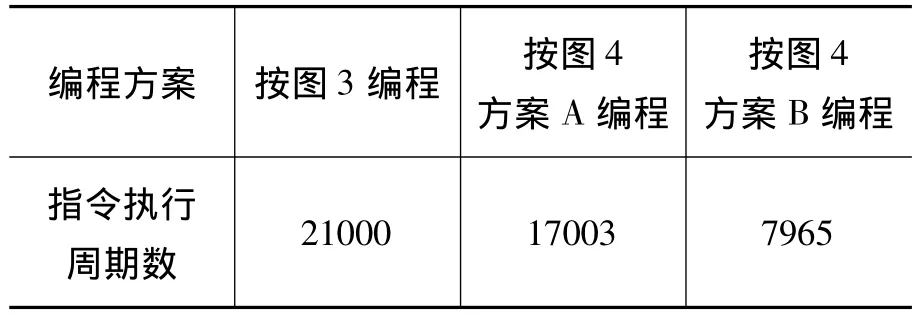

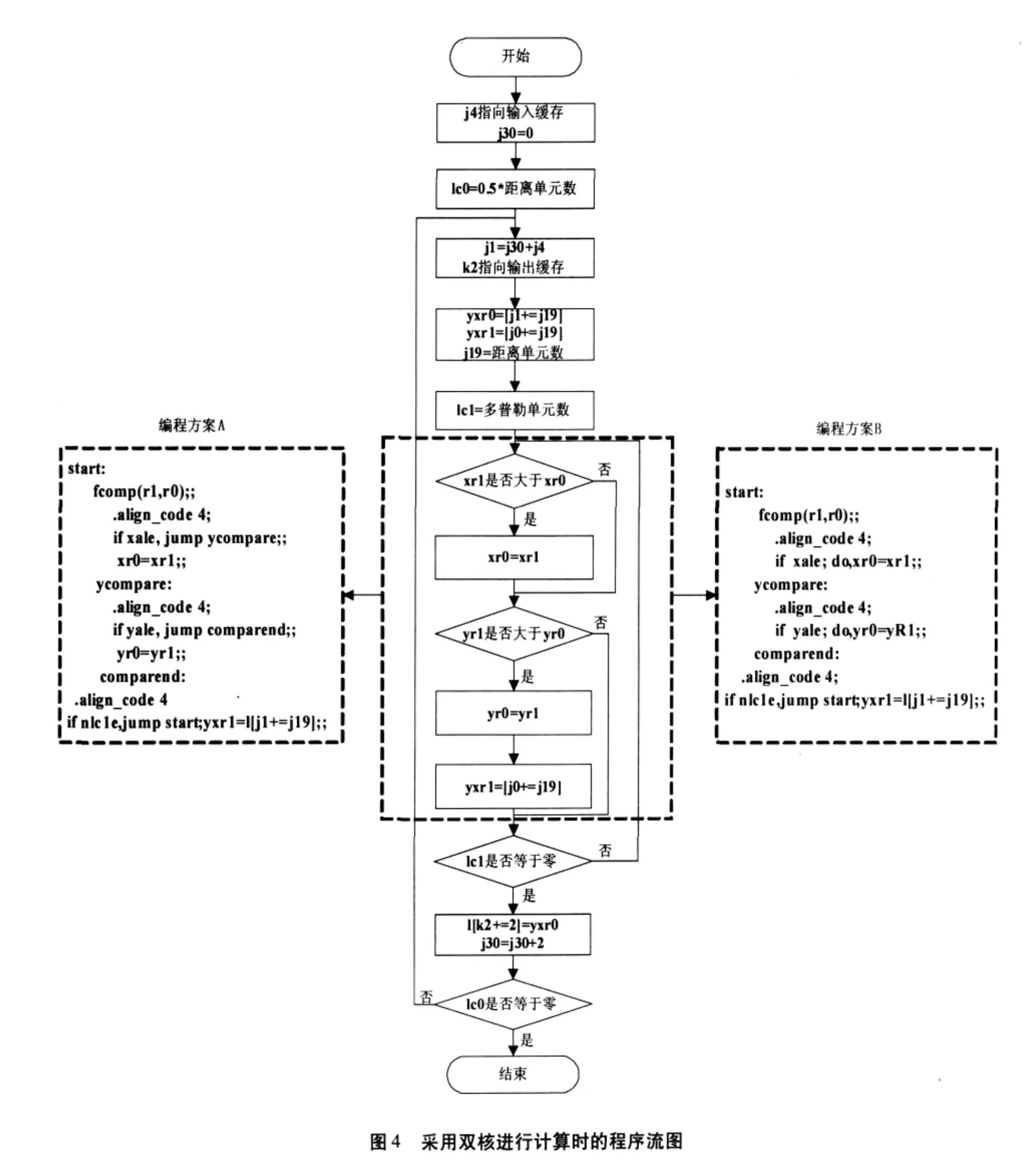

图3、图4给出了采用不同编程方式实现上述功能的三种方案。表1中同时给出了当M=380,N=8时程序所需的指令执行周期数。可见,按图4中的方案B进行编程比图3中的方案进行编程和图4中的方案A进行编程的程序所需指令执行周期数分别减少了62%和53%。进而说明同时使用X和Y寄存器组比仅使用X或Y寄存器组时程序的执行效率要高,在条件判断时使用IF-DO-ELSE指令会进一步提高程序的执行效率。

表1 M=380,N=8时三种方案所需的指令执行周期数

3.3 滤波系数存储单元的合理分配

TS201S[1]可以对存储器进行单字、双字、四字不同长度的读写操作。当进行单字寄存器的读写操作时对地址指针没有特殊要求,但是在进行双字寄存器或四字寄存器的读写操作时,地址指针必须分别可被2整除或被4整除。

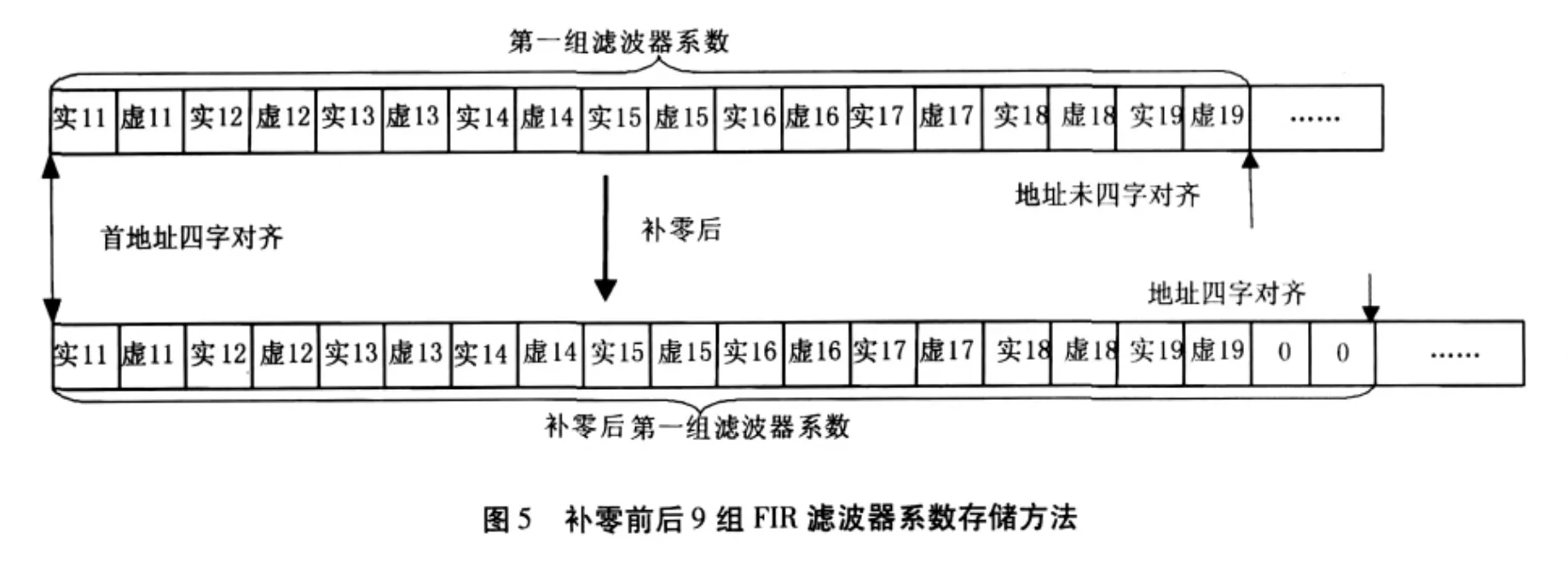

当对同一存储区的数据进行访问时,假设每次只进行数据的读取不进行别的操作运算,分别进行单字寄存器、双字寄存器、四字寄存器读取时,单字寄存器读取所用时间为双字寄存器所用时间的2倍,双字寄存器读取所用时间为四字寄存器所用时间的2倍。所以在进行存储区的读写操作时应尽量使用四字寄存器的加载或存储访问。此时就要求要读写的数据存储区的起始地址要是四的倍数。但是有时要读写的数据的存储起始地址并不是四的倍数,这时可以将要读的数据通过补零的办法使其存储起始地址成为四的倍数,例如对9组脉压数据进行FIR滤波时,一般事先将这9组FIR滤波器系数存储在DSP内部的一段存储区中,在滤波时分别读取这9组系数进行滤波处理,但是9组系数每组按实虚部存储,所以每组系数的数据量为18,则下一组滤波器系数的起始地址不是4的倍数,此时在读取下一组滤波器系数时就不能进行4寄存器的读取访问,但是通过在每组系数后边补两个零使每组系数的数据量为20,就可进行四字寄存器的访问。这样使得FIR滤波器系数所需的存储空间变大,所以称此办法为牺牲空间换时间法。图5为补零前后9组FIR滤波器系数存储方式。图中“实1n”和“虚1n”分别指第一组滤波器的第n个系数的实部和虚部。

3.4 双整型逻辑运算单元的综合运用

TS201S共有两块双整型逻辑运算单元(IALU)寄存器组,分别为J-IALU寄存器组和K-IALU寄存器组,每个IALU寄存器组包含32个数据寄存器和8个专用的循环缓冲寻址寄存器[1]。IALU中所有寄存器都是32位宽,也都是存储器映射寄存器[1]。J-IALU寄存器组的寄存器是J31~J0,K-IALU寄存器组的寄存器是K31~K0。除了J31和K31外,这些寄存器都是通用的,且用于保存整型数据和用于存储区的寻址[1]。当对同一组数据进行相同运算处理时,可以在同一指令行中读取本次要进行运算的数据,存储上一次的运算结果,这就要求在循环体外边先进行一次处理,这样会提高指令间的并行性,进而提高算法的运算效率。但是按照TS201S的IALU指令约束[1]:在同一指令行中,J-IALU只能执行一条指令,K-IALU也只能执行一条指令。可以在同一指令行进行一条J-IALU指令和一条K-IALU指令操作。这就要求分别使用J-IALU寄存器组中的一个寄存器和K-IALU寄存器组中的一个寄存器,分别指向要读取的存储区和要写入的存储区,从而在同一指令行中使用J-IALU寄存器组中的一个寄存器进行读取操作,用K-IALU寄存器组中的一个寄存器进行存储操作,反之亦然。

TS201S的内部总线借助于交叉连接器与每个内部存储块相连,且交叉连接器不能直接访问存储器,需要通过存储器缓冲(包括预取数缓冲、读缓冲、回存缓冲和高速缓冲)才能访问存储器,所以在访问存储器时存在存储器缓冲是否命中的问题。如果所访问的数据未在存储器缓冲中,存储器缓冲将花费一些时钟周期来访问存储器中的数据,所以要采用相应的措施来提高存储器缓冲的命中率。由于预取数缓存的预取数操作是将存储器指定地址对8取模后[5],将所在地址的8个32位字数据传输到预取数缓存内,数据的存储起始地址最好是8的整数,可避免第一次预取数操作取出无用数据;指针的位移量尽可能不要超过8;所以一般要求对于存储在同一存储区并进行相同处理的数据,尽量使用同一指针;数据处理根据指针的方向顺序进行。

3.5 减少指令间的延时

对刚开始编写TS201S汇编程序的设计者,往往存在一个误区:认为程序中使用的指令行越少,程序的执行效率越高,这是由于没有考虑指令间的延时状态,而延时状态并不是程序[1],也不是由用户编写的,在程序和反汇编程序中并不能直接观察到。在延时状态中,处理器基本处于空闲状态,仅仅是在等待延时的结束,而并不执行任何指令,那么延时状态的存在意味着处理器要浪费一些指令周期,所以有时可能程序的并行程度设计得很好,但是程序的执行效率反而下降。

处理器的流水线执行指令方式在执行不同的指令行时会引起一些开销,影响这些开销的因素主要有指令间的相关和资源的冲突。

对于指令m和指令n,如果指令n要用到指令m产生的结果,则称指令n数据相关于指令m[2]。在上一个指令周期运算的结果,如果在下一个指令周期中立刻作为源操作数使用,这两条指令之间就存在数据相关。这时,处理器会根据指令的不同在这两条指令之间插入一定的延时状态,而在这段时间内,处理器基本上是处于空闲状态,仅仅在等待延时状态的结束,而不执行任何指令。在程序设计过程中,如果能避免延时或充分利用延时再进行一些运算,就能实现程序的进一步优化。

资源冲突是内部总线试图进行处理器的存储器访问时[1,3],相应的存储空间处于繁忙状态或者冲突时产生的,所以在同一指令行中如果同时出现存储指令和读取指令时应注意这一问题。建议对同一程序中的不同缓存区分配在不同的存储区(TS201S共有6个4Mbits的存储区),从而减少资源冲突,提高程序的运行效率。

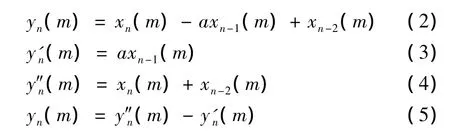

例如,在三脉冲对消过程中,需要在每个距离单元对三个脉冲重复周期的回波信号进行处理。在第m个距离单元、第n个脉冲重复周期的输出信号:

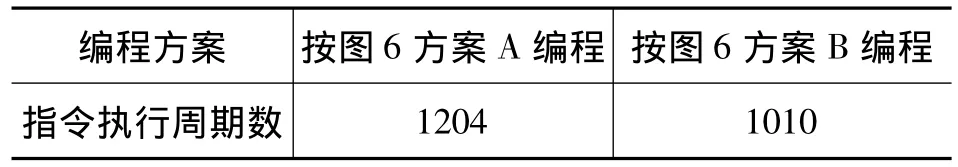

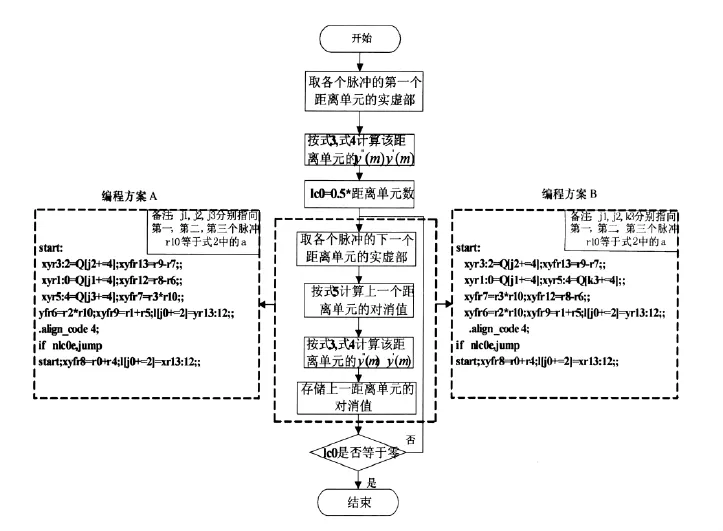

表2给出了当M=380时采用不同编程方案实现上述功能的所需的指令周期数,可见方案B的执行效率比方案A提高了16%。进而说明运用双整型逻辑运算单元IALU比只采用一个整型逻辑运算单元IALU可减少指令间延时,进而提高程序的执行效率。

表2 M=380时方案A和B所需的指令执行周期数

图6 三脉冲对消时的程序流图

4 结论

本文分别从DSP两组寄存器组的使用、IF-DOELSE指令的使用、系数存储单元的合理分配、指令间延时的减少、双整型逻辑运算单元的综合运用几方面说明如何对程序进行优化,并给出了实例,从给出的实例可以看出本文提出的优化方法是切实可行的。本文所述的优化方法同时适用于TS20XS系列DSP程序的优化,在其它DSP中可借鉴。

[1]刘书明,罗勇江.ADSP TS20XS系列DSP原理与应用设计[M].北京:电子工业出版社,2007.

[2]John L.Hennessy,David A.Patterson(郑纬民等译).计算机系统结构-量化研究方法[M].北京:电子工业出版社,2004.

[3]Analog Device Inc.ADSP-TS201TigerSHARC Processor Hardware Reference,2003.

[4]Analog Device Inc.ADSP-TS201TigerSHARC Processor Programming Reference,2003.

[5]钱诚.基于DSP雷达信号参数估计的准实时处理方法研究[D].南京航空航天大学硕士学位论文,2008.

[6]苏涛,赵峰,卢刚.高速DSP新技术在雷达信号处理中的应用[J].火控雷达技术,2005.

[7]www.analog.com.