SRAM型FPGA单粒子翻转测试及加固技术研究

邱金娟,徐宏杰,潘 雄,朱明达

(北京航空航天大学,北京 100191)

0 引言

空间辐射环境中的带电粒子会导致航天器电子系统的半导体器件发生单粒子效应,严重影响航天器的可靠性和寿命,其中高能质子和重离子是导致单粒子效应的主要因素。必须对航天器用电子元器件的单粒子效应进行评估,采取一定的抗辐射加固措施,提高其可靠性。因此,空间辐射的单粒子效应研究具有重要意义[1]。随着航天事业的发展,小型化已经成为卫星发展的主要趋势,它要求所用电子元器件必须具有集成度高、尺寸小的特点,这就使得现场可编程门阵列(Field Programmable Gate Array,FPGA)成为星用电子元器件的主要器件。

SRAM型FPGA是目前应用最广泛的FPGA架构,使卫星在轨编程成为可能,因此在空间得到了广泛的应用。但空间应用表明,SRAM型FPGA器件具有较弱抗辐射能力,这使得FPGA器件的辐照效应研究成为空间电子元器件辐照效应研究的一个重要课题。针对单粒子翻转进行了相应的试验设计,为星载SRAM型FPGA的运行寿命评估及加固设计提供了重要的参考依据[2]。

1 单粒子翻转

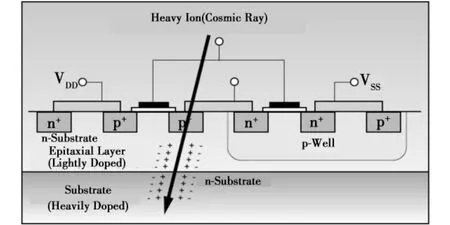

单粒子翻转(Single Event Upset,SEU)是一种位翻转,它既不损害器件也不干扰器件以后的工作,只会改变器件的当前状态。当一个高能带电粒子穿过pn结的灵敏区时,在其路径上,粒子能量的一部分被硅原子所吸收,并在硅中产生电子——空穴对。这些电子——空穴对在pn结电场作用下发生漂移运动和扩散运动,电荷被收集之后,可使pn结诱发一个零点几纳秒的电流脉冲。瞬态电流会使节点电势发生变化,达到一定程度会使导通管截止,截止管导通,引起器件逻辑状态翻转,这就是单粒子翻转[3]。如图1所示。

图1 重离子引发的SEUFig.1 Heavy ion caused SEU

SRAM型FPGA内的配置存储器、块存储器、触发器等资源是单粒子翻转的敏感区。单粒子翻转尤其备受关注,因为它不但影响用户设计的触发器和BRAM块,而且还影响器件的配置存储器,它们可能改变电路的功能。全面估计SEU的敏感度是非常困难的,所以地面测试是不可避免的一个阶段。

2 单粒子翻转的测试技术

2.1 单粒子翻转的静态测试

静态测试是相对器件而言的,用来测试整个器件设备对辐射的敏感程度,它主要是测试FPGA内的配置存储器、块存储器,从而获取FPGA器件的配置存储器的翻转截面及块存储器的翻转截面。图2是FPGA单粒子效应静态测试系统的测试方案。

图2 FPGA静态测试方案Fig.2 Static test scheme

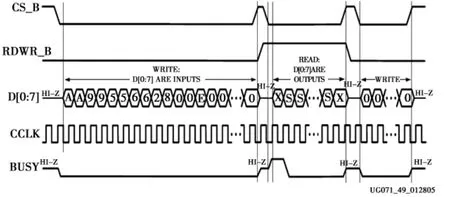

图2的FPGA芯片是用于存放FPGA的读回(Readback)命令、配置命令以及上传读回数据。逻辑控制模块主要用于实现被测FPGA的SelectMAP接口的读写控制时序(见图3)。SelectMAP接口是一个8位的双向数据端口,可以通过它对Virtex进行配置,也可以通过它读回配置数据,它是Virtex最快的配置方式[4-5]。用SelectMAP进行配置需要8位数据 D0:D7和7个控制状态信号,分别是 CCLK、PROG、DONE、INIT、CS_B、RDWR_B、BUSY。

图3 SelectMAP接口读回时序图Fig.3 Readback time sequence of SelectMAP

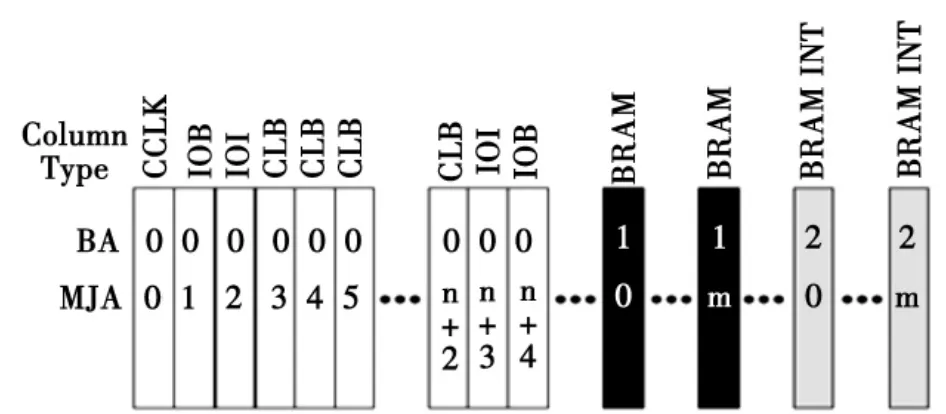

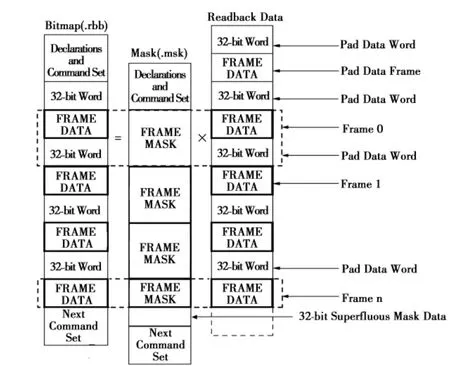

在辐照前,上位计算机把提前设计好的程序下载到被测器件中,然后根据以上时序图,通过下位FPGA的SelectMAP接口读回配置文件并将其上传给上位机进行储存作为原始文件,然后打开辐射源进行照射,经过一定时间或一定剂量的照射后,再次读回配置文件并上传,然后上位计算机在掩码文件的帮助下,比较原始读回文件相应字节与照后读回内容的异同。读回文件的内容分布如图4,读回数据有效性的计算关系如图5。不相同时,根据图4和图5所示的配置数据分布与配置存储器物理地址的映射关系给出具体错误发生的位置,并将错误数与位置上传上位机。

图4 配置文件内部分布图Fig.4 Configuration memory map

图5 读回数据正确性判断Fig.5 Verifying the correctness of readback data

2.2 单粒子翻转的动态测试

静态测试难以测试到FPGA内部触发器及全局寄存器等资源,并且不能探测到程序运行时FPGA对辐射的敏感度。为了弥补这一不足,本系统还设计了动态测试的功能,用于测试FPGA内部有数据传输时,其内部BlockRAM(块存储器),CLB(配置逻辑单元)的单粒子翻转敏感度。

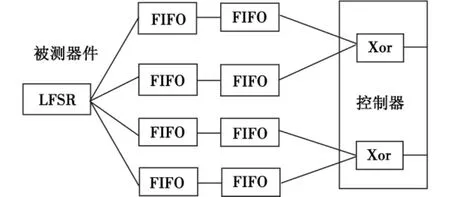

将BRAM配置成8×8192的FIFO(First Input First Output)。用线性反馈移位寄存器(LFSR)产生相同的随机数填满FIFO。当4路FIFO被随机数填满后,开始不断向外溢出;将4路不断溢出随机数进行比较,不同的位数即为翻转的位数。为了防止比较器受到单粒子效应的影响,精确地测试BRAM的翻转敏感度,将比较电路设计在控制器中。采用LFSR产生的随机数填满FIFO,即使LFSR发生翻转也不影响测试结果。此动态测试方法占用了BRAM 90%以上的资源,能够较准确地评估 BRAM的单粒子翻转敏感度[6]。其配置框图见图6。

图6 BRAM测试图Fig.6 Test circuit of BRAM

将CLB配置成6路1×1450的SR(Shift Register),用相同的数填满SR,在相同时钟下进行移位,将输出数据进行比较,得到的翻转结果上传上位机。此动态测试方法占用了CLB 80%以上的资源,能够较准确地评估CLB的单粒子翻转敏感度。其电路配置见图7。

图7 CLB测试图Fig.7 Test circuit of CLB

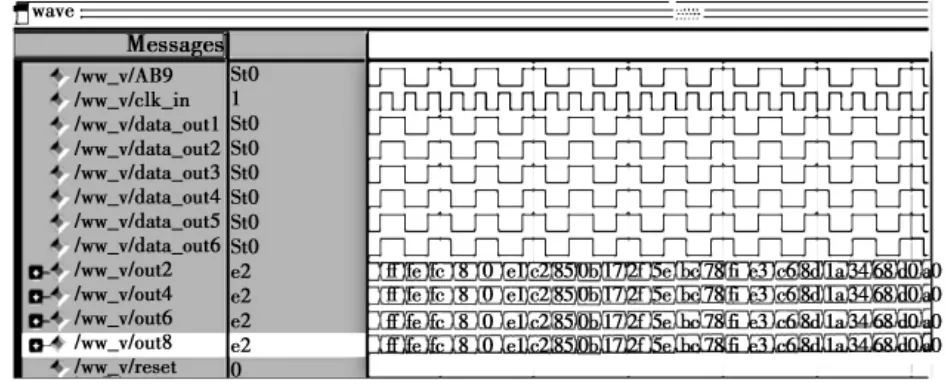

动态测试的翻转结果也将实时地上传并显示到上位机界面上,没有翻转发生时的仿真结果见图8。

为了验证其可靠性,进行了故障模拟,在程序设计时故意将6路数据中任意一路注入错误,经试验观察都可以实时地上传并显示到上位机界面上。

图8 CLB和BRAM测试无翻转的仿真结果Fig.8 Simulation result of CLB and BRAM

3 单粒子效应的防护方法

SRAM型FPGA具有速度快、容量大、可反复编程的能力,是目前卫星通信平台使用的主要器件。由于反熔丝的FPGA不具备二次编程能力,而基于Flash的CPLD的容量规模比较小等原因不适合在卫星平台上使用,所以本文讨论的对抗单粒子效应的方法也是基于SRAM型FPGA的。目前比较常用的对抗单粒子效应特别是发生频率较高的SEU效应,主要有以下几种方法[7-8]。

3.1 整体屏蔽减少辐射

在电子设备的外面一般采用一定厚度的材料进行辐射屏蔽,屏蔽可以减少设备所受的辐射效应。不同的材料对不同的粒子有着不同的屏蔽性能,经常采用的材料有铝、铅、钽和某些酯类化合物等。整体屏蔽的办法在航天电子设备中使用较多,国内也进行了不少有关抗辐射材料的研究。

3.2 冗余设计

常用的应对单粒子翻转的技术是硬件冗余技术,可以将FPGA作为冗余的对象或者采用片内多模冗余。采用多片FPGA冗余有可能增加印制板布局布线的困难,增大设备的功耗、体积、重量等,片内冗余常用的三模冗余(TMR)是将电路三备份,利用设置在FPGA片内或片外的多数表决器对输出信号进行表决。它能容忍一个备份模块发生错误。虽然TMR带来了可靠性的提高,但是也会使模块的速度降低(有的甚至低到原来的80%),占用资源和功率增加(约为3.2倍)。所以设计时可以根据实际情况对关键部分使用部分3倍冗余法。

3.3 配置存储器的回读和重构

控制器负责从非易失大容量存储器中读取Xilinx FPGA的配置数据对其进行配置,然后在运行期间,对最容易受辐射效应影响的配置存储器按列进行读操作,然后与标准数据进行比对,一旦发现错误就进行重配置。另外,也可以通过对读回数据进行CRC校验来检验配置存储器是否出现错误。对配置存储器的读回校验和重配置(或局部重配置)是一种有效的抵抗辐射效应的方法。目前 NASA[9-10]、日本的 Smart Sat卫星工作组都在研究基于这种结构的卫星信号处理平台,国内某高校从2001年起也在对这种结构进行研究与应用,并取得了较大成效。本文设计的测试电路板也可以实现回读与重配置。

4 测试结果与分析

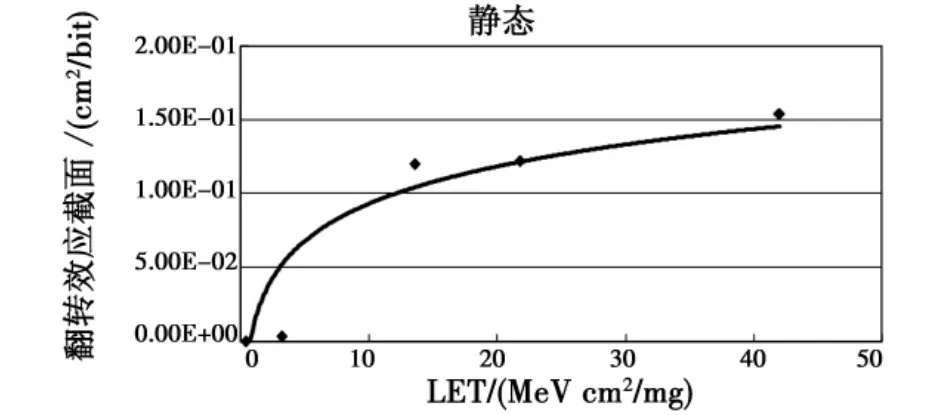

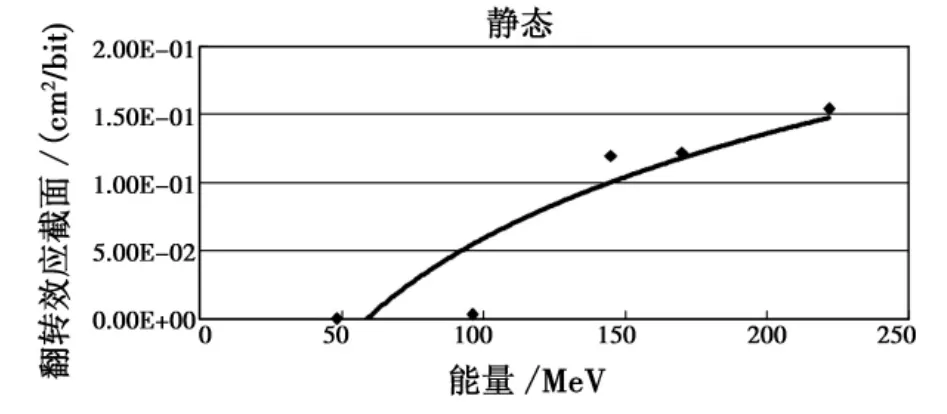

静态SEU测试,测试配置位的翻转敏感度。测试开始设置线性能量传递(LET)值为42 MeV cm2/mg,并逐渐被减少来观察发生翻转的极限值,最低的LET测试值是0.42 MeV cm2/mg。随SEU数量的累积,器件功耗电流随之增加,停止辐照,大电流状态保持,重配置后,电流值恢复到正常。图9显示了翻转效应截面与LET的关系,并进行了相似性拟合。图10显示了翻转效应截面与能量的关系。

图9 静态测试SEU与LET的关系Fig.9 Static test SEU cross section versus LET value

图10 静态测试SEU与能量的关系Fig.10 Static test SEU cross section versus energy

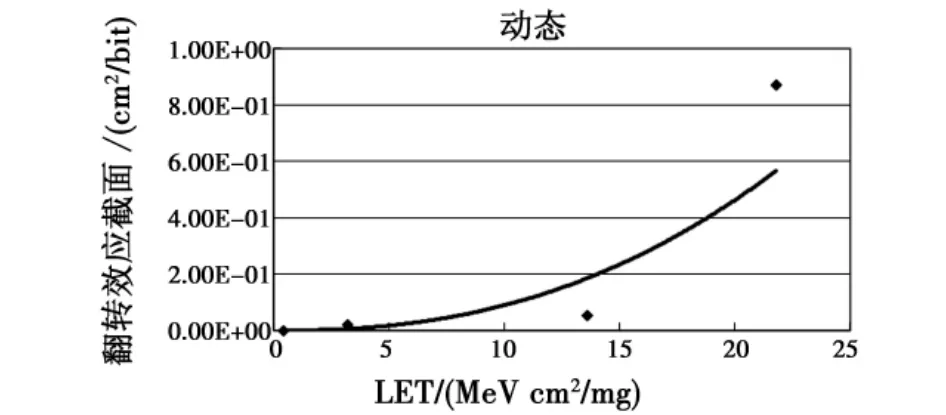

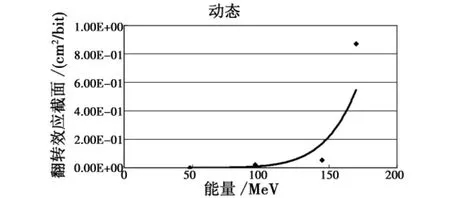

动态SEU测试,从试验现象观察,当注入量大于700 ion/cm2时,开始有翻转出现。当程序运行正常时,配置位有翻转,这显示了静态的翻转对动态有可能不起作用。随着注入量的增大,观察到了大量翻转,这种现象又包含了两种可能:一种是配置位翻转影响到动态测试;一种是用户逻辑的翻转。从试验现象分析得知,配置位的控制逻辑出错,导致了动态测试大量错误的出现。由于配置出错,因而试验中未曾得到BRAM和CLB翻转截面,但是从试验观察看BRAM和CLB对单粒子的敏感度远小于配置存储器。为了评估动态测试下配置存储器的敏感度,记录了动态测试下配置存储器SRAM的SEU截面与LET的关系,如图11所示。

图11 动态测试SEU与LET的关系Fig.11 Dynamic test SEU cross section versus LET value

SEU截面与能量的关系,如图12所示。由试验数据以及拟合所得到的走向趋势可以看出静态与动态下配置存储器SRAM的SEU截面与LET、能量的关系是呈现相反方向的。

图12 动态测试SEU与能量的关系Fig.12 Dynamic test SEU cross section versus energy

试验结果表明,SRAM型FPGA单粒子翻转敏感,同时存在单粒子功能中断,对于航天器控制系统等关键部位,应慎用SRAM型FPGA。若使用则需要相应的加固技术。

5 结束语

本文详细阐述了单粒子翻转的静态和动态的测试方法。静态测试的读回设计,采用了8位并行的SelectMAP接口,可以快速地读回配置数据。动态测试程序对所测对象的覆盖率可达90%,可以有效地评估其单粒子翻转的敏感度。此试验得到了动静态下SEU的翻转截面,对在地面上进行FPGA可靠性评估具有重要意义。另外文章结合工程实践给出了解决常见的辐射失效问题的方法,利用FPGA配置数据可读回的功能,系统可以应用在要求高可靠性的航天领域中,通过将FPGA的读回数据和原始配置数据进行比较,判断配置数据是否发生错误,若有错,则重新配置FPGA,这是一种抗单粒子翻转的有效措施,为进一步研究SRAM型FPGA辐照效应的机理和防护措施奠定了基础。

[1]姚志斌,何宝平,张凤祁,等.静态随机访问存储器型现场可编程门阵列辐照效应测试系统研制[J].强激光与粒子束,2009,21(5):749-755.

[2]冯彦君,华更新,刘淑芬.航天电子抗辐射研究综述[J].宇航学报,2007,28(5):1071-1080.

[3]FULLER E,CAFFREY M,SALAZAR A,et al.Radiation testing update,SEU mitigation,and availability analysis of the virtex FPGA for space reconfigurable computing[C]//IEEE Nuclear and Space Radiation Effects Conference,2000:30-41.

[4]Xilinx Inc.Virtex-II platform FPGA user guide[Z].UG002(V2.1)28 March 2007.

[5]YUI C C,SWIFT G M,CARMICHAEL C,et al.SEU mitigation testing of Xilinx Virtex II FPGAs[C]//IEEE Nuclear and Space Radiation Effects Conference,2003:92-97.

[6]赵又新.SRAM辐射效应测试装置的研制与应用[J].核电子学与探测术,2006,26(4):414-416,445.

[7]邢克飞,杨俊,季金明.空间辐射效应对SRAM型FPGA的影响[J].微电子学与计算机,2006,23(12):107-110.

[8]ALLEN G R,SWIFT G M.Single event effects test result for advanced field programmable gate arrays[C]//IEEE Radiation Effects Data Workshop,2006:115-120.

[9]HODSON R F,SOMERVILLL K,WILLIAMS J,et al.An architecture for reconfigurable computing in space[C]//Military and Aerospace Applications of Programmable Devices and Technologies Conference(MAPLD),2005:1-8.

[10]BERG M.Effectiveness of internal vs external SEU scrubbing mitigation strategies in a Xilinx FPGA:Design,test,and analysis[J].IEEE on Nuclear Science,2008,55(4):2259-2266.