基于数字锁相环的晶振频率同步模块设计

张嘉梁 ,王 剑

(1.电子科技大学 通信与信息工程学院,四川 成都611731;2.电子科技大学 通信抗干扰国家级重点实验室,四川 成都611731)

现有的射频频率源大多采用恒温晶振作为频标,以获得比较好的频率短期稳定度,但是恒温晶振的长期稳定度不能保证,存在累积误差,需要定期校准。本设计利用GPS秒脉冲没有累计误差的特点,通过测量本地晶振与GPS秒脉冲的频率以及相位误差,将误差进行卡尔曼滤波后送入PI调节器,并将得到的误差转为DAC的输入值来调整本地晶振的输出频率,从而获得一个长期与短期稳定度都很好的频标[1]。该模块的alce主要在FPGA内部实现,降低了规模,便于其集成于与其他通信、测量系统中。

1 系统设计

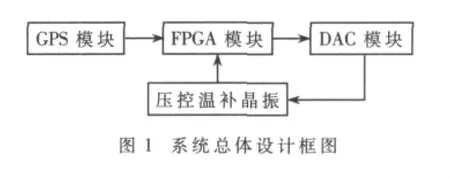

系统总体设计方案如图1所示,其中GPS接收模块可以输出由GPS信号中的秒脉冲信号。在FPGA模块中,实现了一个由计数器和数字延迟线构成的高精度鉴频鉴相器和一个由卡尔曼滤波以及PI控制器构成的数字环路滤波器。DAC模块将环路滤波器的输出转换为对晶振频率的控制量,从而构成一个数字锁相环。在环路锁定的情况下,本地振荡器的振荡频率即可与GPS星载原子钟保持严格同步。

2 电路设计

2.1 高精度鉴频鉴相器的设计

在传统的鉴相器设计中,通常只是利用一个计数器对输入信号进行计数,受到电路的工作频率限制,其精度大约在10 ns量级。由此产生的量化误差,将对系统的准确度造成很大影响。为了达到1e-10甚至更高的准确度,就需要提高时间测量的精度。在以往的设计中,通常采用专用TDC芯片测量,但其成本高,对PCB设计很敏感。为此,本系统在采用计数器进行粗测量的同时,利用Xilinx公司的FPGA内部的高速进位资源,构建了一个数字延迟线,实现了100 ps量级的细测量,即在FPGA内部实现了一个TDC单元,从而降低了频率量化对系统准确度的影响。另外,从相位噪声的角度分析,提高鉴相器的量化位数,也可以有效地降低量化噪声对系统相位噪声的影响。

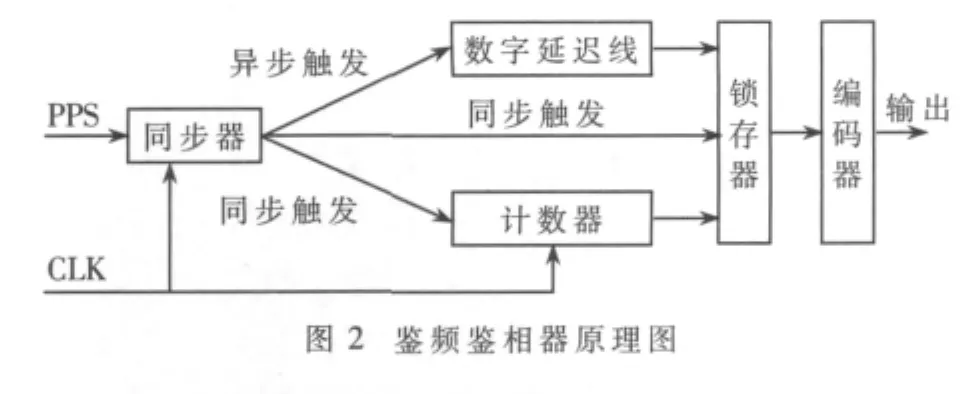

由于秒脉冲的时间相对测量精度比较长,为了实现大范围的测量,设计中采用了鉴频鉴相器测量GPS秒脉冲与本地振荡器的偏差。如图2所示,其中由100 MHz时钟驱动的粗计数器实现了频率的测量,而由数字延迟线构成的鉴相器,可以测量远小于一个时钟周期的相位误差。

如图2,同步器的功能是将异步的秒脉冲信号与时钟同步,作为计数器的同步置零输入,由两级D触发器的级联构成,用于保证时序裕量可以让潜在的亚稳态可能性降到最低,即保证当触发信号在时钟信号的保持建立窗口中到达时,可以让触发器有足够时间恢复到稳定状态。计数器为一个同步置零计数器。为了在大约1 s的时间内对100 MHz时钟进行计数,计数器的位宽被设计为 27 bit。

数字延迟线则是用于测量同步触发信号与异步秒脉冲之间的时间差,是本测量模块的关键。为了实现高精度时间测量,本系统采用了一种基于抽头延迟线的方法,其中延迟线由多个延迟单元组成,每个延迟单元都有相同的传输时延τ。通过采样初始脉冲在线路中传播时线路的状态,利用内插法,完成对两个触发脉冲时间间隔的测量,从而获得秒脉冲与本地振荡器的相位差。

在 FPGA中,有乘法器、比较器、加法器,可以将专用进位连线连接成进位链。由于加法器实现简单,可以清晰地显示出进位信号的逻辑关系。因此加法器是最适合实现延迟线内插器的方案。

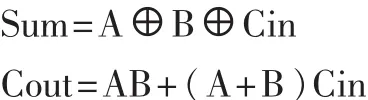

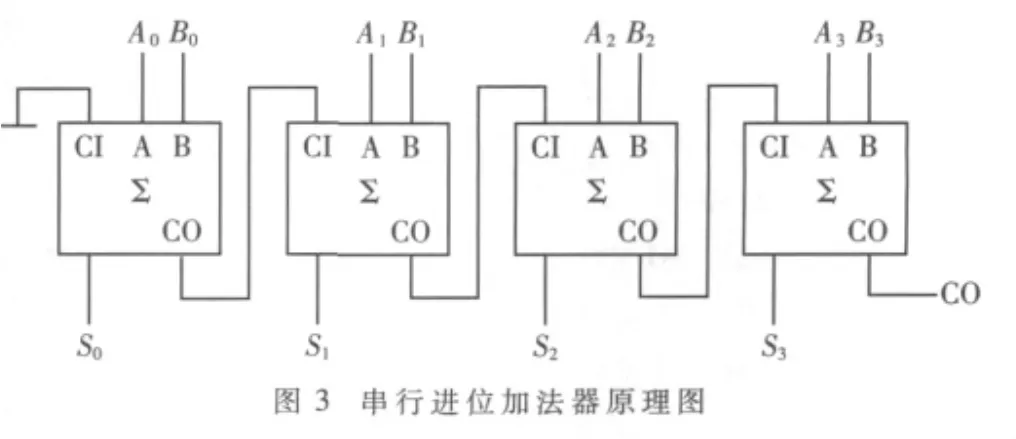

为实现对输入信号的时间内插,就需要使待测信号沿进位链传播。串行进位加法器的表达式如下:

如图3所示,设置输入A为全1,输入 B最低位为待测量信号,其余为0。当外部信号输入为0时,加数的最低位为0,所有输出都为1,进位链上没有信号。当外部输入变成1时,B的最低位变成1,这时最低位输出0,进位信号变为1,进入进位链传播。输入信号沿进位链传播的同时,也被逐级延时,这时,加法器的输出中0的个数,代表了输入信号经过的延迟单元的个数。这样,就实现了对输入信号的内插。

可以看出,从加法器的输出中可以获得需要的延迟信息,这就需要在加法器的输出端每一位后加一个锁存器,用以测量结束时保存进位链的状态。在本设计中锁存器的时钟端需要严格同步,这样采集到的信息才有意义,才能代表时间延迟信息。同时,在锁存器的时钟信号即结束信号的保持建立窗口中,加法器的输出会发生改变,会带来亚稳态的问题。为了解决这个问题,本设计在第一个锁存器之后又加入两个由工作时钟驱动的锁存器构成的同步器。

本设计中最关键之处是利用进位链实现延迟线的布局与布线。以 Spartan 3系列 FPGA为例[2],CLB是FPGA内的基本逻辑单元,每个CLB都包含一个可配置开关矩阵,此矩阵由4个输入、一些选型电路(多路复用器等)和触发器组成。 开关矩阵是高度灵活的,可以对其进行配置以便处理组合逻辑、移位寄存器或RAM。

一个CLB由4个相同的SLICE组成。SLICE中的进位逻辑包括一个进位专用多路复用器和一个进位专用异或门组成。 进位逻辑的延时在CLB中和相邻的CLB中都有专用连接,这些连接的延迟几乎为零。这就为利用进位链构成内插延迟线创造了条件。

在Spartan3系列FPGA中,CLB中的左侧两个SLICE的CIN/COUT直接与垂直相邻的CLB中左侧的两个SLICE的COUT/CIN相连,右侧亦然。以Spartan3系列的XC3S200FPGA为例,该FPGA共有24行20列共480个CLB,1 920个SLICE,故FPGA上在最大情况下共可配置40个96 bit的进位链。

经过实验,在ISE环境下直接调用加法器的IP核,并将XST综合选项设置为面积优先。在布局布线后用FPGA Editor检查底层结构,就可以得到理想中的内插器结构。经过MODELSIM后仿真,结果可以看出该延迟线是均匀的。在实际测试中,由于相邻的两个延迟单元可能会同时落入锁存器的保持建立窗口中,导致分辨率的降低,最终数字延迟线的分辨率约为200 ps。

最后,在同步触发信号到达时,锁存延迟线信息,就可以得到温度计码的结果,再经过优先编码以后,送出中断,通知 microBlaze读取结果。

2.2 环路滤波器

不同于一般ADPLL,由于GPS秒脉冲信号频率低、信号在传输中易受到干扰的特点,本系统不能使用通常的N-before-M等数字环路滤波器。

本系统采用的LEA-5S GPS模块输出的秒脉冲信号精度有效值为30 ns,99%精度小于60 ns。在进行滤波之前,首先要根据上文所述进行数据有效性判断,再进行数据合成(用本次计数器值为高位,内插器结果为低位,减去前一次内插器结果)以及硬限幅处理[3],将与理想秒脉冲相差过大的数据剔除后,将结果送入卡尔曼滤波器。

在滤波器设计上,采用了卡尔曼滤波+PI控制方法,有效滤除了噪声,减小了系统超调与震荡,同时将零差降到最小[4-5]。

卡尔曼滤波器是一个最优化自回归数据处理算法。卡尔曼滤波是一种递归的估计,利用获知上一采样状态的估计值以及当前状态的观测值就可以计算出当前状态的估计值,因此不需要记录观测或者估计的历史信息。相比FIR或滑动平均等滤波器,卡尔曼滤波可以节约大量的存储空间,更利于在低密度FPGA上的实现。

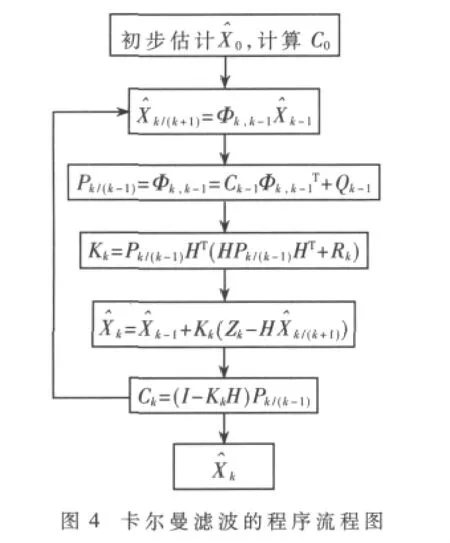

由于卡尔曼滤波需要大量矩阵运算,且需要浮点数来保持其精度以保证最后的收敛,同时,本系统对滤波计算的时间并非十分严格,故本系统中的卡尔曼滤波器在MicroBlaze核中利用C语言实现。KALMAN滤波流程图如图4所示。

在卡尔曼滤波中,动态系统维数、观测系统维数均设为1。同时,应对X0进行初步估计,可以使滤波器收敛速度加快。

滤波后得到当前时刻误差的估计值,将其送入PI模块。在锁相环系统设计中,通常在VCO外再添加一个积分项,来构成一个2类锁相环,以保证系统的收敛,同时消除零差[6]。在PI控制器整定的过程中,先调整比例系数,再调整积分系数,通过实验找出最优值。

2.3 DAC及晶振电路设计

本设计中,晶振选择的型号为TCEBBCS-10.000TCXO,其牵引范围为±8 ppm,在使用中能够基本满足要求,在未来,如将TCXO替换为OCXO,可以进一步提高系统的稳定度。另外可以选择牵引范围更窄的晶振,以进一步提高系统的最小分辨率。

在DAC选择上,需要满足低噪声的要求。本设计DAC选择16 bit高性能的AD5541,其采用R-2R结构设计,噪声可满足全16 bit精度输出,非缓冲输出可以直接驱动晶振的控制端。

3 测试结果及分析

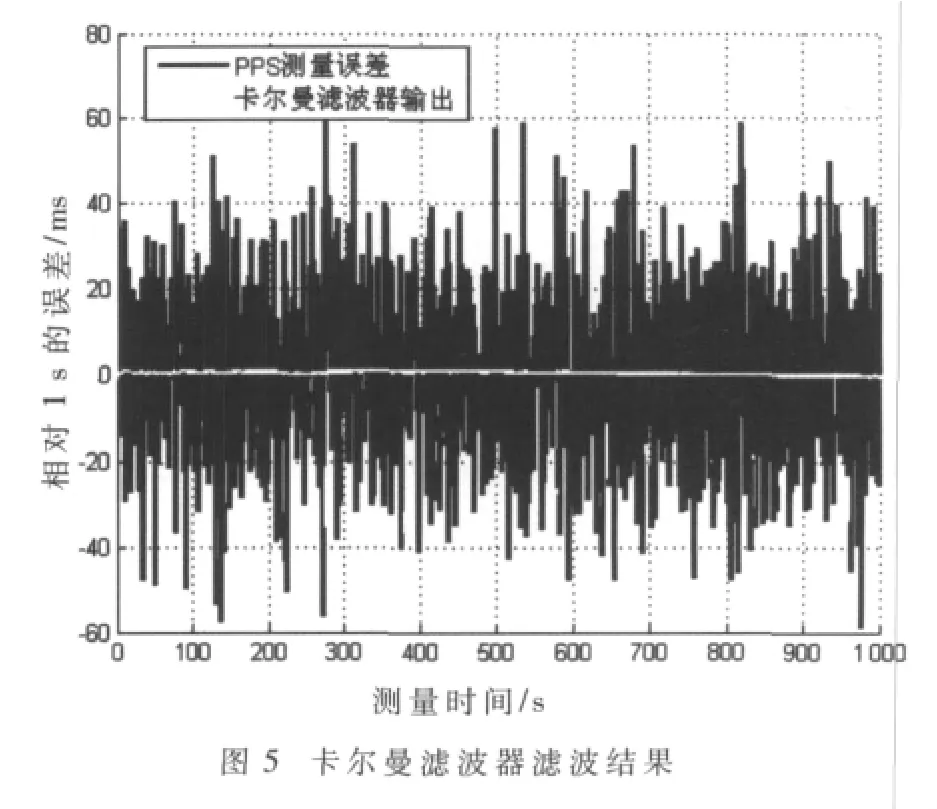

图5是利用CHIPSCOPE抓取的秒脉冲偏差与卡尔曼滤波后的结果。可以看出,卡尔曼滤波器对GPS信号的跳变有比较好的滤除作用。

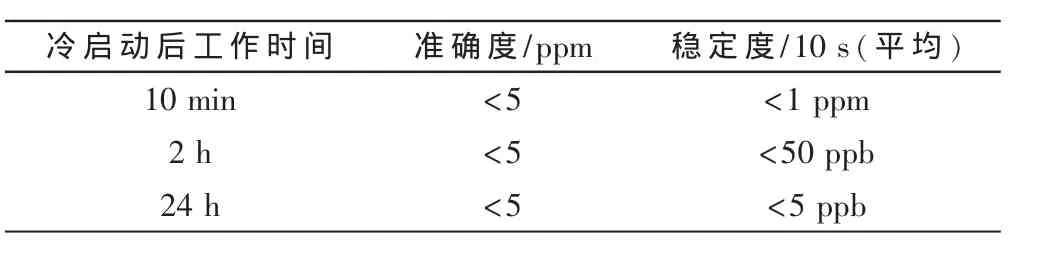

系统的测试结果如表1所示。

冷启动后工作时间10 min 2 h 24 h准确度/ppm<5<5<5稳定度/10 s(平均)<1 ppm<50 ppb<5 ppb

本文介绍的晶振频率同步系统,利用数字锁相环将晶振的输出频率同步于GPS星载时标,从而获得了一个高稳定度、高准确度的本地振荡器。其中,高分辨率数字鉴频鉴相器可以减小系统的量化误差,提高精度。环路滤波器中的卡尔曼滤波器可以很好地抑制GPS秒脉冲对系统造成的干扰。此外,系统的测量单元集成在FPGA之内,降低了系统的成本、体积,提高了稳定性。该系统可以广泛应用于通信网络、测试测量等各个领域,为其提供高质量免校准的频率基准。

[1]曾祥君,尹项根,林干,等.晶振信号同步 GPS信号产生高精度时钟的方法及实现[J].电力系统自动化,2003,27(8).

[2]Xilinx.Spartan-3 generation FPGA user guide.2010.

[3]党晓圆,单庆效,肖昌言,等.基于 GPS与北斗双模授时的压控晶振校频系统的研究与设计[J].计算机测量与控制,2009,17(11).

[4]Cui Baojian.An improved time synchronous system based on GPS disciplined rubidium[C].International Conference on Intelligent Computation Technology and Automation,2009,29.

[5]张莹,周渭,梁志荣.基于 GPS锁定高稳晶体振荡器技术研究[J].宇航计测技术,2005(2).

[6]FLOYD M G,姚剑清.锁相环技术(第 3 版)[M],北京:人民邮电出版社,2007.