FIR滤波器在扩频发射机中的应用

许瑞生,崔 琦

(中国电子科技集团公司第五十四研究所,河北石家庄050081)

0 引言

直接序列扩频系统抗干扰能力的获得是以扩展信号带宽为代价的,扩频信号产生的频谱旁瓣在通信中不再发挥作用,但其进入其他系统的工作带内,会作为噪声对邻近通道造成干扰。特别是在有多套系统兼容工作时,这种问题表现的就尤为突出。为了使得全系统兼容工作,必须设法滤除扩频信号的旁瓣,以消除对其他系统的影响。

早期的扩频系统,采用在基带信号扩频后采用低通滤波器或是声表面波滤波器的方式滤除基带信号的杂散信号,电路复杂且滤除效果不理想。数字化调制为现代扩频通信的发展趋势,随着大规模集成电路的发展,采用数字电路来实现FIR滤波器,可以很好地实现这一要求。FIR滤波器使用单一FPGA就可实现,且电路结构比较简单;在FPGA内部同时还可以在集成电路内部实现编码及电路扩频功能,使电路接口简化,电路集成度提高。

1 系统模型

为了避免信息传输过程中遭遇强信号干扰,同时增加频率利用率,系统通常都会设置许多频道可供选择。特别是在某些场合,要求多套系统同时工作,这就要求,即使相邻2个频道也会同时工作的通信要求,如图1所示。对于BPSK调制方式,为了保证信息的有效传输,通道带宽B必须大于或等于扩频码速率的2倍。假设相邻2个频道之间不会使用同一组频率,相邻2个频道的中心频率之间的差值Δf至少为每个频道所占用的带宽B。

图1 干扰频谱图

在常规直接序列扩频体制的通信中,如图1所示,2套系统工作于相邻的2个频道,每一套系统发射的扩频频谱的旁瓣都会落到另一套系统接收机的工作通道内,就造成了邻近通道干扰。

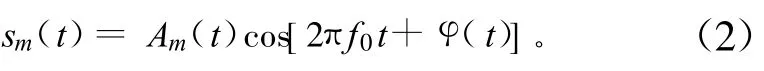

发射机采用CDMA调制方式工作。在CDMA系统中,N个用户分配N个PN码,这些PN码之间相互正交,使得任意2个不同的扩频码间的互相关等于0。即:

数据已调制信号与用户m的扩频信号gm(t)相乘,结果gm(t)sm(t)通过信道发送出去。同时其他用户也在发送各自的扩频信号。接收到的信号是各个用户发送信号的线性组合,表示为:

接收端要接收用户m的消息,且接收端生成的扩频码gm(t)与来自用户m的接收信号精确同步。接收过程是将式(3)的接收信号与gm(t)相乘,将其中的有用成分提取出来。由于实际应用的扩频码并不无限长,所有其函数并不完全正交,当正交性优于20dB时,可以认为能够满足CDMA工程需要。当干扰发射机距离较近,干扰信号的电平大于这个隔离度,就不能被忽略,严重时,系统之间根本无法工作。图1中正常工作的1频道所遭受到的2频道干扰,干扰比有用信号还要强30dB,系统必然不能正常工作。

2 FIR滤波器设计及仿真

由奈奎斯特(Nyqulst)第一准则可知,如果信号经传输后即使整个波形发生了变化,但是只要在其特定点的抽样位置的值保持不变,那么用再次抽样的方法仍可以保证准确无误地恢复原始信号。满足奈奎斯特第一准则的滤波器中,最常用的是升余弦滚降滤波器,该滤波器的冲激响应:

实际的通信系统中,应用的是平方根升余弦滚降频率响应:

式中,T为输入脉冲信号的周期,α为滚降系数,定义为:α=fα/f0;滚降系数越大,频谱在截至频率处越光滑,频带利用率越低[4]。

FIR数字滤波器存在N个抽头的h(n),N称为滤波器的阶数,其数学表达式为:

式中,x(n)为第n时刻的采样值,y(n)为滤波器输出;h(n)为FIR滤波器的第n级抽头系数。而输入数据x(n)可以采用B+1位补码来表示:

式(6)和式(7)两式累加,得到FIR滤波器输出的函数[3]:

数字滤波器采用升余弦(平方根升余弦)滚降形式,采用8倍的过采样处理后,实现低通滤波功能。

分布式算法的实现可以采用串行或并行的方式实现。串行方式数据的处理时间较长,但消耗的资源较少。并行方式可以大大提高运行速度,但要消耗大量的资源,采用串并行多级分布的方式折衷考虑,以期获得最佳的资源利用和运算速度。多级DA算法便是并行与串行方式的结合,将64个抽头的滤波器分成16级实现,每级4个抽头的运算都是串行方式实现,而16个分级之间则是同时运算互不干扰,从整体来说滤波器的16个分级间是并行运算。

图2 滤波器理想幅频特性图

根据所设计的FIR滤波器的参数指标,采用MATLAB仿真得到的滤波器理想幅频特性如图2所示。设计的FIR低通滤波器,截止频率为820kHz,输入数据为16位有符号数,抽头个数为64,输入数据时钟6.4MHz,位操作时钟为102.4MHz,即每输入一个16位有符号数都要利用24个位操作时钟通过DA算法完成滤波运算。若对64个抽头的输入直接采用DA算法,则查找表需要264个存储单元,采用分级DA算法,将63阶FIR滤波器分为16级实现,每级只有4个抽头,所以分级后只需要256个存储单元,等效为4096个存储位,大大节省了FPGA的资源。FIR滤波器的设计主芯片FPGA选用Altera公司的工业级EP2S60F672I4。编程环境为Quartus II,程序采用VHDL语言与原理图设计混合编写。高速数模变换(DAC)芯片采用AD9742。

3 试验验证及结果分析

发射机采用中频扩频方式,基带滤波采用64阶FIR滤波器,中频输出采用了声表面波滤波器完成谐波和远端的干扰信号抑制。

采用FIR滤波器后调制的中频输出频谱如图3所示。图中虚线为没有使用滤波器前的频谱输出。可以看出除了有用信号外,几乎看不到邻道干扰信号,说明FIR滤波器的效果十分明显。从图中可以看到中频输出只剩下扩展频谱的主瓣,而主瓣中所包含的扩频信息能量占调制总能量的90%以上,系统解调损耗(误码性能)约1dB左右,这是工程设计所允许的。

图3 中频输出频谱图

增加了FIR滤波器的发射机参加系统联试,在间隔10个频道情况下,没有受到任何干扰,已经超出前期没有FIR滤波器情况下的所有功能,各套通信系统功能正常,误码率没有收到任何影响。再进行相邻2个通道同时工作试验,依然没有受到干扰,2套通信系统工作正常,说明FIR滤波器在邻近通道的抑制方面效果明显。

传统的LC滤波器由于尺寸原因,阶数不可能做的太多,影响了滤波效果,通常使用的LC滤波器在邻近通道上的滤波效果只能达到20dB左右;采用FPGA器件,可以轻松地实现49阶[2]以上,甚至大于64阶FIR数字滤波器。采用64阶FIR数字滤波器带外抑制更是达到了60dB的理想效果。该试验采用了64阶的FIR数字滤波器来实现,而实现64阶FIR数字滤波器只是占用了采用FPGA器件极小的一部分资源,由于采用数字处理原理,它的插入损耗几乎为0,这也是传统LC滤波器无法想象的。

4 结束语

在数字化技术成为当今通信电路设计的趋势的情况下,基于FPGA电路,采用分布式算法的FIR滤波器,具有良好的滤波效果,对扩频发射机产生的扩频旁瓣有很好的抑制作用。采用FIR滤波器、调制器和信道编码于一体的FPGA设计,不仅可以简化电路的设计,提高系统的可靠性,更可以使得扩频系统具有更强的抗干扰能力。这种数字化电路的设计方式将在测控领域得到越来越广泛的应用。

[1]曹志刚,钱亚生.现代通信原理[M].北京:清华大学出版社,2000。

[2]刘庆良,卢荣军,李建清.FIR数字滤波器的FPGA实现研究[J].电子设计工程,2010,18(3):59-64.

[3]黄猛.基于自适应遗传算法FIR数字滤波器优化设计[J].现代电子技术,2010,33(2):143-146.

[4]黄其斌.无线信道数字传输系统分析设计[D].硕士学位论文.成都:电子科技大学.2003:5-7.

[5]高红涛.多进制扩频系统性能分析与仿真[J].无线电工程,2007,37(8):22-24.