IEEE 802.11n无线局域网中的多模交织研究与实现

张振东,吴 斌,朱勇旭,周玉梅

(中国科学院微电子研究所 北京 朝阳区 100029)

随着高清电视、视频、在线游戏等多媒体应用的发展,用户对无线局域网(WLAN)的数据吞吐率需求迅速增长。基于IEEE 802.11n协议的下一代WLAN通过采用正交频分复用(OFDM)、多输入多输出(M IMO)等技术提高系统吞吐率,物理层速率最高可达600 Mb/s[1]。在高速率的数字通信中,为了抵抗实际信道的记忆特性以及提高信道编码的纠错性能,通常对传输数据进行交织,以分散错误的突发结构[2]。交织对高吞吐率的WLAN系统实现空间分集和频率分集具有重要作用。文献[3]的仿真表明,在均方根延时扩展为75 ns的瑞利衰落信道下,采用QPSK调制和1/2码率的卷积码编码,误包率为1%时,系统利用交织器获得的增益大约为5 dB。

IEEE 802.11n协议中共定义了77种调制编码方式(MCS),包含36种不同的交织模式[1],在4×4的M IMO收发机中需要4个交织器与4个解交织器。文献[4-5]对WLAN系统中的交织算法进行了性能评估与改进,文献[6-8]介绍了802.11a/g协议中的交织硬件实现,但现有文献较少涉及如何设计适用于802.11n WLAN系统的高速度、低功耗的交织器与解交织器。本文通过分析802.11n协议中交织与解交织的置换规律,提出了一种支持该协议全部36种交织模式且交织与解交织复用的硬件结构。FPGA实现及ASIC综合仿真结果表明,本文的硬件结构相对于其他已有的设计在速度、硬件资源以及功耗等方面均有较优越的性能。

1 交织与解交织原理

IEEE 802.11n协议采用交织深度为一个OFDM符号编码比特数的块交织器,具有多置换特点,共进行3次数据置换[1]。第一次置换使相邻的比特映射到不相邻的数据子载波上;第二次置换使相邻的比特被交替映射到星座的高有效位和低有效位,以避免连续低可靠性比特的存在;第三次置换称为频率旋转,用于减小多天线相邻编码数据流比特之间的相关性。以k、I、j、r分别表示置换前以及经第一、二、三次置换后的数据顺序。置换规则分别定义为:

2 传统交织实现

交织与解交织的硬件实现主要有查表法和地址产生法两种。查表法实现的交织框图如图1所示[6],该方法将交织置换所需的地址序列预先通过置换公式计算出来,并存储于只读存储器(ROM)中,因而可适用于各种复杂的、多置换的交织器设计。然而,802.11n协议中的交织共有36种模式,在最高4×4的M IMO收发机中若交织与解交织采用查表法实现,则需要680 960 bit的ROM以及10 368 bit的随机存储器(RAM),如此大的存储资源开销不利于系统大规模集成。

地址产生法实现的交织框图如图2所示,该方法通过设计智能地址产生单元产生置换所需的地址序列,因而相对于查表法能够大大减小存储资源开销。但是,从置换定义式(1)~式(6)可以看出,直接数学计算产生交织地址序列需进行大量的乘法、除法以及取模运算。为了降低复杂度以及缩短地址产生单元中的关键路径,文献[7-8]采用级联单置换交织方式实现多置换交织。该级联方式需进行多次数据写、读操作,将增加一定的RAM开销,特别是将增大交织过程的延时。802.11n协议中的交织需进行3次不同的置换,采用级联方式将使系统的整体延时难以满足媒体接入控制层中确认包短帧间间隙的定时需求。

图2 地址产生法实现的交织框图

3 多模复用交织结构

从上述讨论可知,IEEE 802.11n协议中交织实现的关键问题是如何在不增加延时的情况下有效产生交织置换所需的地址序列,以及如何尽可能减少M IMO收发机中多个交织器与解交织器的总硬件开销。对此,本文提出3种技术相结合的方法:合并3次置换为一次写、读数据操作;利用低硬件复杂度的电路代替数学计算产生多模地址及复用交织与解交织。

3.1 3次置换合并

通常,交织写地址产生单元产生置换式(1)~式(3)所定义的地址序列,读地址产生单元产生顺序地址[9]。但通过Matlab工具分析置换公式在不同模式下的置换操作发现:可以先将顺序地址作为写地址将数据依次写入置换矩阵,然后以解交织置换式(4)~式(6)定义的序列作为读地址来实现交织。对于交织中的任一单独的置换,该等效变换的实现方式均成立。比如,交织中第一次置换的直接实现是利用式(1)定义的序列作为写地址,以顺序地址作为读地址。根据上述变换方法该置换也可以利用顺序地址作为写地址,以式(6)定义的序列作为读地址来实现。从而每一种置换均有两种实现方案,增加了多置换交织硬件实现的灵活性,也使置换合并成为可能。

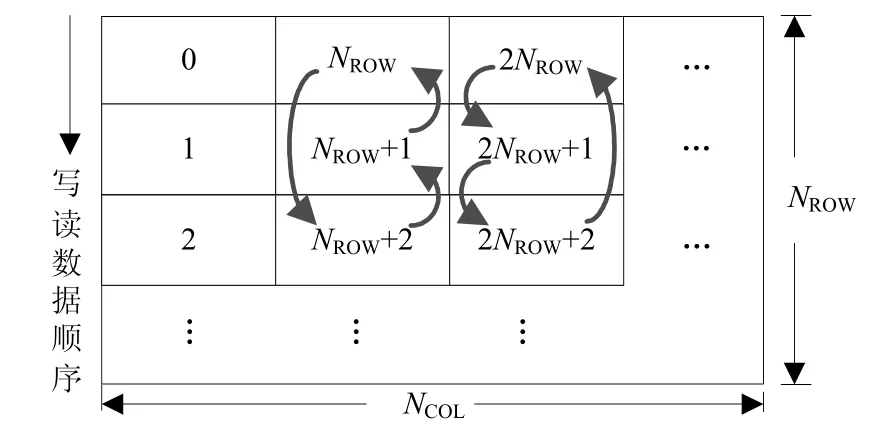

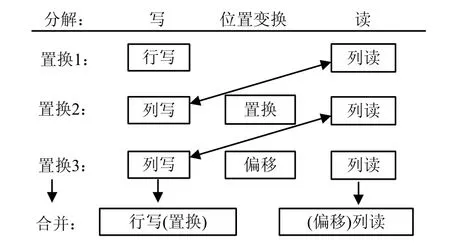

置换合并的原理是首先将多置换交织中各单独的置换分解为行或列方向的写操作、数据位置的变换,以及行或列方向的读操作3个步骤;然后通过去除相邻置换间冗余的行或列方向的写、读操作减少数据的写、读次数。IEEE 802.11n协议中,交织第一次置换可进行如图3所示的分解,数据先从水平箭头所指的行方向依次写入置换矩阵,然后从列方向依次将数据读出(即式(6)定义的序列)。图4给出了第二次数据置换的分解,数据先从左侧箭头所指列方向依次写入置换矩阵;然后按图中弧形箭头所指方式将相应位置的数据交换,最后再从列方向依次将数据读出。图4中显示的弧形箭头方向表示数据采用64QAM调制时的位置变换方式,当为16QAM调制时,数据仅在偶数列变换位置,当为QPSK或BPSK调制时,数据无位置变换。交织中第三次置换的分解如图5所示,数据先按箭头所指列方向依次将数据写入置换矩阵;然后部分数据从矩阵的末列移出至首列;最后从图中左侧箭头所指列方向将数据读出。

图3 第一次数据置换操作分解

图4 第二次数据置换操作分解

图5 第三次数据置换操作分解

依照上述置换分解,可进行如图6所示的置换合并。图中双向箭头所指的操作即为重复冗余的写、读操作,在实现中可以去除。第二次置换分解中的数据位置变换可合并在行方向的写地址中实现,第三次置换分解中的数据位置变换可通过偏移列方向的读首地址实现。因而硬件实现只需一次数据写、读,消除了传统级联方式产生的延时并使存储开销为级联方式的1/3。

图6 置换合并原理示意图

3.2 地址产生电路设计

针对置换合并后的地址产生,提出优化电路以代替复杂的公式计算。该电路利用数据位置置换的循环特性消除写、读地址产生所需的所有乘法、除法以及取模运算。写地址产生电路如图7所示,图中包含4个选择开关、一个计数器、一个加法器以及少量的寄存器。合并置换后行方向的写地址通过基址(addr_base_w)加偏移址(const_offset)的方法实现。偏移址用于实现第二次置换分解中的数据位置变换,不同映射模式下偏移址的大小通过设置行、列方向的循环移位寄存器唯一确定。采用64QAM调制方式时,写地址中位置变换的最小循环单元为采用图4所示的9宫格,需设置的行、列循环移位寄存器长度各为3 bit,图中分别标记为row_flag_64qam及col_flag_64qam。采用16QAM调制方式时,数据仅在偶数列变换位置,行、列循环移位寄存器长度各为2 bit,图中分别标记为row_flag_16qam及col_flag_16qam。采用QPSK与BPSK调制方式时,数据无位置变换则相应的偏移址为零。

图7 合并置换后写地址产生电路

图8所示为读地址产生电路结构,合并置换后列方向的读地址通过当前地址(addr_r)加置换矩阵的列值(NCOL)实现。当一整列地址产生后,当前地址赋值为列基址(col_base_r)的值,列基址表示当前地址所在矩阵列的位置。该电路结构简单,只需预先将各模式的读首地址(addr_ini)及读首地址所在的列位置(col_ini)存储在一个小的常量查找表中。

图8 合并置换后读地址产生电路

3.3 交织与解交织复用

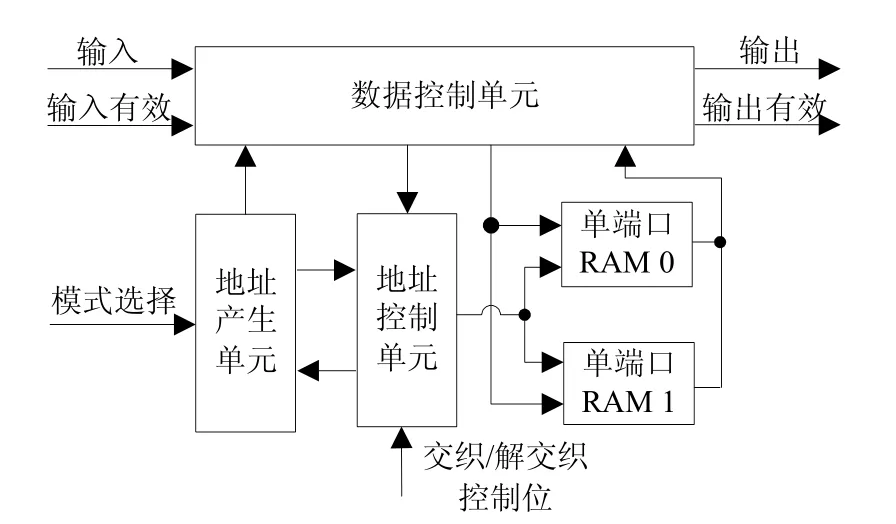

图9 交织与解交织复用的结构框图

由于交织与解交织为互逆的置换过程,通过交换交织的写、读地址便可实现相应模式的解交织。在实际的WLAN收发机中,数据的收、发始终为时分操作(即交织与解交织始终不会同时工作),采用如图9所示的交织与解交织复用结构可进一步减少系统的硬件开销。该结构主要由4个部分组成:1) 地址产生单元,产生前述置换合并后的写、读地址;2) 地址控制单元,根据交织/解交织控制位产生相应的地址请求信号,从而实现模块的交织功能与解交织功能切换;3) 数据控制单元,控制输入输出数据的时序;4) 单端口RAM 0以及单端口RAM 1,实现数据乒乓连续处理。图10给出了复用后的交织解交织模块在收发机中的集成方式。通过该方式最终可使收发机中交织器与解交织器的总数减少为独立设计的1/2。

图10 交织与解交织模块在收发机中的集成

4 FPGA实现及ASIC综合仿真结果

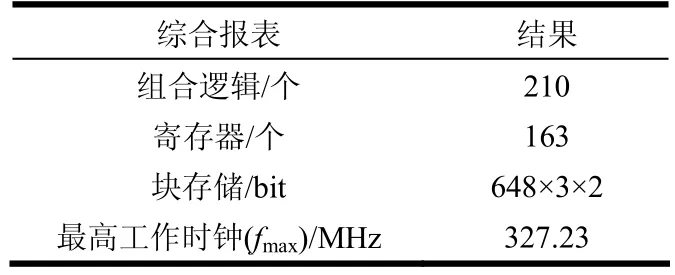

本文设计采用Verilog HDL描述。首先,使用ModelSim仿真工具进行功能验证,当输入相同的测试向量时,在802.11n协议定义的36种交织模式下硬件电路的仿真输出结果均与直接通过定义公式计算的输出结果一致;然后,对设计进行FPGA综合并将其加入到课题组开发的基于FPGA的802.11n原型系统中进行系统级验证,Litepoint公司生产的专用WLAN测试设备IQ n×n能够正确解调原型系统发射的数据帧,进一步说明了设计的正确性。表1给出了本文设计在QuartusⅡ 8.0中使用StratixⅡEP2S60F672C3器件综合的结果。

表1 FPGA综合结果

表2 本文设计的ASIC实现与部分已有设计对比

FPGA验证通过后,在SM IC 0.13 µm 1P6M CMOS工艺下采用Design Compiler对设计进行ASIC综合。布局布线完成后,使用Prime Time与VCS工具分别对设计进行时序分析和功能验证。最后,根据VCS仿真工具记录的电路翻转信息采用Prime Power对其进行功耗分析。表2列出了本文设计与部分已有设计的各项参数对比。本文设计写、读地址产生电路的关键路径上仅包含一个加法器和两个级联的多路选择开关,因而相对文献[10-14]的设计具有最高的工作频率。综合考虑工艺与数据位宽的不同以及是否支持数据连续流水处理,本文设计在面积与功耗方面同样具有较优越的性能。

5 结束语

IEEE 802.11n协议的产品设计及算法理论研究已成为产业与学术界的关注热点,高速度、低功耗、多模式的交织器与解交织器是WLAN收发机中的重要组成部分。多模复用交织结构有效解决了802.11n M IMO收发机中交织与解交织硬件开销大、多模地址产生困难的问题,克服了传统实现方法的不足。此外,IEEE 802.11a/g、802.16d/e及HiperLAN/2等协议均采用与802.11n前两次置换规则相同的块交织器,因而该结构同样能够应用于基于上述各协议的通信系统中,具有较好的参考和实用价值。

[1] IEEE LAN/MAN Standards Comm ittee. P802.11n D6.00 part11: w ireless LAN medium accessc control (MAC) and physical layer (PHY) specifications[S]. New York: IEEE Press, 2008.

[2] ANDREAS F. Wireless communications[M]. New York:Wiley-IEEE Press, 2005.

[3] TERRY J, HEISKALA J. OFDM w ireless LANs: a theoretical and practical guide[M]. Indianapolis: SAMS Press, 2002.

[4] WANG X F, SHAYAN Y R, ZENG M. On the code and interleaver design of broadband OFDM systems[J]. IEEE Communications Letters, 2004, 8(11): 653-655.

[5] NIU H N, OUYANG X M, CHIU N. Interleaver design for M IMO-OFDM based w ireless LAN[C]//IEEE Wireless Communication and Networking Conference. Las Vegas,NV: IEEE Press, 2006: 1825-1829.

[6] TELL E, LIU D. A hardware architecture for a multi mode block interleaver[C]//International Conference on Circuits and Systems for Communications. Moscow: IEEE Press,2004.

[7] WU Y W, TING P, MA H P. A high speed interleaver for emerging w ireless communications[C]//IEEE International Conference on Wireless Networks, Communications and Mobile Computing. Maui, HI: IEEE Press, 2005: 1192-1197.

[8] DANILIN A, SAW ITZKI S, RIJSHOUWER E, et al.Reconfigurable cell architecture for multi-standard interleaving and deinterleaving in digital communication systems[C]//International Conference on Field Programmable Logic and Applications. Heidelberg: IEEE Press, 2008: 527-530.

[9] YU C, YEN M H, HSIUNG P A, et al. Design of a high-speed block interleaving/deinterleaving architecture for w ireless communication applications[C]//IEEE International Conference on Consumer Electronics. Las Vegas, NV: IEEE Press, 2009: 1-2.

[10] MARTINA M, NICOLA M, MASERA G. Hardware design of a low complexity, parallel interleaver for WiMax duo-binary turbo decoding[J]. IEEE Communications Letters, 2008, 12(11): 846-848.

[11] TROYA A, MAHARATNA K, KRSTIC M, et al. Lowpower VLSI implementation of the inner receiver for OFDM-based WLAN systems[J]. IEEE Transactions on Circuits and Systems, 2008, 55(3): 672-686.

[12] CARLOS R, PARRA-M ICHEL R, RENTERIA G. Design and implementation of a multi-standard interleaver for 802.11a, 802.11n, 802.16e&DVB standards[C]//International Conference on Reconfigurable Computing and FPGAs. Cancun: IEEE Press, 2008: 379-384.

[13] IACONO D L, RONCHI M, TORRE L, et al.M IMO-OFDM physical layer real-time prototyping[C]//IEEE Wireless Communication and Networking Conference. Las Vegas, NV: IEEE Press, 2008:18-23.

[14] ASGHAR R, LIU D. Low complexity hardware interleaver for M IMO-OFDM based w ireless LAN[C]//IEEE International Symposium on Circuits and Systems. Taipei:IEEE Press, 2009: 1747-1750.

编 辑 张 俊