片上网络:新一代的片上系统结构*

刘炎华,刘 静,赖宗声

(华东师范大学 微电子电路与系统研究所,上海 200062)

片上网络:新一代的片上系统结构*

刘炎华,刘 静,赖宗声

(华东师范大学 微电子电路与系统研究所,上海 200062)

片上系统是使用共享或专用总线作为芯片的通信资源。由于这些总线具有一定的限制,因此扩展性较差,不能满足发展需求。在这种情况下,目前的片内互连结构将成为多核芯片的发展瓶颈。文章介绍了一种新型的片上体系结构(片上网络)来解决未来片上系统中总线所带来的不足。片上网络作为一种新的片上体系结构,可以解决片上系统设计中所带来的各种挑战,受到了学术界和工业界的广泛重视。片上网络的研究涉及体系结构、设计方法以及设计工具等诸多方面,文章从体系结构的角度对片上网络研究中的关键问题作了简单介绍。

片上系统;片上网络;体系结构

1 引言

微电子技术发展的理论基础是19世纪末到20世纪30年代期间建立起来的现代物理学。从1947第一支半导体晶体管的发明,到1958年采用硅平面工艺的集成电路诞生,直到目前正在发展中的SoC,半导体集成电路一直遵循摩尔定律的预言高速发展着。半导体发展速度为人类历史上所罕见,仅近40年来,单个芯片上集成的晶体管数目就增加了数百万倍。正是源于这种高速发展,使得移动电话、彩色电视机、数码相机、个人电脑、互连网络等高科技全面进入了寻常百姓家,迅速改变了人类的生产模式、文化娱乐和生活方式。

从设计的角度来看,一个SoC可以被认为是“一个将多个独立的超大规模集成电路拼接在一起从而提供一个完整应用功能的电路。”当设计SoC时,SOC供应商除了可以调用来自内部设计的内核库以外,还可以使用由外部设计者所提供内核库。内核基本上是预先设计好的具有复杂功能的模块,这些模块称为知识产权模块(IP Model),虚拟元件(VC)或简单的一些宏。由于SoC中的核来自不同来提供商,因此SoC内部是多样的,这是使得设计过程变得复杂的一个关键因素。

总线结构是SoC的主要特征。总线由于结构简单而被广泛运用。然而随着工艺技术的持续发展,总线渐渐无法满足芯片对性能的新要求,其主要表现在以下几个方面:

(1)扩展性差;

(2)线通信效率低;

(3)单一时钟同步问题。

因而,2000年左右几个研究小组提出了一种全新的集成电路体系结构—片上网络(Network on Chip),其核心思想是将计算机网络技术移植到芯片设计中来,从体系结构上彻底解决总线架构带来的问题。

2 NOC结构

2.1 NOC基本体系结构

片上网络(NoC)第一次将计算机网络的技术引入到芯片设计中,从体系结构上彻底地解决这些瓶颈问题[1,2]。NoC从本质上来说就是一个基于网络通信的多处理器片上系统,它主要由计算节点和通信节点两部分组成。通信节点主要由路由器组成,计算节点通过路由器加以网络协议从而规范实现片上资源的互连和通信,这些互连资源包括CPU、DPS、视频流处理器以及I/O接口等。NoC经过几年的发展,已经出现了多种架构方案,其中kumar提出的二维规则型网络(2D Mesh),因其结构简单、容易分析和布局等优点,已经成为了研究的热点[3]。图1是一个典型的2D Mesh结构的NoC示意图。

从图1我们可以看出,计算节点rn通过网络适配单元NI和负责计算节点之间信息交换的通信节点Sn来实现数据交换。图1给出的4×4的2D Mesh 结构包含了一个NoC 基本组成,该结构没有采用总线和专用点对点的链路,而采用了一般网格拓扑结构,通过一定的路由算法可以实现任意两个计算节点之间的通信,可采用包交换、电路交换或其他的路由方式,可使用同步、异步或其他逻辑实现。

对于一个NoC来说,常见的片上路由器结构如图2所示。由于片上路由器的缓存(buffer)限制以及NoC对信息延迟的要求,因此虫孔交换[4]是一种比较适合NoC信息交换的方式。

2.2 NoC层次结构

NoC借鉴OSI网络模型中的分层思想,每一层和相邻层之间都有数据接口,较低层通过接口向上一层提供服务,服务的实现细节是对上层屏蔽的。较高层又是在较低层提供的低级服务的基础上实现更高级的服务。一般来说,各层的主要功能都是由NoC中的网络适配单元来实现。关于NoC 层次结构在不同的NoC 实现中有不同的描述,各层的功能略有差异,各层的名称和数目也不尽相同。图3给出的NoC中各层次的结构,每个层次都对应着NoC 的不同研究问题[5,6~9]。

3 NOC关键问题

3.1 NoC拓扑结构

NoC的拓扑结构反映了NoC中各节点在芯片中如何分布和连接。由于通信需求约束、各计算节点的面积、芯片封装形式等因素的不同,采用NoC体系结构时,设计者需要根据实际情况采用不同类型的拓扑结构。在选择拓扑结构的时候,设计者主要应该考虑两个因素:通信负载较重的计算节点之间应该尽可能靠近;NoC使用片内布线资源作为通信信道,因此节点之间的连接不能太复杂,且要具有可扩展性。

目前来说,常见的二维片上网络拓扑结构主要有以下几种:

(1)蜂窝结构(Honeyeomb)

蜂窝结构如图4所示,计算节点和通信节点的比例为3∶1,每个计算节点与三个计算节点以及一个通信节点相连接,每个通信节点与六个计算节点以及六个通信节点相连。相对于其他拓扑结构,其连线资源比较紧张。图4中白色模块代表计算节点,黑色模块代表路由节点。

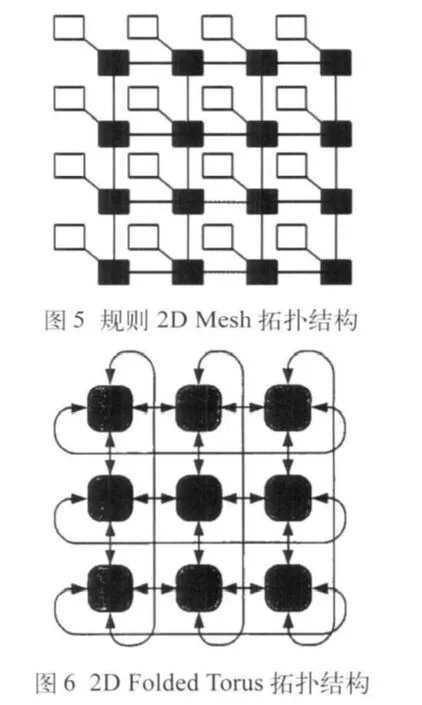

(2)规则的二维网状网络(Regular 2D Mesh)

规则的二维网状网络是目前设计者最常用的拓扑结构,如图5所示。每一个计算节点与一个通信节点相连,而一个通信节点与四个相邻的通信节点相连;通信节点实现路由的功能,并作为每个相邻的计算节点的网络接口。

(3)二维折叠环(2D Folded Torus)

2001年6月,斯坦福大学的W.J.Daly提出使用片上互连网络通过数据包通信的方式替代各式各样的连线结构的构想,并提出了二维折叠环的拓扑结构,如图6所示。与二维网状网络相比,它将处于边界的通信节点也连接起来,使所有的通信节点成为一个环路,这样可提供更多的路由选择。但是从图6中也可以看到,由于环路与环路之间有交叉的地方,这样不可避免地在物理实现时需要更多的版图布线资源[10]。

由于三维片上结构的技术发展,已经有学者提出了三维的片上结构,三维的片上网络可提供更高效的数据通信。

3.2 路由策略

路由是确定一个数据从源节点到目的节点的发送机制。NoC中的路由算法确定如何为每个数据包建立下一条要执行的路径,即路由算法决定数据包从源节点开始选择哪一条路径到达目的节点。所以,路由算法对NoC网络性能的好坏是至关重要的。路由算法可以分为:确定性路由(Deterministic Routing)和自适应路由(Adaptive Routing)。

NoC主要的确定性路由算法有源路由算法和XY路由算法。源路由算法是由源节点指定包到目的节点的路由;XY路由算法将数据包首先在X方向进行传输,然后在Y方向进行传输到达目的地。它是一种无死锁、确定性和基于源地址的路由算法。XY路由算法能在负载较轻和负载均匀的条件下,比较稳定地工作,但在负载加重时,NoC的性能会变得很差。文献[11]针对XY路由在负载加重时,性能变差这一缺点提出改用一种自适应路由模式。在负载较轻和负载均匀的条件下采用XY路由模式,在负载加重时采用自适应路由模式,这路由算法称为DyAD Routing。自适应路由涉及动态分布机制,它能根据局部链路拥塞的情况,很好地适应网络状态的变化,是具有一定容错功能的网络路由算法。例如,网络中某节点不可用(故障)时,包就绕开该节点,沿着其他的路径传输,但自适应路由算法实现复杂、开销大,不适合在芯片上实现。

NoC中的路由算法应该能有效地解决活锁、饥饿以及死锁的问题。活锁:当一个包在它的目的地环绕但无法到达目的节点时就发生了活锁,该问题存在于非最短路由算法中。饥饿:使用不同优先级可能出现高优先级的包始终占用资源,而一些低优先级的包永远不能到达其目的地,发生饥饿现象,使用公平路由算法或为低优先级的包预留一些资源可避免饥饿现象。死锁:当两个包彼此等待路由转发时,由于保留了部分资源并等待对方释放资源,因此产生死锁,死锁是由资源的独占性引起的。

3.3 交换技术

交换技术是按照某种方式动态地分配传输线路和接口资源的规则。NoC中的基本交换技术,包括:存储转发交换、虚拟直通交换技术(Virtual Cut-Through)和虫孔交换技术 (Wormhole Routing)[12]。

(1)存储转发交换:在计算机网络中,这是最流行的分组交换技术。采用存储转发交换,整个数据包的一部分将存放在接收路由器中,直到接收路由器接收到整个数据包后,它才将数据包提交给下一个在路由路径上的路由器。在这路由机制下,每个路由器都需要有充足的缓冲空间,以存放整个数据包。对于大的数据包而言,这种方法将会引入额外的数据包传输延迟。由于缓冲资源相当昂贵,除此以外,存储转发交换需要消耗更多的功耗和面积,因此不适合作为NoC的路由交换技术。

(2)虚拟直通交换:这种技术可以减少由于存储转发交换所引起的数据包延迟。在这种路由机制下,路由器不存储整个数据包,数据包被当前路由器接收后可以马上转向下一个路由器。但是,如果下一个路由器无法使用,那么,当前路由器,将以完整的形式存储待发数据包。在吞吐量相同的情况下,虚拟直通交换机制的能耗低于存储转发交换。

(3)虫孔交换:这种交换机制是为并行处理器而开发的。虫洞流程控制能够实现较小的Buffer和较短时间的路由延迟。在虫孔交换中,信息包被划分成更小的流控单元(flit)。flit以流水线的方式进行路由,可明显减少通信延迟。第一个flit通常被称为头flit,头flit中包含了路由信息,当头flit由于网络竞争产生堵塞后,后续的flit将停止在各自所在的路由节点,因此各路由节点只需要很小的缓存就可以满足存储的需要。从而减少了路由器中缓存空间的需求。

通过比较了三个流行的交换技术后,可以很容易的看出,虫孔交换是片上网络的最佳选择:虫孔交换使网络延迟对路径长度不那么敏感。通常延迟由两部分组成:一部分是发送数据包的时间,另一部分是各个节点寻径时间的总和。在实际应用中,一般数据包的长度比较大,且远远大于各个节点寻径时间的总和,虫孔交换的网络延迟主要由数据包发送时间来决定,因此采用虫孔路由的片上网络更易升级。同时虫孔路由只需要很少的路由器缓存,这一点也很好的迎合了NoC的特点。因此目前的大部分片上网络交换技术都是采用了虫孔路由技术。

片上网络成为了解决日益复杂的SoC设计问题最有前景的方法之一,目前NoC的研究除了集中在上述几个方面外,还包括了NoC的服务质量(QoS)以及它的软件模型(software model)等。

4 小结

本文所讨论的问题只是 NoC设计中的一部分,具体实现一个 NoC的时候,从物理层到系统层,从软件到硬件,NoC涉及的方方面面远远多于本文所讨论的问题。虽然NoC的潜力是巨大的,但在实现一些关键技术之前:如可靠的NoC结构、高质量的服务保证和可行的软件模型,它将还无法应用到实际设计中去。因此NoC这个领域,还有很多值得研究的地方。

[1]L.Benini, G.De Micheli.Networks on chips: A new SoC Paradigm [J].IEEE Computer Magazine, 2002, 35(1):70-78.

[2]W.J.Dally, B.Towles.Route packets,not wires:on-chip interconnection networks[A].Proc.Design Auto- mation Conf[C],2001,684-689.

[3]Kumar S,J ant sch A,Soininen J,et al.A Network on Chip Architecture and Design Methodology [A].Proc- eedings of IEEE Computer Society Annual Symposium on VLSI[C], 2002,105-112.

[4]L.M.Ni and P.K.McKinley.A survey of wormhole routing techniques in direct networks [J].Computer, 1993, 26(2):62-76.

[5]http:// www.st.com/[EB/OL].

[6]Dally W J, Towles B.Principles and Practices of Interconnection Networks [M]. Morgan Kaufmann, 2004.

[7]Bjerregaard T,Mahadevan S.A survey of research and practices of network-on-chip[C].ACM Computing Surveys,2006 , 38(1) :1-54

[8]Dehyadgari M,Nickray M, Afzali2kusha A, et al. A New Protocol Stack Model for Network on Chip[C]. In: Proceedings of the 2006 Emerging VLSI Technologies and Architectures (ISVLSI’ 06), IEEE, 2006, p2

[9]Kumar S, J ant sch A, Soininen J-P, et al. A network on chip architecture and design met hodology. In: Proc. Int’s Symp.VLSI (ISVLSI), 2002. 117-124

[10]W.J.Dally and C.L.Seitz, The Torus Routing ChiP[J].Technieal RePort 5208:TR:86,ComPuter Seienee De Pt,California Inst.Of Technology,1986:1-19.

[11]Dehyadgari M,Nickray M,Afzali - kusha A,et al. Evaluation of pseudo adaptive XY routing using an object oriented model for NoC [C]//The 17th International Conference on Microelectronics. Iran:Tehran University,2005:204-208

[12]Ye T, Benini L, De Micheli G.Packetization and routing analysis of on chip multiprocessor networks[J]. Journal of Systems Architecture,2004,50(223):81-104.

NoC: A New Architecture for System on Chip

LIU Yan-hua, LIU Jing, LAI Zong-sheng

(Institute of Microelectronics Circuit & System, East China Normal University,Shanghai200062,China)

The shared or dedicated buses are used in System on Chip(SoC)to interconnect the communicating on-chip resources. But, these buses can not be scalable beyond a certain limit. In this case, the current interconnect infrastructure will become a bottleneck for the development of multi IP chip. In this paper, we will introduce a new design paradigm (Networks on Chip) that has been proposed to counter the inefficiency of buses in future SoC. NoC as a new architecture on chip, can be a solution for the challenges of SoC design and has been

recognition by academe and industry. The research for NoC involves many problems such as system architecture, design methodology, design tools and so on.In this paper, we simply discuss the key problems for NoC from the view of system architecture.

System on Chip(SoC); Network on Chip(NoC); system architecture

TN701

A

1681-1070(2011)05-0023-05

2011-04-02

江苏省专用集成电路设计重点实验室开放课题基金资助项目(JSICK0801)

刘炎华(1980—),男,江苏南通人,博士研究生,主研方向为高性能SoC/NoC体系结构设计及测试。

微电子制造与可靠性