六角形超结VDMOS器件的终端结构设计

孙华芳,荆吉利,孙伟锋

(东南大学国家专用集成电路系统工程技术研究中心,南京 210096)

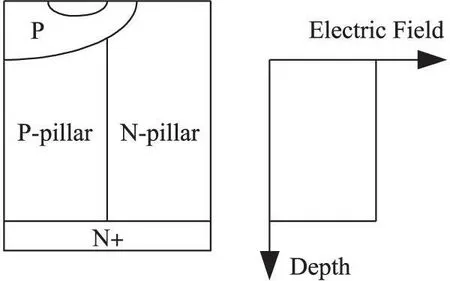

在大力发展节约能源,动态控制,噪音减少等技术的今天,电力电子半导体器件由于其具有精度高,速度快和功耗低的特点而得到了在功率电子系统的广泛应用。为了降低功耗,要求功率半导体器件在断态时能承受较高的电压,在通态时有较低的导通电阻。而超结的概念正是基于上述原因提出的。超结MOS的结构和电场分布如图1所示。它的临界电场没有传统MOSFET那样的大斜率,几乎为恒定值,这就使得击穿电压仅仅依赖于漂移区的厚度,而与掺杂浓度无关,从而导通电阻与击穿电压的关系得到很大改进,由传统的平方关系变为线性关系,这使得超结器件具有更加优越的性能和特点[1~3]。高压功率器件通常会受到结曲率效应的影响导致电场在结附近聚集,因此可以利用场限环,场板等技术来避免终端结的曲率效应[4~6]。随着超结器件的发展,超结的终端技术问题也随之产生。本文针对六角形晶格单元结构的超结VDMOS器件的终端技术进行了研究,设计了600 V超结VDMOS器件所需要的终端结构、工艺等参数。

图1 超结MOSFET的器件结构和电场分布

1 超结终端技术原理

由于平面结终端弯曲造成的局部场强增高,以及热氧化使表面区域杂质浓度升高使平面结的终端区电场强度远高于体内,使得pn结表面附近以及pn结弯曲处的击穿电压比平行平面结的击穿电压低,出现了结终端表面提前击穿的现象。传统结构的终端技术中,为了使主结弯曲处的电场积聚作用被削弱,通常采用了场限环,场板等技术,击穿电压因此得到提高。而超结器件中的终端技术不仅要考虑主结弯曲处的电场分布,还必须考虑终端区纵向的电场分布,如果不考虑这一点,终端区的击穿电压可能比有源区的要低很多[7]。因此,超结器件终端的设计比一般功率器件要有更多的考虑。

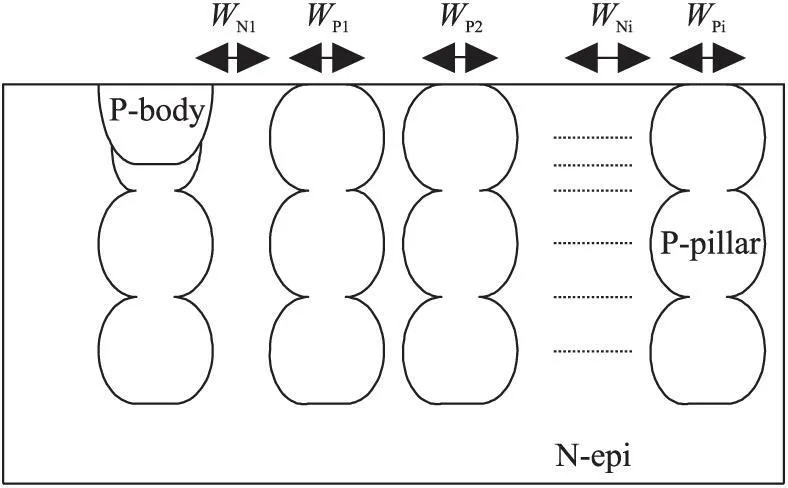

利用相互交叠的P柱和N柱构成可以实现超结VDMOS终端结构,如图2 所示。其中P柱的宽度为Wpi, NA是P柱的掺杂浓度。 N柱的宽度为WNi, ND是N柱的掺杂浓度。

图2 一个带有终端的原胞结构

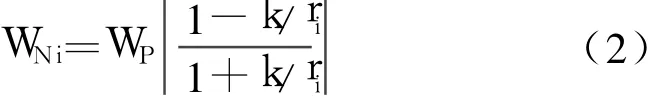

终端结构中,每一个P柱和N柱都形成一个超结,对终端结构上的第i个PN结——PiNi结进行独立的分析, PiNi结的宽度为WPi到WNi之间的距离,即WPi+WNi。 PiNi结的宽度总有WPi+WNi<ri成立,对于高压器件随着i的增加, WPi+WNi≪ri, PiNi结的电荷面密度可近似表示为:

方程(1)中有四个参数是需要我们确定的。另外,在原胞部分, N柱和P柱的掺杂浓度应相等。离子注入的工艺过程应在原胞和终端区同时完成,所以N柱和P柱的浓度也近似相等。为了节省工艺成本,终端结构下的P柱的宽度也应相等即公用一块光刻板。于是就有NPi=NNi=Nc, WP1=WP2=…WPi=WP, WNi可由下式表示:

其中

由(2)式可以知道, WNi仅与ri有关, Wp, k为常量。随着ri的增加, WNi随之增加, 并且逐渐满足WPi+WNi≪ri。但需要注意的是不管WNi怎样增加,都要满足WNi<WP。 WNi随着ri增加而增加并且保持WNi<WP,便可以满足式(2)。这也就意味着终端结构中N柱的宽度要从原胞区的边界到终端区不断增大,而P柱的宽度却是固定不变的。

利用上述超结器件终端技术的原理,文献[7]已经通过模拟得到了 600 V超结 VDMOS的终端结构。

2 六角形晶格终端结构设计

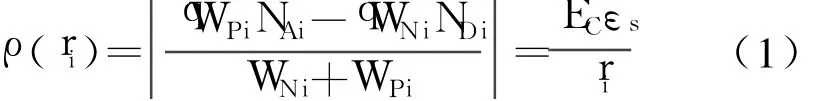

超结结构有许多形式的晶格单元,四种常用的晶格单元形式有:叉指式,六角形,方形和格子形晶格单元。虽然各种晶格单元在形式上有很大差异,我们根据实际应用的需要可以采用不同的晶格单元,但是原理都是一样的,即利用电荷补偿效应降低电场峰值提高耐压的同时减小导通电阻。在器件的宽深比较小时,有源区的形状对超结结构的影响已不是主要因素,补偿效果最差的叉指式原胞晶格和补偿效果最好的六角形原胞晶格的优化结果相差已不是很大。当器件的宽深比较大时,六角形原胞晶格的优势就显现出来了。而且随着宽深比的增加,优势更明显[8]。考虑到常用的宽深比下,六角形原胞晶格的设计结果确实是最好的。六角形原胞晶格的结构如图3所示。

图3 六角形有源区晶格的示意图

在六角形晶格的终端部分,如果P柱之间的位置关系满足式(2),会使终端部分的六角形晶格版图的排列不均匀,导致击穿在终端提前发生。为了使终端不提前击穿,终端P柱和N柱的宽度就必须要比有源区P柱和N柱的宽度小。这就使有源区和终端区之间的六角形版图排列形状不规则,出现了有源区和终端之间的电荷不平衡,使击穿电压下降。为此在六角形的排列晶格结构中,采用的处理方法是使有源区和终端区的六角形原胞晶格形状相同,终端P柱和N柱的宽度均为有源区原胞晶格的一半,使击穿可能会发生在终端区域与有源区之间的版图不规则的地方而不是终端的位置。尽管六角形有源区的原胞晶格设计结果是最好的,但是六角形有源区的原胞晶格版图排列的不规则使得超结VDMOS的击穿位置常常发生在有源区和终端之间的区域,但这也是不可避免的。由于P柱和N柱的宽度越小,就越容易耗尽,因此击穿电压随着P柱和N柱的宽度的减小而增加。设计的版图排列如图4所示。图4中,每一个六角形便构成了一个晶格单元,在六角形的中心位置有一个圆形,它代表了P柱,晶格单元较大的是有源区,较小的位置是终端单元。

图4 六角形原胞及终端结构版图

在有源区域和终端区域之间存在一个过渡区,如图所示的与终端区相邻的六角形形状已经被终端的六角形形状所破坏,变得不再规则;因此它的有源区和终端区之间的过渡区存在电荷不平衡的现象。

当有源区P柱和N柱区的宽度确定后,再确定耐压所需要的终端横向长度就可以了。终端横向长度与P柱的个数有关。

3 仿真结果讨论

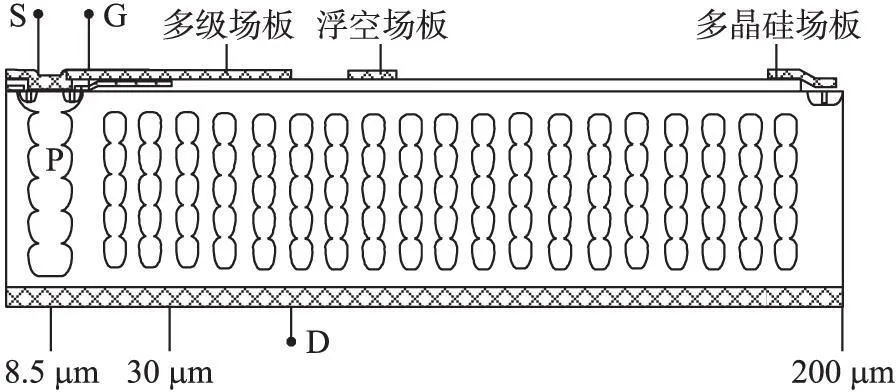

以600 V六角形晶格单元的超结VDMOS为例,设计它的终端部分。图5是六角形的终端区域示意图,在如图所示的场板结构中,使用了与主结相连的金属场板和多晶硅场板结合的多级场板,与截止环相连接的多晶硅场板,以及浮空场板。其中多级场板使主结渐渐耗尽并且耗尽层向外侧扩展,由于在多级场板的边缘位置与硅之间电位差很大,所以多级场板边缘处出现一个峰值电场;为了减小多级场板末端的峰值电场,可以在末端附近的位置增加浮空场板,调整多级场板末端与浮空场板之间距离的大小可以减小级场板末端峰值电场。

图5 六角形终端结构示意图

由于六角形的终端区域P柱的宽度是有源区域P柱宽度的一半,当有源区P柱和N柱区的宽度确定后,确定600 V所需要的终端横向长度就可以了。终端横向长度与P柱的个数有关,在P柱宽度和N柱宽度均确定的情况下,仅需确定P柱的个数。在六角形的有源区内P柱和N柱的宽度都是7.5 μm,六角形的终端区域内P柱和N柱的宽度是有源区原胞晶格的一半,故取3.75 μm。终端区域内P柱的个数和击穿电压的关系如图6所示,要达到600 V的击穿击穿电压, P柱的数量要在18个以上。

图6 终端区域内P柱的个数和击穿电压的关系

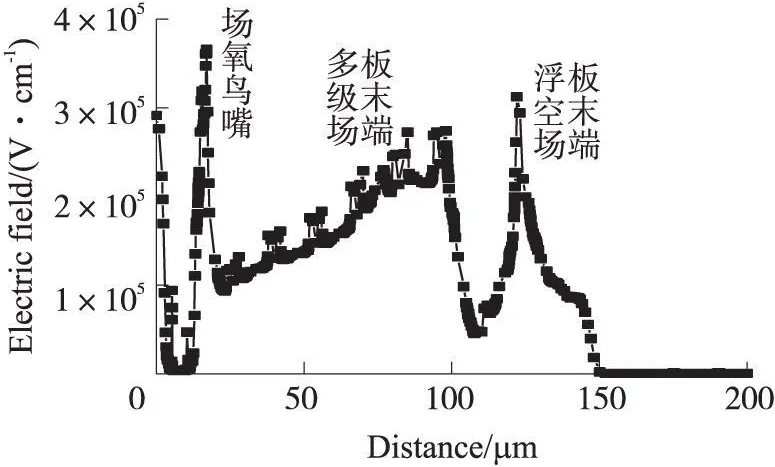

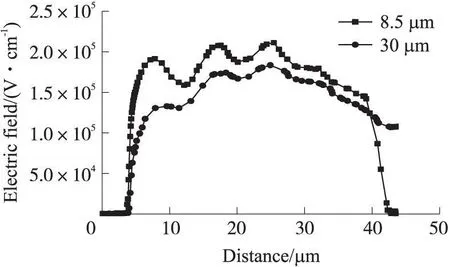

表面电场,表面电势的分布情况分别如图7, 8所示。在图7中发现表面电场从左到右出现了3个峰值电场,它们分别在场氧鸟嘴,多级场板末端及浮空场板末端。在这3个峰值电场附近表面电势上升的很快,如图8所示。在图9中,垂直电场在有源区域(x=8.5 μm)和终端区域(x=30 μm)都呈矩形分布,电荷达到平衡,从而达到最高的击穿电压。

图7 表面电场分布

图8 表面电势分布

图9 在水平位置x=8.5 μm和30 μm的纵向电场线

4 结论

功率器件设计中要考虑原胞和终端两个部分。对于终端设计,应该使表面的电场峰值转移到体内,避免在较低电压下终端提前发生击穿。六角形超结VDMOS有源区原胞晶格的电荷补偿效果是最好的,但如果它的终端设计按照其它晶格单元设计方法一致,会使终端部分的六角形晶格版图的排列不均匀,导致击穿在终端提前发生。为此提出了一种与有源区相似的六角形终端结构,终端P柱和N柱的宽度均为有源区原胞晶格的一半,使击穿可能会发生在终端区域与有源区之间的版图不规则的地方而不是终端的位置。

[ 1] Wataru Saito, Ichiro Omura, SatoshiA ida, etal.High Breakdown Voltage(>1 000 V)Semi-Superjunction MOSFETs Using 600 V Class Superjunction MOSFET Process[ J] .Electron Devices,2005, 52(10):2317-2322.

[ 2] Yu Chen, Yung C Liang, Ganesh S Samudra.Procession of Superjunction Power MOSFET Devices[ C] //IEEE Industrial Electronics Society, 2007:1380-1385.

[ 3] Zing RP.On the Specific on-Resistance ofHigh-Voltageand Power Devices[ J] .Electron Devices, 2004, 51(3):492-499.

[ 4] Evgueniy Stefanov, Georges Charitat, Luis Bailon.Design Methodology and Simulation Tool for Floating Ring Termination Technique[J].Solid-State Electronics, 1998, 42(12):2251-2257.

[ 5] Yo Han Kim, Han Sin Lee, Sin Su Kyung, et al.A New Edge Termination Technique to Improve Voltage BlockingCapability and Reliability of Field limiting Ring for Power Devices[C] //Integrated Circuit Design and Technology and Tutorial, 2008:71-74.

[ 6] Liao CN, Chien F T, Tsai Y T.Potential and Electric Field Distribution Analysisof Field LimitingRing and Field Plate by Device Simulator[C] //Power Electronicsand Drive System, 2007:451-455.

[ 7] 荆吉利,孙伟锋.超结MOSFET的终端技术分析[ J] .固体电子学研究与进展, 2009, 24(4):25-30.

[ 8]Chen X B.Optim ization of the Specific On-Resistance of the COOLMOS[ J] .IEEE Trans.Electron Devices, 2001, 48(2):344-348.