一种高动态性能数字DC-DC算法建模与芯片设计*

周浬皋,李冬梅

1.清华大学微电子学研究所, 北京100084;

2.清华大学电子工程系, 北京100084

手机、掌上电脑、MP4等多媒体设备需要精度高且稳定的供电,因此会配有专门的电源管理芯片。降压型DC-DC是电源芯片当中的主要模块,它将随不稳定的电池电压转换成基带芯片所要求的电压,并且在负载变化的情况下依旧能保持电压稳定。本文采用了一种新的结构,对反馈系统进行了优化,并以手机基带供电为背景,提出指标,完成仿真和芯片设计。

文章第1部分简单介绍降压型DC-DC的工作原理和重要组成模块;第2 部分描述算法设计的思路,接下来的第3部分介绍如何用硬件实现算法构想;最后给出了仿真结果、分析和结论。

1 工作原理

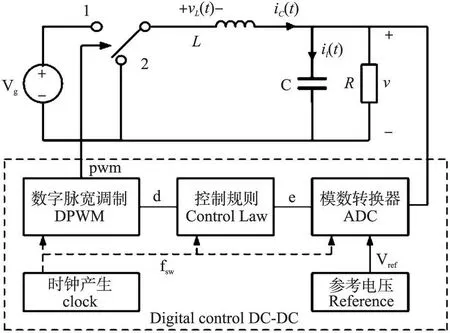

降压型DC-DC的组成如图1所示,虚线框以上为功率电路部分,它将电源电压转换成负载所要求的电压,虚线框内是反馈控制部分,它将输出电压稳定在要求范围内,使其不随电源电压、负载大小的变化而变化。其原理是利用反馈系统,对输出电压进行检测,并通过补偿算法来调整输出脉冲的占空比,从而控制1、2开关的通断时间,继而控制输出电压。公式表示中, D代表输出脉宽的占空比[1]:

图1 数字降压型DC-DC原理[2]

以手机基带芯片供电这一应用为例, Vg代表手机电池,其输出电压变化范围为2.4 V到3.3 V。R相当于基带芯片负载,它是一个随时变化的量。输出电压V则是芯片所获得的电压。虚线框内为数字校正部分,它由模数转换器、补偿算法、数字脉冲宽度调制器三部分组成。

2 算法分析

2.1 直接数字法介绍[ 3 ~5]

对于数字控制系统,通常有两种建模的办法:数字映射法和直接数字法。数字映射法是指先在模拟域内考虑补偿函数,然后再将其转化为数字信号来处理;直接数字法是将所有的模拟模块全部建模成数字信号,直接在数字域里面寻找补偿函数。数字映射法可以将模拟算法映射为数字算法,这样可以利用模拟电路的丰富积累。但如果考虑功率转换电路的相位裕度和带宽,以及负载的瞬态响应,直接数字法是有优势的。一来它是在一个更保守的环境下设计系统,这样提高了设计的可靠性;二来直接数字法能够更方便的控制阶跃响应的波形。

2.2 系统建模[ 6]

功率电路的传输函数为:

利用直接数字法,将整个系统进行数字建模。先假定整个环路的延迟为一个周期,并且考虑DPWM的零阶抽样保持。

2.3 补偿函数的寻找

对于BULK电路,在0 db时,相位为-180°,其相位裕度接近于零,见图2。系统不稳定,须引入补偿算法。

图2 BULK电路开环波特图

设补偿算法的传输函数为C(z),系统开环传递函数为Hop,闭环传递函数为Hcl。

设补偿函数具有如下形势:

需要根据G(z)的特点,并且结合数字电路的可实现性,来确定补偿函数零极点的个数和位置,从而使得闭环系统有良好的阶跃响应。

传统的方法是采用零极点相消,得到一个相位裕度足够的开环波特图,从而判断其阶跃响应。但这种方法对阶跃响应的过冲、稳定时间的控制并不直观。而利用MATLAB,在根轨迹中粗调补偿零极点的位置,并且对开环波特图进行细调,从而能够更直接的控制阶跃响应的波形,也提高了对波形精度的控制能力,使它更能贴近需求[7]。所得补偿函数如下[8]:

2.4 周期个数对动态性能的影响

前面在建立系统函数的时候,假定系统在一个周期内能完成反馈。而通常的情况是输出电压经过模数转换器需要一个周期,算法需要一个周期,脉宽调制器也可能增加一个周期。每增加一个周期,系统的相位裕度就会变差一些。对Z域而言,每多一个周期,就多了一个极点,这样使得补偿难度更大,阶跃响应的动态性能更差。

表1对比了在此系统环境下,环路不同周期的延迟对阶跃响应造成的影响。可以看出,周期的减少对动态性能与稳定性能均有较大的影响。因此本文尝试用一个周期完成整个反馈过程。

表1 周期与阶跃的关系

3 电路的实现

若要一个周期完成整个反馈运算,那么数模转换与补偿算法要在一个周期内完成,并且在下一个周期开始的那一刻,脉冲宽度调制器置为高电平,且输出有效脉宽。系统的工作频率为1 MHz,时序安排如图3所示。

图3 系统时序分配

3.1 ADC的设计

对于数字降压型DC-DC而言,为使得输出纹波较低(低于8 mV),同时又不出现极限环效应, ADC的最低有效位LSB的选取应该满足如下关系:

其中Vr为最小输出纹波, LSB为ADC最小采样精度,最左边的表达式是指输出电压的最小调节精度, n是指pwm的位数。结合电路指标, ADC的LSB选择为5 mV。

在DC-DC的设计中,转换效率是很重要的指标,因此ADC的功耗不能太大。同时,由于时序的要求,需要ADC在不到一个周期的时间内产生输出。结合这些特点, ADC采用如图4所示的结构[9]:

图4 ADC的结构

左边MOS开关与采样电容、高增益运放构成一个采样保持电路,其指标为50 ns内建立到0.1%,因此运放的增益要求为70 dB,带宽为150 MHz。右边是一个低压VCO[10-11],其中心频点约在1.25 V附近。此部分电路完成了对Vo信号的采样,后面接计数器,将模拟量数字化,并完成校正和做差。

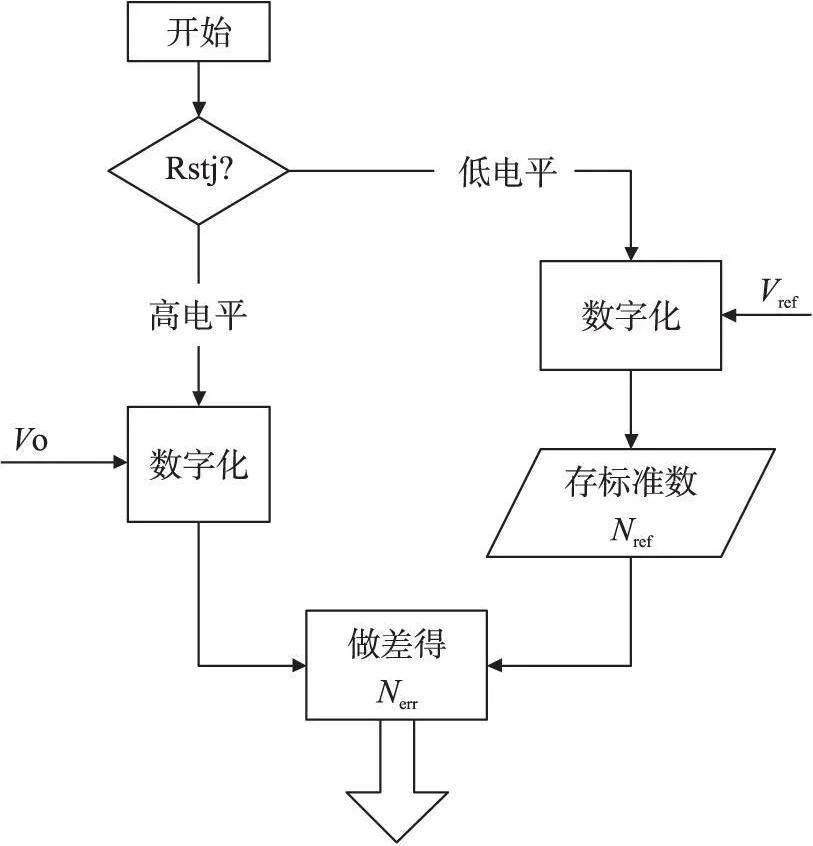

整个ADC的工作原理是,前50 ns采样,然后用450 ns让VCO起振,计数器记下VCO的震荡个数,然后与预置的标准数做差,从而得出Vo与Vref误差的数字输出,见图5 。

图5 ADC的算法

3.2 算法的设计

在任何闭环系统的设计当中,开环增益是极其重要的参数,它直接影响反馈系统的稳定性以及建立精度。在DC-DC设计当中,最难的问题是确定系统的开环增益。整个环路中包括开关、ADC、PWM等模块,因此不能简单的认为补偿函数与功率函数的总增益便是开环增益。目前尚没有精确的理论分析来给出开环增益的推导过程,只好另辟途径,采用测试的办法。

在整个系统搭建起来之后,将系统在Vo与ADC的连接处断开,并设补偿函数的增益为1。在ADC的输入端加入一个合适的电压差量,并测量输出Vo的值,相比得到的增益,便是算法增益归一时的环路增益。将算法增益代入,便能得到整个系统的开环增益。

考虑一个周期的延迟,将补偿函数转化为差分方程:

3.3 DPWM的设计

这里需要一个10位的数字脉冲调制器(DPWM),脉宽的变化范围是0 ns到1 023 ns,每个数值对应1 ns。传统的结构是用32个的延迟单元构成低5位的延迟,然后再用一个5位的计数器,来实现高5位的延迟[12]。考虑功耗、面积等因素,本文依然沿用这一结构,但这一结构由于包含了丰富的数字电路,而脉宽最小单位为1 ns,因此容易产生竞争,尤其是在极小或极大输出脉宽的情况下, RS触发器无法正常启动或复位,从而导致输出脉宽产生根本性的误差[13]。

考虑到输出电压一般是稳定在Vref附近,因此占空比在Vref/Vo附近的精度要求是最高的,而对于两个极端情况,其精度对系统的影响可以忽略。因此,在算法部分,将容易使DPWM产生冲突的数值滤除掉,从而在不影响系统性能的情况下,极大的增加了系统的稳定性[14]。

4 结果分析

图6所示是芯片的后仿结果,由图可知,当负载从50 mA跳变到800 mA时,电路能够在140 μs内稳定到1.25 V附近,纹波不超过5 mV,稳定的精度能达到0.5%。

图6 仿真结果

实际电路仿真已取得良好的动态性能以及较高的建立精度,但与系统函数的仿真结果仍有少许差距:在负载跳变时,会出现短时间的震荡。这主要是因为,在将系统数字化实现时,出现了参数量化、有限字长、高阶极限环等效应的影响[15]。若要减少这些效应的影响,需要增加量化的精度,乘法器的位数等,这样系统芯片的面积、功耗等开销会有所增加。在实际应用中,可以根据情况进行折中。

[ 1] RobertW Erickson, Dragan Maksimovic.Fundamentals of Power Electronics SECOND EDITION[ M] .Page(s), 37-61.

[ 2] 孟浩.数字控制DC-DC开关电源研究[ D] .清华大学硕士学位论文, 2007.

[ 3]Peng H, Prodic A.Modeling of Quantization Effects in Digitally Controlled DC-DCConverters[ J] .IEEE Transactionson Power Electronics, 22(1):208-215.

[ 4] Lukic Z, Rahman N.MultibitΣ– PWM Digital Controller IC for DC-DCConverters Operating at Switching Frequencies beyond 10MH[ J].IEEE Transactions on Power Electronics, 22(5):1693-1707.

[ 5] A larcon E, Pao L.Proximate Time-Optimal Digital Control for DCDCConverters For Peer Review[ J] .IEEE Transactions on Power ElectronicsManuscript ID:TPEL-2007-07-0343 Manuscript Type:Regular Paper.

[ 6] Trevisan D, PMattavelli.Digital ControlofSingle-InductorMultiple-Output Step-Down DC–DCConverters in CCM.IEEE Transactions on Industrial Electronics, 55(9):3476-3483.

[ 7]Franklin G F, Powell JD, Workman M.Digital Control of Dynamic Systems[ M] .北京,清华大学出版社, 2001, 222-238.

[ 8] Bryant B, Kazimierczuk M.Voltage Loop ofBoost PWM DC-DCConverterswith Peak Current-Mode Control[ J].IEEE Transactions on Circuits and Systems Part 1:Regular Papers, 53(1):99-105.

[ 9] Chui Martin YeungKei, Ki W ingHung, Tsui ChiY ing.An Integrated Digital Controller for DC-DCSwitching Converterwith Dual-Band Switching[ C] //2003 Svmposium on VLSl Circuits Digest of Technical Papers.

[ 10] Straayer M, Perrott M.A 12-Bit, 10-MHz Bandwidth, Continuous-Time SigmaDelta ADC with a 5-Bit, 950-MS/s VCOBased Quantizer.IEEE Journal of Solid-State Circuits, 43(4):805-814.

[ 11] Wei P, Min P.Design of New CMOSQuadrature VCO[ J] .Chinese Journal of Electron Devices.

[ 12] Abram Dancy, Anantha Chandrakasan.A Reconfigurable Dual Output Low Power Digital PWM Power Converter[ J] .Low Power Electronics and Design, 1998, Page(s):191-196.

[ 13] Choe S, Ahn J.Dynam ic Simulator for a PEM Fuel Cell System with a PWM DC/DC Converter[ J] .IEEE Transactions on Energy Conversion, 23(2):669.

[ 14] Lukic Z, Wang K.Multibit 6 0 1 PWM Digital Controller IC for DC-DC Converters Operating at Switching Frequencies Beyond 10 MHz[ J] .IEEE Trans.Power Electron.22(5):1693-1707.

[ 15] 程佩青.数字信号处理教程(第二版)[M].北京:清华大学出版社, 2004, 392-440.