串行可编程多路数字PWM发生器设计

戈 亮

(上海船舶运输科学研究所研究开发中心,上海200135)

0 引 言

脉宽调制技术是一种对模拟信号电平进行数字编码的技术,最早应用于通信技术领域。随着科学技术的发展,现已广泛应用在电力、电子、微型计算机、自动控制等多个学科领域,并逐渐成为一项不可或缺的控制技术。同时,由于现代大容量FPGA芯片在数字电路设计方面应用也日益广泛,其具有高精度、速度快、可靠性高等优点,用户可以灵活地根据自身系统的特点进行数字电路设计,且相应 SOPC(System on Programmable Chit)技术也迅速发展,使得利用FPGA芯片进行集成多路高性能PWM 模块的开发设计成为可能。本文根据系统设计要求,介绍一种在FPGA芯片上集成可编程多路高精度数字PWM发生器的设计,可实现通过串行接口与片上处理器或与外部处理器连接,实现一个完整的控制系统。

1 总体设计方案

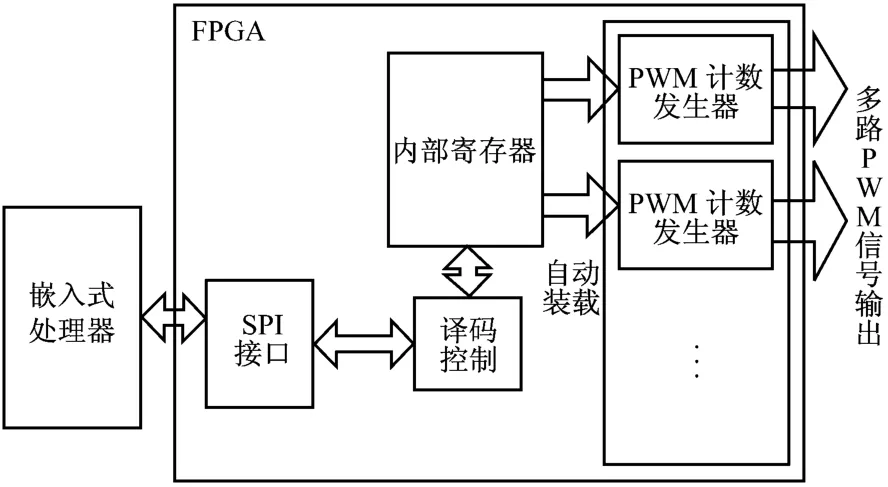

本设计采用的是嵌入式处理器外加FPGA芯片扩展多路PWM信号输出的方式来构建的。嵌入式处理器通过SPI串行数据总线与FPGA芯片进行通信,对各路PWM输出信号的参数、使能开关等功能进行设置,达到信号调制的功能。而FPGA中主要由SPI总线接口、译码控制、内部寄存器、PWM计数发生器等4部分组成,图1为FPGA芯片内部结构示意框图。SPI总线接口主要负责SPI总线规范数据的收发,收到的数据通过译码控制模块后,得到相应的地址和命令,就可对内部寄存器进行数据存取工作。内部寄存器主要用于存放内部控制信号、内部状态信号以及PWM输出的设置参数等。而PWM波形主要由2个计数器及辅助组合逻辑所组成的PWM计数发生器来产生,PWM计数发生器会自动装载内部寄存器中的相关设置数据,在控制信号的控制下进行PWM波形发生工作,并返回自身工作的一些状态信号以供监控。

图1 总体设计方案框图

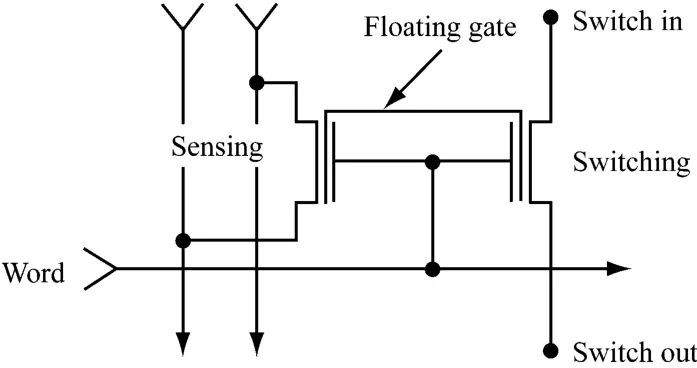

图2 基于Flash结构逻辑单元

2 FPGA扩展PWM输出的设计与实现

2.1 FPGA芯片选型

本设计中FPGA采用Actel公司的ProASIC3系列A3P030芯片,其具有高速度、低功耗、低成本、大容量及可靠性高等优点。芯片内部由Flash-CMOS结构的可编程逻辑单元组成,如图2所示。其具有掉电不丢失,故无需外部配置电路,硬件电路实现简单,上电工作快等优点。芯片还提供了丰富的用户IO接口资源,且兼容多种IO电平标准,具有通用JTAG编程调试接口。在本方案的硬件电路设计中,只需连接一个50 MHz有源晶体振荡器作为FPGA时钟输入,再配以单电源电路和简单复位电路,芯片就可以正常工作。

2.2 SPI总线接口模块

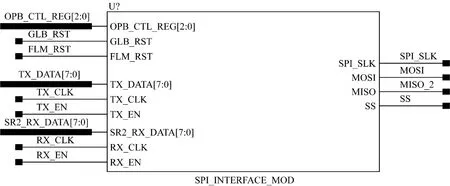

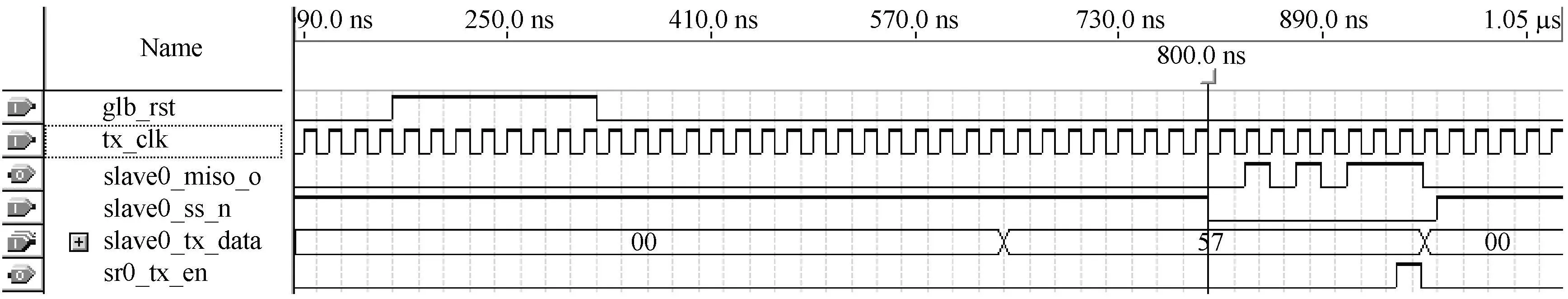

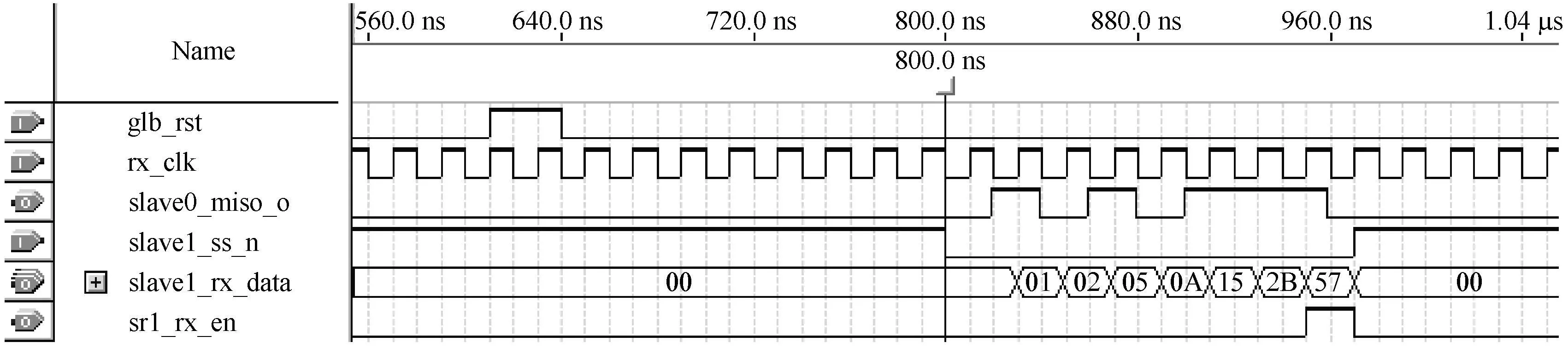

SPI总线接口模块主要任务是对数据的发送和接受进行控制。采用开放的IP软核SPI总线Slave器件模块,如图3所示,通过该模块将串行的总线数据转换为并行的8位数据形式,并输出锁存信号。本设计设定数据传输的时序模式为:CPOL空闲状态极性设置为“0”,CPHA时钟相位选择设置为“0”,可根据实际情况进行更改配置。该模块收发数据波形如图4,图5所示。

图3 SPI总线Slave器件模块

图4 MISO(主收从发)模式SPI总线数据波形

图5 MOSI(主发从收)模式SPI总线数据波形

2.3 命令及地址译码控制部分

译码控制部分通过对接受锁存和发送完成信号进行触发切换,以区分指令与数据,并对SPI主器件发送来的指令进行译码,输出对应内部寄存器地址的读写信号,使数据锁存或被读出。命令译码部分采用VHDL代码实现,VHDL代码如下:

2.4 内部寄存器模块

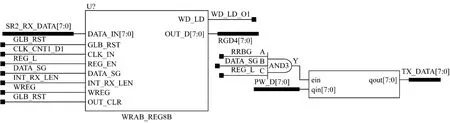

内部寄存器模块存放内部控制信号、内部状态信号以及PWM输出的设置参数等。内部寄存器模块由多个8位数据存储单元组合构成。每个存储单元都可对输入数据进行锁存,以及将存储数据输出到总线。数据存储单元模块又由输入锁存器与输出缓冲器组成,如图6所示。

2.5 PWM发生逻辑模块

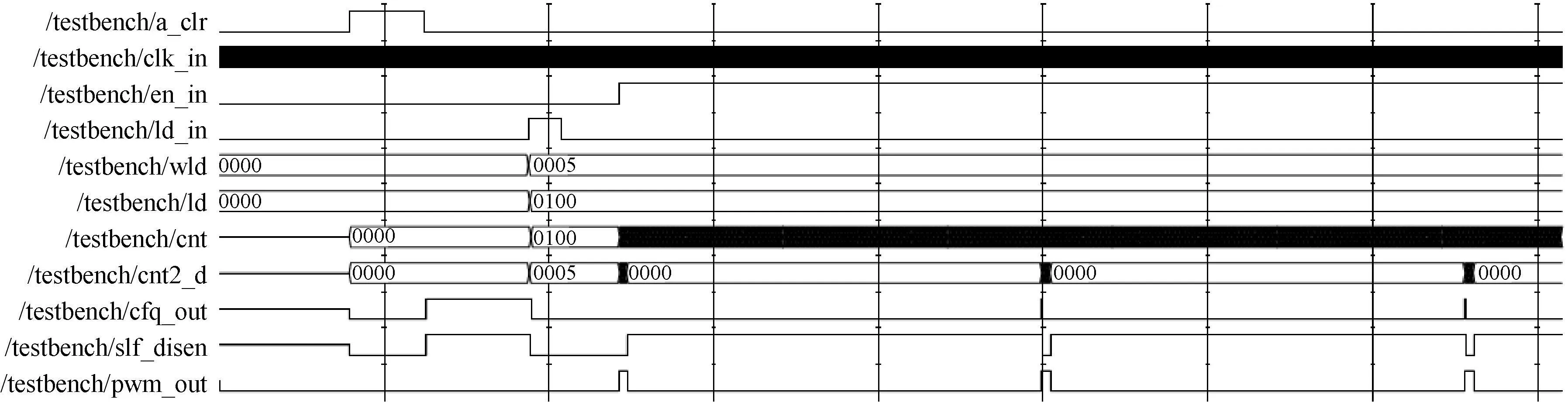

PWM发生逻辑模块是实现PWM输出的主要功能模块,由2个16位计数器及一些辅助组合逻辑组成,故其PWM输出调节精度最高可达1/65 536。PWM计数模块的计数值还可被读出,以供检查验证。外部视图如图7所示。

PWM发生逻辑模块内部逻辑如图8所示。2个16位计数器分为脉宽计数器与频率周期计数器,同时装载各自计数数据,当EN_IN为“1”时,2个计数器同时开始计数,由于脉宽计数器计数值小于频率周期计数器计数值,脉宽计数器计数先溢出,关闭自身计数使能。频率周期计数器继续计数,直至计数溢出后,输出溢出信号再次开启脉宽计数器计数,如此循环往复,即可得稳定的可调脉宽波形输出。

图6 内部寄存器

图7 PWM发生逻辑模块外部视图

图8 PWM发生逻辑模块内部视图

图9 ,图10为仿真输出波形:

图9 占空比为1.95%的PWM波形输出

图10 占空比为56.25%的PWM波形输出

仿真结果证明PWM发生逻辑模块功能完整、工作正常,且实际模块电路输出波形与软件仿真结果相符,控制效果达到了设计预期。

3 结 语

由于文中所述的数字PWM发生器每路使用独立的寄存器和使能信号,不仅能对脉宽进行高精度调节,还可实现对频率周期及初始相位的控制,且每1路都可独立工作,在多路输出时,每1路都可以以不同频率或不同相位输出。外部处理器可方便地通过SPI总线访问和配置本模块,以实现多路PWM输出,从而大大减少了主处理器IO、寄存器及运算资源。同时,此PWM发生器也可作为1个功能子模块与片上处理器集成,构成SOPC系统。此扩展数字PWM发生器现已在实际模块上成功运用,且工作稳定可靠,具有较高的调节精度和灵活性。以它为基础可进一步实现精确D/A转换输出和精密电机控制等功能。

[1] 孙立志.PWM与数字化电动机控制技术应用[M].北京:中国电力出版社,2007.

[2] 金西.VHDL与复杂数字系统设计[M].西安:西安电子科技大学出版社,2003.

[3] 侯伯亨,顾新.VHDL硬件描述语言与数字逻辑电路设计[M].西安:西安电子科技大学出版社,2002.