基于嵌入式系统的误码仪的总体设计

古志强,石春和,贾盼恩 (军械工程学院,河北 石家庄 050003)

基于嵌入式系统的误码仪的总体设计

古志强,石春和,贾盼恩 (军械工程学院,河北 石家庄 050003)

误码仪是专门为测试通信信道误码率而开发的仪器,其测试的直观性给工程实际应用带来了极大的便利。设计了基于嵌入式系统和FPGA的简易误码仪,充分利用了FPGA强大的可编程能力和丰富的资源,以及WinCE嵌入式系统体积小、功能强大等优势。设计了基于FPGA的误码测试板,该板通过PC104总线与PCM-3350嵌入式系统板进行通信,在实验平台上初步实现了其功能,具有很好的实用价值。

嵌入式系统;误码测试仪;FPGA;PC104

0 引 言

由于数字通信具有许多优良的特性,数字传输方式日益受到欢迎。但在数字通信中,信道噪声使得接收端不可避免地会出现误码而影响通信的可靠性,在数字通信中误码率是一项主要的质量指标[1]。因而,误码与误码率的研究与检测一直深受关注。误码仪将信道误码率结果直观、准确地显示出来,从而可方便地判断数字通信系统的可靠性。本文充分利用了FPGA的灵活性,以及嵌入式系统的体积小、功能强大等优势,设计了该简单实用的误码仪。

1 误码测试系统的基本原理

误码率的测试仪主要由发送模块和接收模块两个部分组成[2]。首先,由发送模块产生伪随机码序列数据流,作为误码测试的测试码;经过发送端发送到被测信道,测试码通过被测信道后由接收端模块接收,经过一定的处理后,将其与本地产生的、与发端形式相同的伪随机码比特流进行比较,分析比较的结果即可计算误码率,从而完成误码测试。误码率计算方法如下[2]:

式中,m为传输的误码数,N为发送的码元总数。

如图1所示,其中,接收端的时钟提取电路为本地测试码发生器提供与发送端同频率的时钟,从而保证接收端时钟的正确性。

2 误码测试板的设计思路

误码测试板设计思路示意图如图2所示,该板由FPGA及其外围电路组成,核心器件为FPGA,其工作原理如下:

图1 误码率测试原理图

在低频时钟CLK1的驱动下,将 “测试码生成模块”生成的时钟测试数据输入到被测信道,由FPGA设计的接收端接收。接收端包含有时钟同步模块、帧同步和误码检测模块和误码统计模块。 “时钟同步模块”在高频时钟CLK8的驱动下,提取时钟测试数据流的时钟信号,时钟同步成功后,便得到同步时钟CLK和时钟同步信号Syn,并用Syn信号通知发送端时钟同步阶段已完成,使 “测试码生成模块”开始发送周期为T=29-1的m序列 (即该系统标准的误码率测试码)。m序列经过被测信道进入接收端的 “帧同步和误码检测模块”,接下来进行帧同步搜索,当首次搜索到帧同步信号时,所有计数器复位并开始计数,并对一帧数据进行误码检测;若非首次搜索到帧同步信号,则只对帧信号进行误码检测。检测到的误码信号传递给 “误码统计模块”,该模块负责统计误码数,并把误码数送给显示模块进行误码率计算和显示。在误码检测过程中,若一帧数据的误码数达到误码阈值或者激活 “Reset”键,则该模块会给帧同步和误码检测模块发送LostSyn信号,使所有的计数器清零,并使系统重新进行帧同步搜索和误码检测。

3 误码仪软硬件设计

3.1 误码仪硬件设计

误码仪的主要硬件构成为研华公司的PCM-3350嵌入式系统板和自行设计的以ALTERA EPF10K20TC144-4芯片为核心的误码测试板。

PCM-3350是一款基于X86体系微处理器和PC104总线的模块,板载功耗低,可以无风扇工作,支持Windows CE系统,兼容工业计算机的所有功能,专门为嵌入式系统开发设计,能够适合各种场合和各种恶劣环境[3]。

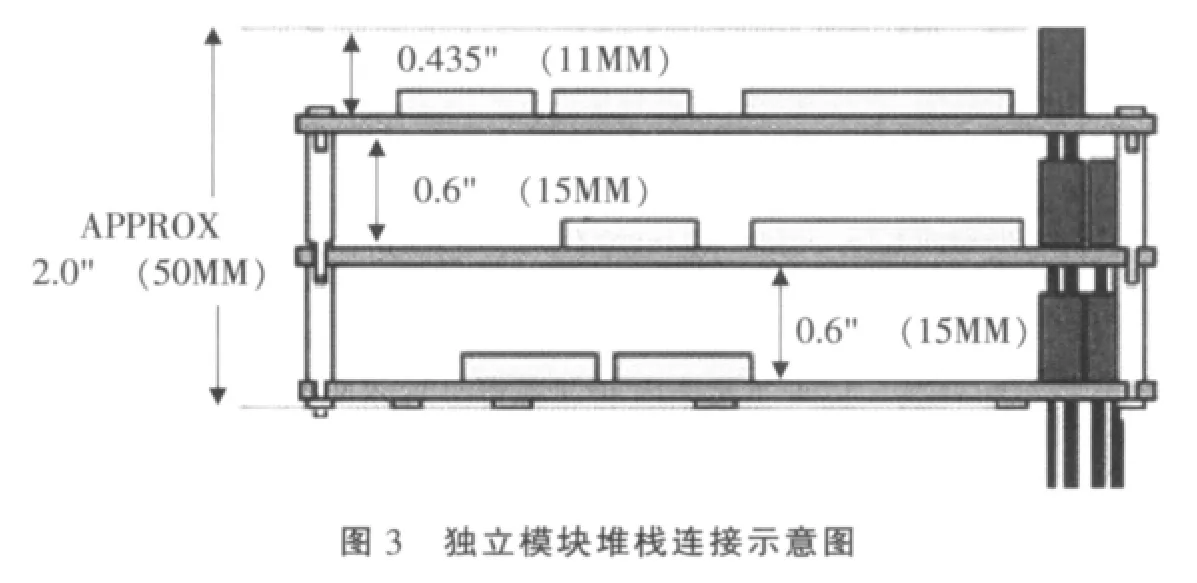

PCM-3350和误码测试板通过PC104相连接。其中,PC/104总线信号定义和功能与它们在ISA总线相应部分是完全相同的。104根线分为5类:地址线、数据线、控制线、时钟线、电源线。其模块的扩展和应用非常灵活[3]。在嵌入式系统中通常有独立的模块堆栈和作为元件应用两种基本方法来使用。该设计中采用独立模块堆栈的方法,即PC104总线模块之间的连接是通过上层的针和下层的孔互相咬和相连,这种层叠封装有极好的抗震性,也可以硬件减小占用的面积。该设计中误码测试板和PCM-3350的连接方式就是采用独立模块堆栈的方式。独立模块堆栈连接示意图如图3所示。

误码测试板的设计以EPF10K20TC144-4芯片为核心,充分利用了FPGA芯片灵活的编程能力,使得设计的周期和成本大大降低。EPF10K20TC144-4芯片具有144个外部引脚,有102个可以被配置使用,具有1 152个逻辑单元,12 288个RAM位,1 344个触发器。该器件使用TQFP封装方式,支持高达60MHz的数据速率[3]。测试码发送模块和接收模块都由该芯片实现,同时为了调试方便,设计了手动误码加入模块。

误码测试板与PC104总线进行连接时,使用的总线信号包括:数据总线,SD0~SD15;地址总线,SA0~SA9;读写线,IOW、IOR;DMA控制信号,AEN;电源和地线,+5V、+12V、GND等。其中,SA0~SA9直接与FPGA配置为输入的10位IO引脚相连。SD0~SD15直接与FPGA配置为输出的16位引脚相连接。IOW、IOR、AEN直接与FPGA配置为输入的3位IO引脚相连。其他为电源、晶振和FPGA配置模块和掉电保护等外围电路。

3.2 误码仪的软件设计

WinCE是开放体系结构的嵌入式操作系统,具备完备的操作系统特性包,能较好地满足开发基于嵌入式误码仪的需求[4]。

为了使自行设计的误码测试板能实现其功能,为其开发了配套软件,包括应用程序和流式接口驱动程序。

设备驱动程序是操作系统与硬件交互的方式,是连接硬件与操作系统之间的桥梁,操作硬件是驱动的首要任务[5]。在WindowsCE下,多数驱动程序都以用户状态下的DLL文件形式存在。DLL文件最大的优势在于可在系统运行时动态加载。本设计中的流式接口驱动程序的加载就是通过应用程序动态加载实现的。流式接口驱动程序具有定制的接口,是一般类型的设备驱动程序,其驱动程序文件一般也表现为 “*.dll”文件。这种驱动程序的函数是一组固定的函数,称为流接口函数,这些函数使得应用程序可以通过文件系统访问这些驱动程序,也就是说,流式接口驱动程序把设备抽象为文件进行操作。

Windows CE中定义的流式接口函数有 12个[5],分别为 XXX_Open(),XXX_Close(),XXX_Init(),XXX_Deinit(), XXX_Read(), XXX_Write(), XXX_Seek(), XXX_IOControl(), XXX_PowerUp(), XXX_Power-Down(),XXX_PreClose(),XXX_PreDeinit()。其中XXX是驱动程序的设备名称,有些函数是直接与某个文件操作API对应的;而有些函数是为了某些特殊的目的。在本设计中设备名称为BER,所以命名用到几个函数为BER_Init(),BER_Deint(),BER_Read(),剩余几个流式接口函数不进行任何实质性的操作,可以置为空函数。在BER_Init()中实现一些全局变量的初始化,在BER_Deinit()中实现全局变量的恢复,在BER_Read()实现了从总线上读取数据的功能。

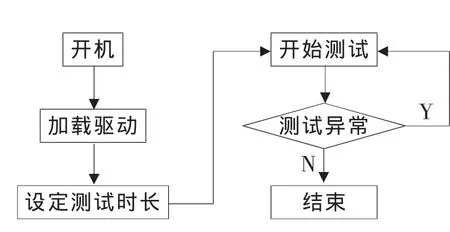

该设计的应用程序基本结构如图4所示。

该软件的开发环境为EVC4.0,面板中显示的项目有误码个数、误码率、测试时间和当前时间,以及测试进度。使用方法为:首先打开电源,系统初始化的过程中应用程序自行启动并动态加载流接口驱动程序,然后进入设置测试时长的界面。设置完后按确认键进入测试面板,面板中的显示实时的计算结果。

误码相关数据从读出到显示的基本流程为:首先由应用程序每0.5s调用读函数,读函数通过调用下面这个函数:

BOOL ReadFile(

HANDLE hFile,

LPVOID lpBuffer,

DWORD nNumberOfBytesToRead,

LPDWORD lpNumberOfBytesRead,

LPOVERLAPPED lpOverlapped

);

驱动程序就将要读取的数据返回给应用程序。应用程序得到所需数据后,再将数据按照误码率计算方法进行运算,计算的结果在误码仪的测试软件面板中显示出来。

对于FPGA的程序设计,采用VHDL语言和原理图混合的方法实现五大功能模块,有测试码生成模块、时钟同步模块、帧同步和误码检测模块、误码统计模块,LE使用率为91%。

图4 应用程序基本结构

4 结束语

为了验证以上所述设计方法的有效性,在理论研究的同时,也进行了一些实验。在对整个系统调试过程中,直接将发送端接到接收端进行自测时,设定测试时间为30分钟,如果没有手动加入误码,则误码个数显示为“0”,误码率显示为 “0”;如果手动加入误码,误码个数与手动加入误码次数相一致,误码率显示正确。系统调试结果表明,该方案具有可行性。在以后的研究中将进一步完善之。

[1] 樊昌信,曹丽娜.通信原理[M].6版.北京:国防工业出版社,2006:398.

[2] 杨亮.低速率误码测试仪的设计和实现[D].郑州:郑州大学,2005.

[3] 关进辉.面向防空指挥系统的空情信息模拟训练器的设计与实现[D].石家庄:军械工程学院,2010.

[4] 赵国峰,朱其林.基于WinCE移动终端的无线视频会议系统[J].通信技术,2008,41(8):201-203.

[5] 何宗键.Windows CE嵌入式系统[M].北京:北京航空航天大学出版社,2006:194-264.

Design of BER Test Apparatus Based on Embeded System

GU Zhi-qiang,SHI Chun-he,JIA Pan-en (Ordnance Engineering College,Shijiazhuang 050003,China)

BER test apparatus is designed to test bit error rate of communication channel.Intuition of the test brings great convenience to the practical application.A sample BER test apparatus based on embedded system and FPGA is designed,making full use of the design flexibility and powerful function of FPGA and WinCE embedded system.The BER test board is designed and its communication with the PCM-3350 board depends on PC104.Its preliminary function is achieved on the experiment platform,It has a good practical value.

embedded system;BER test apparatus;FPGA;PC104

TN911

A

1002-3100(2010)09-0089-03

2010-06-22

古志强(1987-),男,江西寻乌人,军械工程学院硕士研究生,研究方向:控制系统性能检测与故障诊断。