基于FPGA的数据采集与存储技术研究

张 临,张建民

(天津职业技术师范大学 电子工程学院,天津300222)

当前音频信号的采集技术主要分为8位、16位和24位采集。8位音频采集与处理技术电路简单,容易实现,但由于失真较大,现在很少被采用。24位和16位采集的音频信号在听觉效果上相差不大,但24位占用了更多的资源,实现电路复杂,也很少被采用。目前音频信号处理技术主要是指16位数据采集与处理技术。AD7705是AD公司推出的带有二通道的高精度AD转换器,适合于测量低频模拟信号,采用∑-Δ转换技术来实现16位转换精度,可广泛应用于智能系统、微控制器和数字信号处理系统中。近年来现场可编程门阵列FPGA的飞速发展也在数据处理中占据一席之地,高端的FPGA已经集成了DSP功能,并不断壮大,甚至在某些领域将有可能取代DSP,FPGA内部丰富的逻辑资源使其非常适合于实时数据处理。本文正是从此出发,利用AD7705及FPGA设计了音频信号采集系统,并利用Quartus II对采集系统进行了仿真。针对前端信号中存在的噪声,设计低通滤波器对噪声进行处理,并使用MATLAB对低通滤波器进行仿真,验证了设计的可行性。

1 系统设计

传感器采集到的音频模拟信号首先经过信号调理电路处理,然后对其进行滤波并送AD处理,转换后得到的数字信号经FPGA[1]处理,并存储在FLASH中。音频信号采集的方框图如图1。

图1 系统设计方框图

2 硬件设计

2.1 信号调理

由于被采集的信号相对较小,而且经常会伴有噪声,所以在前端需要对信号进行放大、滤波。同时由于被采集的信号都是单端信号,所以要在信号进入AD之前进行差分变换,通过将信号放大,再移位来实现。

2.2 前端滤波

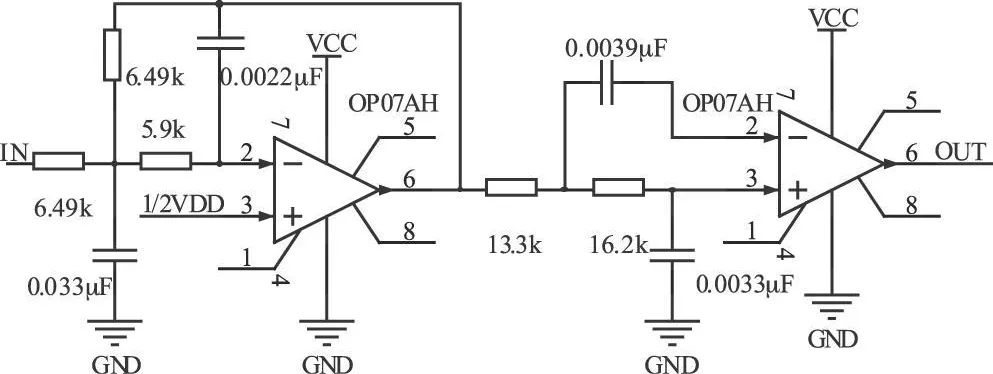

音频低通滤波器[2]主要是滤除音频以外的噪声信号。音频信号频率为20 Hz~20 k Hz,由于实际生活中的音频信号范围在50 Hz~10 k Hz范围内,考虑到实现的难度,本文设计成低通滤波器。具体要求截止频率3 dB,10 k Hz阻带衰减不小于-40 dB。通过查表或使用相关滤波器设计软件可以知道:电路由1到2个单元的运放和任意RC网络组成可以实现,本文采用4阶巴特沃斯实现,如图2所示。

使用Matlab 7.0[3]对音频低通滤波器进行仿真,仿真结果如图3。从仿真图中可以看出截止频率满足-3d B,音频信号上限10 k Hz时衰减-41.8 dB,也满足设计要求。

图2 音频带通滤波器

图3 带通滤波器仿真结果

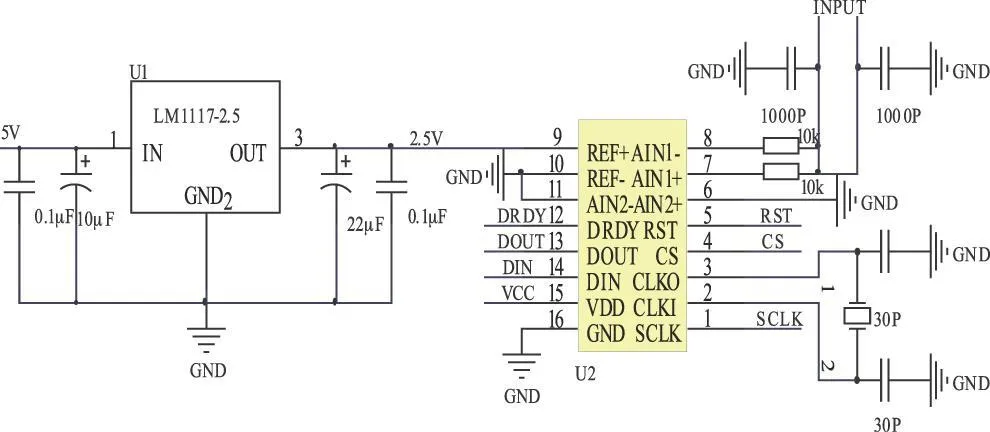

2.3 基准电源及AD外围电路设计

由于基准电压对AD转换器影响很大,本设计采用专用集成稳压芯片LM1117系列低压差电压调节器来提供基准电压[4]。LM1117具有电流限制和热保护电路,包含1个带隙参考电压以确保输出电压的精度在1%以内,本文采用固定输出电压的LM1117-2.5为AD提供2.5 V基准电压。

数字接口AD7705的串行数据接口包括5个接口,其中片选输入CS、串行时钟输入SCLK、数据输入DIN、转换数据输出口 DOUT、转换结束指示位DRDY。主要硬件连接如图4所示。

图4 基准电源设计

2.4 存储电路设计

2.4.1 基本原理

本文采用AT45DB041B对采集信号进行存储,该存储器主要由主存储器和两个264B的缓存构成,主存储器容量约为 4Mbit,分为 2048页,每页也为264B。

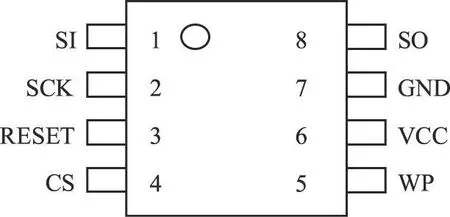

图5是AT45DB041B的SOIC-8的封装形式,各管脚的定义与功能如下:1脚:SI,串行数据输入端;2脚:SCK,串行时钟信号。数据在SCK上升沿输入,接高电平;4脚:CS,片选信号,低电平有效;下降沿输出;3脚:RESET,复位信号,低电平有效。由于芯片内部有上电复位电路,不用时此管脚可直接5脚。5脚:WP,写保护信号,低电平有效。若此脚为低,则主存储区前256页不能被擦写编程,如果不用此功能,可直接接高电平;6脚:VCC,电源输入端;7脚:GND,电源地;8脚:SO,串行数据输出端。

图5 存储电路封装

AT45DB041B的操作命令分为读命令、编程和擦写命令以及附加命令:

(1)读主存储区

不经过缓冲区读主存储区任一页,缓冲区内容不会改变。指令格式后续的SCK信号将使数据依次从SO端输出。如果读到了指定页的最后字节,将自动跳回到页首起始位置,循环读取。整个过程中,CS必须保持为低电平,CS从低到高的跳变将中止读操作,并将SO引脚置三态。

(2)连续读主存储区

不经过缓冲区直接读任意存储单元的内容,缓冲区内容也不会改变。指令格式后续的SCK时钟信号将使数据依次从SO端输出。如果读到了整个主存储区的最后字节,将自动跳回主存储区起始位置,循环读取,页与页之间及主存储区首尾之间没有延时。整个过程中,CS必须保持为低电平,CS从低到高的跳变将中止读操作,并将SO引脚置三态。

(3)写缓冲区

数据能够通过SI端被写入任意一个缓冲区。当写到缓冲区结尾后仍有数据写入时,数据将从缓冲区起始字节依次写入。只要CS保持为低,在SCK时钟信号配合下,数据将一直循环写入,CS从低到高的跳变将中止写操作。

(4)缓冲区写入主存储页(带擦除)

事先写入缓冲区的数据可通过编程写到主存储页中。当指令写完后,CS由0变为1时,芯片首先擦除待写入页,然后再将指定缓冲区内的数据写入主存储页。页擦除和写入操作由内置时钟控制。

2.4.2 硬件接线

图6 AD转换及存储电路连接

AD转换以及存储电路的硬连接[5]如图 6,将EP1C6Q240C8N的IO和AT 45DB041B的SI、SO 、SCK、RST、CS引脚相连,WP接高电平;通过 AD转换,EP1C6Q240C8N将转换结果存储于AT45DB041B中,完成数据存储工作。

3 软件设计

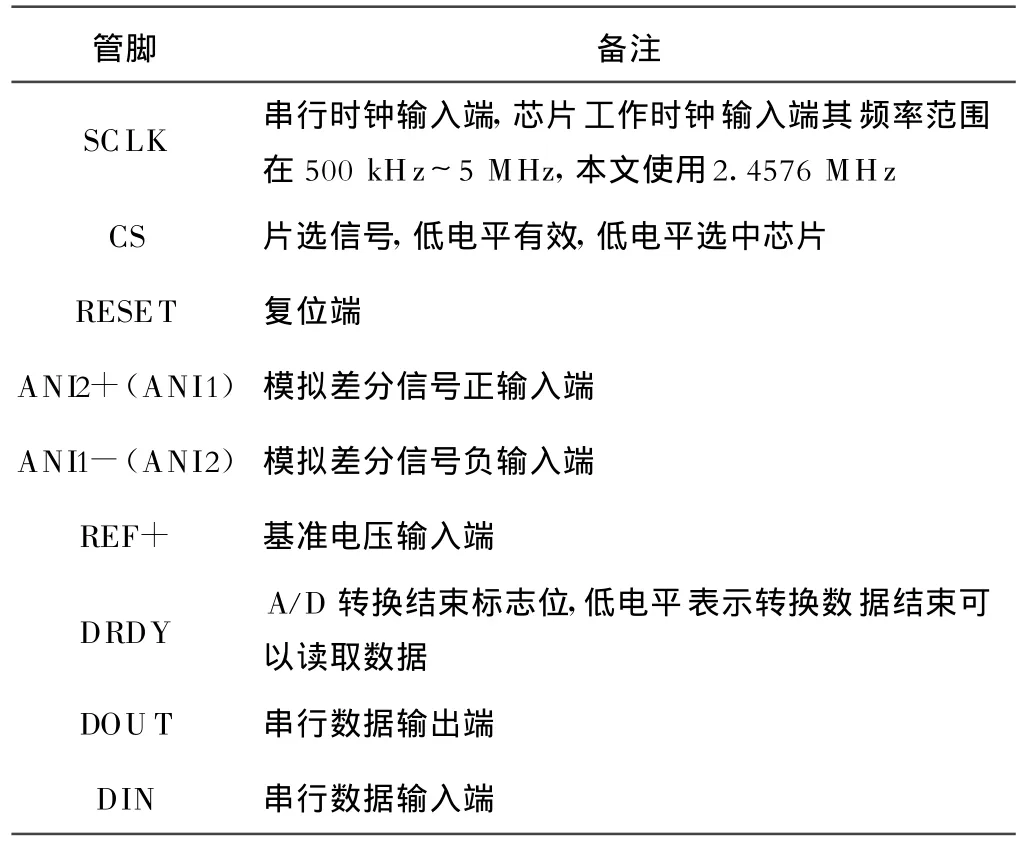

本文所使用的AD7705是AD公司生产的适合于测量低频信号的16位AD转换器,主要引脚功能介绍见表1。

表1 AD主要引脚功能

依据奈奎斯特采样定理,在模拟信号的数字化过程中,要想不失真的还原出原信号,采样频率必须大于模拟信号最高频率的两倍,即

由于音频信号的频率范围为20 Hz~20 kHz,即fh=20 kHz,所以采样频率最低为40 k Hz。目前对音频信号的采集频率主要有44.1 k Hz和48 k Hz两种,为更好地还原信号本文使用48 k Hz采样速率。

AD7705在时钟为2.4576 MHz的条件下,更新速率有四种,分别为50 Hz,60 Hz,250 Hz,500 Hz,即理论上最快只需2 ms即可完成一次数据转换。由相关资料知,AD7705典型建立时间为16 ms,即使用60 Hz更新速率,16 ms完成一次转换,每秒输出60次转换结果。本文更新速率使用60 Hz。由AD手册[6]知串行时钟脉冲宽度不得小于100 ns,即时钟不得大于5 MHz,通过将系统时钟分频,得到所需要的串行时钟。

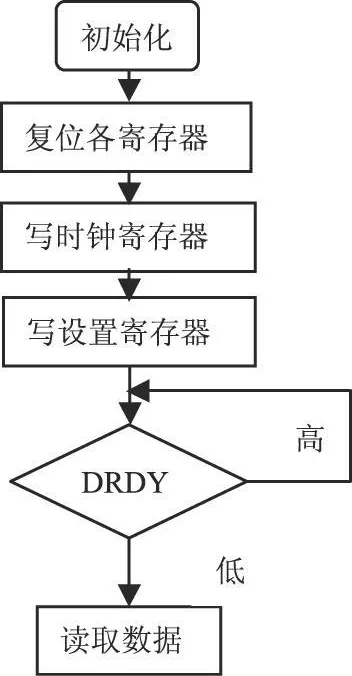

上电或复位后,器件等待指令数据写入通信寄存器。包括向 AD7705写控制字。当写入控制字后,AD7705即处于工作状态,对采集到的模拟量进行模数转换。当模数转换完毕后,AD7705的DRDY引脚会产生一个低电平。系统工作后,FPGA查询DRDY电平状态。如果引脚为低,则AD7705转换数据结束,可以读取数据,具体流程如图7所示。

图7 数据采集流程图

4 试验结果

利用QuartusII[7],对系统采样进行了仿真,结果如图8所示。

图8 FPGA控制AD时序仿真

从图8我们可以知道,对FPGA的操作首先复位各寄存器,然后写控制字,再通过通信寄存器对时钟寄存器、设置寄存器进行访问。分别写控制字FFH、05H 和40H,分别表示AD晶振2.4576 MHz,更新频率60次/s,自校准模式,差分输入。

5 系统设计注意事项

(1)如果AD7705复位引脚直连VCC,最好在初始化程序中加入初始化序列,不然DRDY信号不会输出,就检测不到转换是否结束,也就无法读取转换结果。

(2)如果AD7705采集单端信号,则输入必须在0到VDD之间,而不可以超出或为负。如果一个输入为负,则另一个输入会有灌入电流的现象,芯片无法正常运行。

(3)AD7705的模拟地和数字地要分开走线,最后汇聚到一个唯一的公共点,并且这个点要尽可能靠近AD7705。

(4)数字信号线应尽量避免走在AD7705芯片下面,模拟地应布置在芯片的下面,电源线、地线应尽可能粗,时钟信号要尽量远离模拟信号,并用数字地屏蔽。

(5)AD7705时钟大于2M时,时钟设置寄存器的CLK位应置1,小于2M时应置0。SCLK的脉冲宽度要满足最小的脉宽要求。在时钟SCLK下降之后的低电平期间读取数据DOUT。在时钟SCLK的低电平期间写入数据DIN,然后在SCLK的上升沿写入到AD7705。在两次写操作之间,DIN最好保持在高电平,时钟信号SCLK在两次操作AD7705之间也要保持高电平。即在AD7705空闲时刻,或两次操作之间的空闲时刻,DIN、SCLK都最好保持高电平。

6 结束语

音频AD转换器的选择直接关系着听觉效果,精度太小能明显感觉失真,精度太高则成本及实现难度也会加大。本文选取精度适中的16位AD转换器对音频信号进行采集与处理,并采用FPGA作为微控制器。通过对音频信号进行滤波、放大,AD转换,最后被FPGA采集并存储。实际操作证明本文方案不仅易于实现,转换速度较快,而且能感觉音质有一定的提高。

[1] 王 诚,吴继华.Altera FPGA/CPLD设计[M].北京:人民邮电出版社,2005.

[2] McGraw Hill,Sanjit K Mitra.Digital Signal Processing[M].A Computer-Based Approach,Second Edition,2001.

[3] Sanjit K Mitra编,孙洪 等译.数字信号处理实验指导书(Matlab版)(第一版)[M].北京:电子工业出版社,2005.

[4] 王 超,黄显高.高速数据采集系统的电源设计研究[J].西安邮电学院学报,2009(9).

[5] 宁 海,尹青山.低功耗16位A/D转换器 AD7705及其应用[J].甘肃农业,2006(6).10-13.

[6] Analog Device.AD7705/AD7706 Manual[Z],2001.

[7] 侯伯亨,顾 新.VHDL硬件描述语言与数字逻辑电路设计[M].西安:西安电子科技大学出版社.2006。