烧结温度对氧化铝陶瓷机电性能的影响*

李宏杰

(西安创联轮德器件有限公司 西安 710065)

烧结温度对氧化铝陶瓷机电性能的影响*

李宏杰

(西安创联轮德器件有限公司 西安 710065)

烧结温度对氧化铝基板性能有重要影响,随着烧结温度的提高,瓷片的体积电阻率、体积密度、击穿强度升高,抗折强度呈先上升后下降趋势,而介电常数、介质损耗角正切则是先降低后升高。得出最佳的烧结条件为1 570℃保温2 h。

烧结温度 氧化铝陶瓷 抗折强度 体积电阻率 击穿电压 介电常数 介质损耗 体积密度

前言

由于氧化铝陶瓷具有优良的机电性能,如导热率较高,耐高温,绝缘性能良好,机械强度适中、耐磨及耐化学腐蚀,且价格低廉,工艺成熟,故广泛用在电子、电气、航空、航天、石油化工等领域,成为目前用量最大的工程陶瓷之一[1~2]。在微电子行业,A-75瓷常用来制作电阻瓷基体;A-96瓷常用作厚膜电路基板;A-99瓷常用作薄膜电路基板[3]。BeO陶瓷虽然导热率高,但毒性大,随着人们环境保护意识的增强,国家相继出台了一系列环境保护法,限制生产使用BeO陶瓷。A lN陶瓷虽然具有导热率高(是A l2O3陶瓷基板的5~10倍),膨胀系数与Si接近等优点,但原料合成到目前尚未大批量生产,且批次一致性差,难以烧结。但在陶瓷基板领域中,流延法生产A l2O3陶瓷基板仍占着统治地位。

我公司引进的美国流延法成形生产线,瓷料配方体系为M gO-A l2O3-SiO2三元系统。在长期的生产实践中发现,由于国产氧化铝粉形貌不规则,钠离子含量较高,导致产品的介质损耗过高,体积密度上不去,高温体积电阻率较低,无法满足客户的需求,针对此情况,我公司开展了A-96瓷瓷料配方的研究。在文献[4]中,通过在M gO-A l2O3-SiO2三元系统中引进CaO,成功地改进了产品的机电性能;产品的抗折强度值及其分散性也得到了一定改善,虽然达到了国标,在实际使用中仍显强度不足。为此,我公司又开展了抗折强度提高试验。在文献[5]中,通过攻关进一步提高了抗折强度,降低了强度分散性。笔者在文献[4~5]的基础上,通过对烧结工艺的优化,进一步提高产品的性能。现已用于批量化生产中。

1 实验

1.1 实验用原料

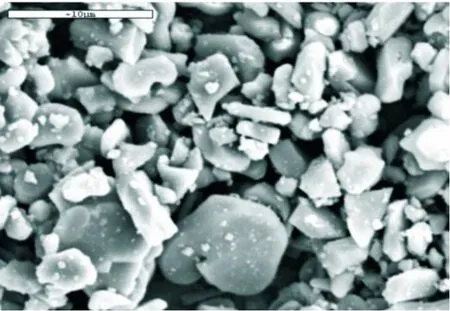

氧化铝微粉由河南鑫源陶瓷材料有限公司提供,d50=1.94μm,比表面积为14 114 cm2/g。化学成分见表1,粉体形貌见图1。

表1 氧化铝微粉的化学成分(质量%)

图1 0.192%Na2O氧化铝粉体材料的形貌(×4 000)

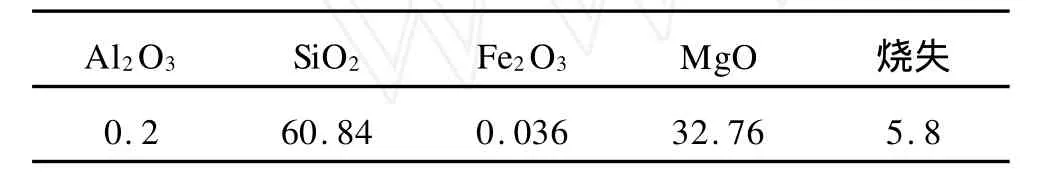

由图1可见,国产氧化铝粉的形貌极不规则,有片状、板状及多面体状,且大小相差很悬殊。滑石粉(TALC)由辽宁艾海滑石有限公司提供,d50=4.6 μm,化学成分见表2。

表2 TALC的化学成分(质量%)

碳酸钙(CaCO3)由山东东营益达化工厂提供,含量99.5%,d50=1.2μm。二氧化硅(SiO2)由四川顺达新材料有限公司提供,含量99.0%,d50=1.6μm。

La2O3由江苏阜宁稀土实业有限公司提供,含量≥99.0%;d50=3.2μm。

1.2 工艺路线

将氧化铝微粉、助熔剂、分散剂和溶剂按配方比例称重加入球磨机中球磨20 h,再将增塑剂和粘合剂加入,球磨30 h后,测试浆料粘度,合格后出料。

1.3 试样制备

将制备好的合格浆料,真空除泡后,在TCMⅢ流延机上流延成形1.0mm厚度的制品,干燥后,在气动冲床冲制成50.8 mm×50.8 mm和20 mm×60 mm的两种瓷片。撒沙机撒沙叠片后,进高温炉在不同的烧结温度下烧结。烧结温度分别为1 540℃/2 h;1 570℃/2 h;1 600℃/2 h。抛光清洗后在覆平炉里矫平。选取20 mm×60 mm的瓷片做瓷片抗弯强度和体积密度试验。在50.8 mm×50.8 mm的瓷片正反两面按GB5593的规定制作银电极,烧银后进行体积电阻率、击穿强度、介电常数和介质损耗性能测试。

1.4 性能测试

使用NF2511A绝缘电阻测试仪,分别在室温、300℃、500℃条件下保温15 min,给试样加不大于500 V的直流电压,1 min后读取电阻测量仪上的读数,得到试样体积电阻率:

式中:ρ——试样的体积电阻率,Ω·cm;

d——试样电极的外径与内径之差,cm;

RV——测得的试样的绝缘电阻,Ω;

t—试样的厚度,cm。

使用阿基米德排水法测定了体积密度;使用三点弯曲法测定了材料的抗折强度;使用ZYS—75型高压试验装置在室温下测定了试样的击穿强度;按国标GB5593—85的方法用HP4295A在1 M Hz下进行了Tanδ和介电常数的测定。

2 试验结果

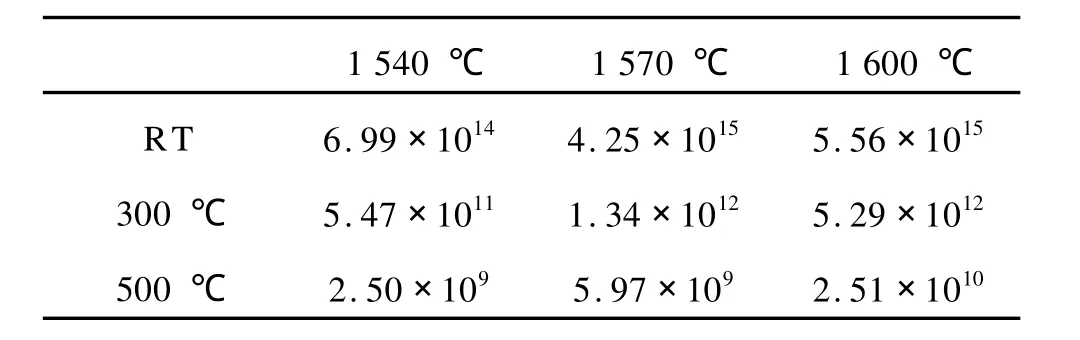

2.1 体积电阻率

不同烧结温度体积电阻率的测试结果见表3。由表3可看出,随烧结温度提高,瓷片的体积电阻率,不论在室温、300℃还是500℃,体积电阻率都有不同程度的提高,且体积电阻率随烧结温度的提高而提高。原因在于随烧结温度的提高,晶界出现更多玻璃相,填充晶界缺陷,并有利于气孔的排出和致密化。致密的材料有效抑制了钠离子的迁移,从而提高了体积电阻率。

表3 在3种烧结温度下制得样品的体积电阻率的比较(Ω· cm)

2.2 介质损耗角正切与烧结温度的关系

介质损耗角正切与烧结温度的关系如图2所示。

由图2可以看出,随着烧结温度的提高,介质损耗角正切先是减小,接着增大。介质损耗角正切的具体意义是电容器消耗的电能与其所储存电能的比值。它与测试频率和温度密切相关。介质损耗主要是由电导和极化引起的[6]。随着烧结温度的提高,体积电阻率升高,电导下降,故在此情况下,介质损耗的增大应该不是由电导率引起的,应是由极化引起的。结合图3中介电常数与温度的关系也可看出,随着烧结温度的提高,瓷体的介电常数增大,即极化增大,引起损耗角正切升高。1 540℃、1 570℃烧结的瓷体,其介电常数变化不大,而在1 600℃烧结的瓷体,其介电常数明显变大。介电常数是衡量电介质储存电荷能力的参数,它是由陶瓷中质点的极化引起的。在常温和目前的测试条件下,极化主要是位移式极化(包括电子位移极化和离子位移极化)和离子松弛极化[7~8]。

图2 温度对介质损耗角正切的影响

图3 不同烧结温度下瓷体的介电常数

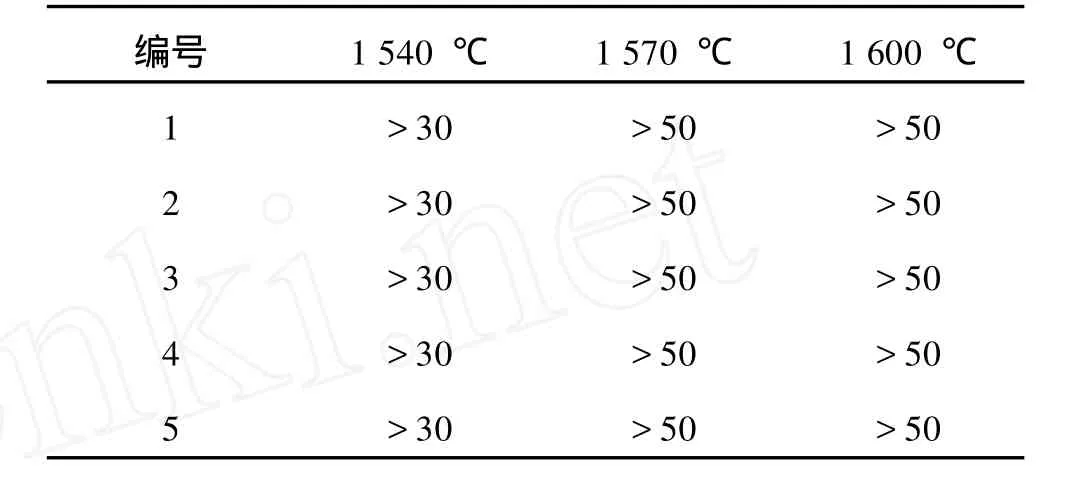

2.3 材料击穿强度、体积密度与烧结温度的关系(见图4、表4)

从图4、表4可以看出,随着烧结温度的升高,材料的体积密度和击穿强度均会提高。随着烧结温度的升高,在晶界出现较多的液相,致密化速率加快,缺陷消除较快,可以得到较为致密的瓷体,从而使体积密度得到提高。较为致密的瓷体可以有效阻止离子的迁移,从而提高击穿强度。

图4 温度对体积密度的影响

表4 击穿强度的测试结果(kV)

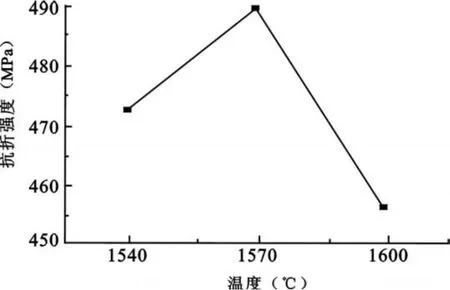

2.4 材料抗折强度与烧结温度的关系(见图5)

图5 烧结温度对样品抗折强度的影响

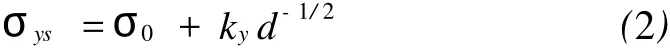

由图5可以看出,随着烧结温度的升高,材料抗折强度呈先上升后下降趋势。这可解释为:在较低烧结温度下,瓷体的晶粒细小,但气孔也较多,故抗折强度较低;随着温度的升高,气孔率降低,晶粒仍然较小,此时抗折强度最高;烧结温度进一步升高,瓷体的晶粒发育得较大,根据Hall-Petch关系:

式中:d为晶粒的平均直径,cm。d越大,所得材料的强度越小。故烧结温度越低,材料的强度越大[8]。

3 结论

研究了烧结温度对氧化铝基板机电性能的影响。得到如下结论:瓷片的机电性能与烧结温度密切相关。根据瓷片体积电阻率、体积密度、击穿强度、介电常数、介质损耗角的变化,由此可以确定最佳的烧结条件为: 1 570℃,保温2 h。

1 Eugene Medvedovski.A lumina ceramics for ballistic p rotection,part1.The American Ceramic Society Bulletin,2002, 81(3):27~32

2 Eugene Medvedovski.A lumina ceramics for ballistic p rotection,part2.The American Ceramic Society Bulletin,2002, 81(4):45~50

3 K Otsuka.M ultilayer ceramic substrate-tecnology for VLSI package/ulichip module.London:Elsevier App lied Science,1993:42~45

4 蒋文军,李宏杰,卫海民.流延成形A-96瓷机电性能改进.全国性建材科技期刊——陶瓷,2010(6):33~38

5 李宏杰.La2O3对氧化铝陶瓷机电性能的影响.全国性建材科技期刊——陶瓷,2010(9):16~21

6 霍振武.掺杂对高纯氧化铝致密化速率的影响.硅酸盐通报,2002(2):8~11

7 James D Caw ley,John W,Hallo ran.Dopant distribution in nominally yttrium-doped sapphire.J Am Ceram Soc,1986, 69(8):C-195

8 石德珂.材料科学基础.北京:机械工业出版社,2003

Sintering Temperature Effect on the Electrical and Mechn ical Properties of Alum ina Ceram ic

Li Hongjie(Xi’an Chuang Lian Leadership Devices Co.,L td,Xi’an,710065)

The paper researched the effect of sintering temperature on the p roperties of alumina substratesmechnical and electrical.w hen sintering temperature arises,the volume resistance and volume density also arises,the puncture strength arises first and decreases later.But the dielectric constant and dielectric loss decreases first and arises later.As result,draw a conclusion for best sintering condition:temperature fo r 1 570℃,heating p reservation for 2 h.

Sintering temperature;A lumina ceramic;Bend strength;Bulk resistivity;B reakdow n volt;Dielectric constant;Dielectric loss;Bulk density

TQ174

:A

:1002-2872(2010)12-0011-04

李宏杰(1968-),硕士,高级工程师;研究方向为工程陶瓷。E-mail:hongjie.li2007@163.com