基于 FPGA和 W5100的以太网通信系统设计

梁中英, 苏涛, 武荣伟, 郭文伟

(西安电子科技大学雷达信号处理重点实验室,陕西 西安 710071)

0 引言

光纤以太网是指在光纤上运行以太网 LAN数据包接入服务的网络,底层连接可以任何标准的以太网速度运行,包括 10 Mb/s、100Mb/s、1 Gb/s或 10Gb/s。在此情况下,这些连接必须以全双工速度运行,即数据可以同时往两个相反的方向传输[1]。光纤以太网业务能够应用交换机的速率限制功能,以非标准的以太网速度运行[2]。

设计中基于某特殊需求,采用无反馈的单向光纤以太网数据传输方法,克服了无握手和丢包的困难,使用FPGA控制W5100进行以太网(百兆)的网络连接后,利用 FPGA内部的高速数据收发模块(RocketIO GTP)、光模块及光纤传送数据,实现了数据率为 3 Gb/s(可扩展提高)的数据通信。

1 系统的结构组成

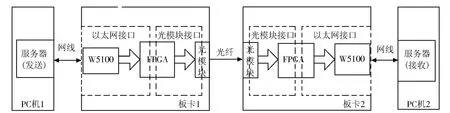

系统主要由两端的以太网接口和中间的光模块接口组成。系统框图如图 1所示。FPGA选用 Xilinx公司的XC5VLX 50T,光模块选用 FTM-5128C-SL80G。在通信链路中,计算机(PC机)与板卡通过网口(RJ45)用网线相连。板卡 1收到的以太网数据包经过速率匹配后,通过 FPGA中的GTP模块发送给光模块。板卡 2的光模块将信号进行光电转换后,经过FPGA内部的 GTP模块将数据稳定接收后通过以太网接口发送给 PC机 2。

2 以太网接口的设计实现

2.1 以太网和 W5100简介

以太网是一种基于带冲突检测的载波侦听多路访问协议(CSMA/CD)的局域网(LAN)。以太网介质传输层(MAC)是网络与设备的接口,是以太网核心部分。所选用的FPGA内部含有MACIP核,但需要对以太网的各层结构有一定的了解才能对该IP核进行参数化,开发周期较长且占用较多逻辑资源,故并没有使用,而是选择W5100来实现该功能。

图 1 通信系统结构框

W5100是一款多功能的单片网络接口芯片,内部集成有10/100以太网控制器。包括TCP/IP协议栈(TCP/IP协议是一个四层协议系统,包括数据链路层、网络层、传输层和应用层,每一层负责不同的功能[3])、MAC和物理层(PHY)。且集成有 16KB存储器用于数据传输[4]。在进行系统设计时不必考虑网络协议的细节,只需要解释并执行网络芯片传送的指令和数据就可实现网络连接,且不需要操作系统的支持,具有接口电路简单、编程方便等特点[5]。

设计中选用直接总线接口,采用 15位地址线和 8位数据线,另加/CS(片选信号),/RD(读使能信号),/WR(写使能信号)及/INT(中断信号)等信号线。

2.2 W5100读写时序的设计实现

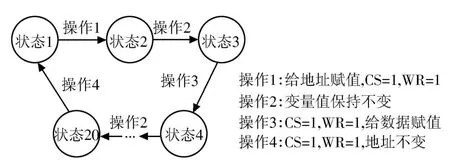

W5100对读写时序要求比较严格。若不满足读写时序的要求,会导致数据传输错误。写时序要求如图 2所示。为保证可靠,时序设计中还留有一定的裕量。

图 2 W5100写时序要求

在 FPGA中使用有限状态机来实现读写时序,以写时序为例。选用 10 MHz的时钟来进行数据和地址的写操作,即写周期为 100 ns,满足图 1中的条件 1。用 200 MHz的时钟来控制状态机,状态图如图 3所示。从图中可以看出,有效地址到/CS变低的时间(条件 2)为 15ns;/CS变低到/WR变高的时间(条件 3)为 85 ns;由图 3中的操作 1、3、4可知,满足条件 4、5、6。

图 3 写时序状态

读时序与写时序类似,将图 3各操作中的/WR信号换为/RD信号,并且不用对数据赋值,只需将数据线上的数据取出即可。

完成W5100的读写时序设计后,调用该子程序对 W5100进行初始化配置,包括基本设置、网络信息设置、端口存储信息设置、端口寄存器设置。发送初始化端口命令进行配置实现。然后发送连接请求到远程服务器,与 W5100进行网络连接。

2.3 以太网数据通信的FPGA实

2.3.1 数据接收的 FPGA实现

为了实现该系统的设计,在 PC机上需要一个服务器与W5100进行交互数据收发。这里使用 VC++编写该服务器。测试前,先设置 PC机的 IP地址,设置的值与FPGA配置W5100时的 IP地址必须一致。

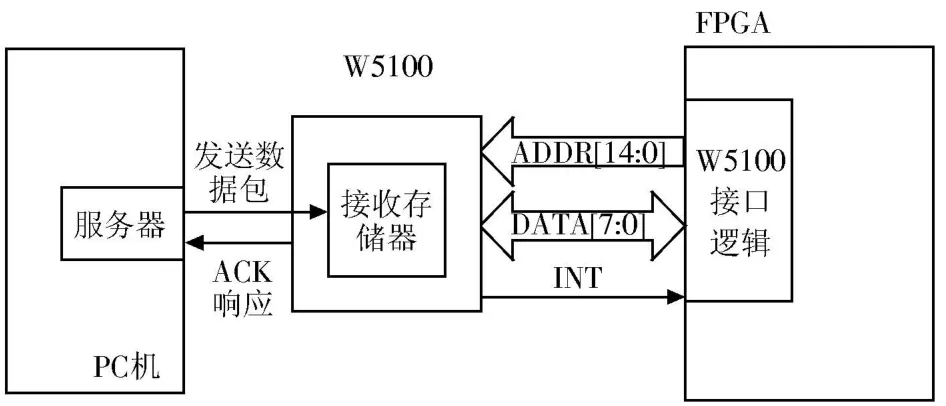

(1)接收数据至 W5100接收缓存区

服务器监听端口,给板卡上电后,W5100与服务器建立连接。数据传输框图如图 4所示。服务器发送数据包至W5100,数据放在 W5100的接收存储器中,服务器处于等待状态。W5100接收到一包数据后会触发一次中断且端口中断寄存器的第 2位会置1,表示接收到了数据。FPGA通过接收数据字节数寄存器来判断W5100接收寄存器中接收到数据的个数。

图 4 PC机发送数据到FPGA的数据传输框

(2)将 W5100中的数据读到 FPGA中

若接收到的数据个数不为 0(即有数据接收到),则开始计算数据所存放的起始地址。然后按照相应地址将数据读出到FPGA中。数据读完后,FPGA给 W5100发送一个“RECV”命令,“告诉”W5100数据已读完,可以继续接收新的数据。这之后,W5100给 PC机发送一个ACK响应,服务器继续发送数据包,重复上述过程,直到文件发送完成。

2.3.2 数据发送的 FPGA实现

数据发送的实现方法与数据接收类似,这里只作简单说明。

W5100与服务器建立连接后,FPGA读取 W5100的发送存储器剩余空间寄存器的值,计算出数据存放的起始地址。FPGA将数据写入到 W5100的发送存储器中,写满后给W5100发送一个“send”命令。 W5100给 PC机发送数据,数据发送完成后会触发中断且中断寄存器的第 4位会置 1,表示数据发送完成。如此反复操作直到数据发送完成。

3 光模块接口的设计实现

3.1 RocketIO GTP收发器简介

Virtex-5 Rocketl O GTP收发器是Xilinx FPGA器件中内嵌的一个硬核,具有通用性、低功耗和低成本等特性,可以支持多种标准协议,如Aurora协议、吉比特以太网等。

单个 GTP的线速率为 100 Mb/s~3.75 Gb/s。内建可选的物理编码子层(PCS)特性,如 8B10B编码、字符(comma)对齐、通道绑定及时钟修正等[6]。每一个GTP收发器包含独立的发送模块和接收模块。利用 GTP实现数据收发时,按照设计需求通过 Xilinx的核产生器(Core Generator)来例化 GTP即可。

3.2 光模块接口设计

以太网数据发送过来后,填充数据包至 2.4 Gb/s。填充的数据包可以是无效数据包,也可以是有效数据包(其他信号处理的数据)。填充的数据经过GTP内部的 8B10B编码模块后数据率为 3 Gb/s。编码后的数据转换成串行数据以差分的形式送入光模块。

光模块对数据进行光电转换,GTP内部的时钟恢复模块根据串行数据流提取时钟信息并恢复数据,使用提取的时钟完成串并转换,再由符号对齐和检测功能块完成数据定界,之后将 8B10B解码的数据送入弹性缓冲,FPGA的接收(RX)接口从弹性缓冲中读出数据送入FPGA逻辑。最后将以太网数据还原,即将填充的数据包丢掉,将数据送往以太网接口逻辑。

4 系统的硬件实现验证

理论上讲,单片机控制 W5100时的最大通信速度可达25 Mb/s。实际应用中,由于网络的原因、CPU与 W5100之间通信速度的等原因,使 W5100的网络传输速度远低于25 Mb/s。该设计采用 FPGA控制 W5100,经过测试发送端的速度最高可达 64 Mb/s。

由于系统是单向光纤传输,没有反馈,考虑板卡 1接收数据的速度快而板卡 2发送数据的速度慢时会出现丢包现象。在板卡1的 FPGA程序中添加一定的空循环降低接收服务器数据的速度,同时在板卡 2的FPGA程序中添加一定大小的存储空间缓存收到的数据。两端做适当调整后,不再出现丢包现象。

两个PC机的服务器都建立网络连接后,进行数据收发测试。发送端发送一个视频文件,接收端对收到的视频文件进行实时播放,试验结果证明可以准确无误的进行数据发送、接收以及流畅的视频播放。

其中的GTP收发数据部分的速率可以根据实际应用做相应的调整,多个GTP模块进行通道绑定可实现最高速率为90 Gb/s的数据收发(多路光纤)。也可将以太网数据扩充为多个用户(需要多个 W5100芯片),分时复用后经过 GTP发送,接收后再解复用将数据分配给各个用户,实现多个用户的以太网通信系统。

5 结语

结合特殊需求,介绍了利用 FPGA控制W5100实现基于以太网的单向光纤数据通信的方法且按实际需求可做相应扩展。占用FPGA内部较少逻辑资源,并通过视频文件的传输和实时播放验证了该设计方法的可行性和可靠性。也为利用FPGA进行数据处理的同时进行以太网数据通信并对通信链路的无误性进行验证提供了简单的实现方法。

[1]汤德荣.浅析多路数据采集与通信系统设计方案[J].通信技术,2010,43(02):95-97.

[2]朱礼义,巴继东.光纤以太网技术在城域网中的应用[J].光通信研究,2003,32(01):32-35.

[3]孙社文,张铭伯.基于 DSP技术和以太网卡的数据传输方案[J].通信技术,2008,41(07):98-100.成都浩然电子.

[4]W5100数据手册.Version 1.1.6.[EB/OL].(2009-03-01)[2010-02-11].http://www.doc88.com.

[5]北京博控自动化有限公司.基于 W5100的 DSP快速网络接入解决方案[J].单片机与嵌入式系统应用,2009,31(03):84-85.

[6]XilinxUG196.Virtex-5 FPGA RocketIO GTP user guide.[EB/OL].(2008-02-11)[2010-04-28].http://www.xilinx.com.