一种脉宽精密可控的脉冲信号电路设计

朱 楠,黄建国,付在明

(电子科技大学自动化工程学院,四川 成都 611731)

1 引 言

脉冲技术是现代电子技术中一项重要的基础技术,其在大规模集成电路的测试、半导体器件性能检测、地质探测以及雷达、电子对抗、通信系统和计算机硬件系统设计中都起着重要作用。但传统意义上的脉冲信号已经不能满足现代技术的需要,在很多实际工程应用中对高速脉冲信号源多样化要求越来越高,不仅关注脉冲的频率和上升沿,而且要求高速脉冲的电平和幅度能够在较大范围内精密可控,同时需要其脉冲宽度和脉冲延迟也精密可调。因此,该文根据实际需要,采用FPGA与高精度、高分辨率的可编程延迟芯片相结合的方法,实现对脉冲宽度的大范围高精度的精密可调控制。

方案的设计目标是实现频率覆盖范围为200kHz~250MHz、脉宽可调范围为 2ns~(周期-2ns)、分辨率为10ps的脉冲信号。根据设计目标,同时考虑到实际需要及产品化时对于成本的控制,经过对多种不同系列的FPGA比较后,选择了Altera公司的Cyclone系列的FPGA EP1C6Q240C6。该款FPGA的I/O引脚可工作在 464 MHz,并支持LVTTL、LVCOMS、LVDS等多种电平标准,可满足项目设计的需求,且有较好的性价比。

2 总体方案设计

图1是合成脉冲脉宽调整电路的基本原理框图,其基本原理是将输入的时钟信号送给FPGA内部的窄脉冲形成模块以形成窄脉冲信号,再将该窄脉冲信号经过选择信号选择后产生上升沿触发信号和下降沿触发信号,把这两个信号送出FPGA,经过电平转换后将上升沿触发信号送入D触发器的时钟端,下降沿触发信号经过脉宽微调模块后送入D触发器的清零端,同时D触发器的D端一直接逻辑高,这样最终实现脉冲的形成和脉冲宽度的可调[1-5]。

图1 合成脉冲脉宽调整电路

FPGA内部功能主要由窄脉冲形成模块及脉宽粗调模块实现,其中窄脉冲形成模块又由时钟信号输入时的高低频不同而分为高频窄脉冲形成模块和低频窄脉冲形成模块。在设计中,高低频的区分是以50 MHz这个频点做为分界点的,时钟频率大于50MHz时为高频,小于等于50MHz时为低频。选择50MHz为分界点的原因在于该设计采用的是FPGA内部粗调和延迟芯片微调共同实现脉宽的调整,而脉宽微调是由2片级联的可编程延迟芯片实现的,其可调范围为20ns,所以在脉宽粗调时采用的计数时钟频率必须是大于50 MHz的,即周期总是小于20ns的,这样才能结合可编程延迟芯片保证达到脉宽连续可调的设计要求。

综上所述,FPGA内部实现脉宽粗调的具体实现方式为:当时钟输入大于50 MHz(高频)时,将上升沿触发信号同时作为下降沿触发信号直接从FPGA输出;当时钟输入小于等于50MHz(低频)时,将形成的低频段窄脉冲信号分为两路,一路作为上升沿触发信号直接从FPGA输出,另一路经过脉宽粗调后作为下降沿触发信号从FPGA输出。

3 具体电路设计

3.1 极窄脉冲产生电路

因为设计要求脉冲宽度为2ns~(周期-2ns),所以下降沿触发信号必须为脉冲宽度小于2 ns的极窄脉冲。因为如果下降沿触发信号的脉冲宽度大于2ns,要么不能产生最大脉冲宽度为(周期-2ns)的脉冲信号;要么就是在下一个上升沿触发信号来临的时候上一个周期的下降沿触发信号还保持有效,在合成脉冲时D触发器不能在预定的时刻翻转,导致不能正常的产生脉冲信号,所以必须将下降沿触发信号整形成为极窄脉冲信。

如图2极窄脉冲产生电路所示,该电路采用FPGA内部逻辑实现[6-10],并实际测得其产生的极窄脉冲宽度约为1.4ns,能够满足设计中下降沿触发信号脉宽小于2ns的要求。这个电路虽然简单,但却是实现最大脉冲宽度(周期-2ns)的关键。

3.2 脉宽粗调模块

如图3脉宽粗调模块所示,该模块由脉宽粗调计数器和一个极窄脉冲产生电路组成。

图2 极窄脉冲产生电路

图3 脉宽粗调模块

脉宽粗调计数器共有3个输入端和一个输出端,3个输入端分别是 clk,pw[15..0]和load;一个输出端为out。

clk是计数器的计数时钟输入端;pw[15..0]是计数器的脉宽预置值输入端,它决定计数器的计数值,计数时钟周期乘以脉宽预置值则决定了脉冲宽度的粗调量;load输入端是计数器脉宽预置值的载入端,load为1则载入脉宽预置值,load为0则脉宽粗调计数器开始工作。

输出端out信号的初值为0,当脉宽粗调计数器计数到脉宽预置值后,out信号变为1,即产生一个上升沿,该上升沿再经过一个极窄脉冲产生电路后产生下低频段时下降沿触发信号。

3.3 脉冲合成电路

如图1合成脉冲脉宽调整电路的基本原理框图所示,D触发器是合成脉冲信号的最后一级,是产生设计所要求的一定脉冲宽度的脉冲的重要电路。设计中选用ONSEMI公司型号为MC100EP51的D触发器[4]。之所以单独选用一片D触发器来合成脉冲而不用FPGA内部D触发器来合成最终的脉冲信号,是因为如果把下降沿触发信号经过脉宽微调后再送入FPGA配合上升沿触发信号与内部D触发器合成脉冲后再送出FPGA,由于FPGA内部布局布线和D触发器之前复杂逻辑所带来的不确定性会影响信号质量,严重时会使电路时序混乱,导致电路不能正常工作;再者,如果先在FPGA内部合成脉冲信号后再输出,这样就不能对脉冲宽度进行微调[1-2,5-10]。

设计中所选触发器为PECL型D触发器,并带有温补网络,能够在-40℃~85℃的温度范围内保持良好的工作特性,最大工作频率大于3 GHz,建立时间是80 ps,保持时间是40 ps,固定传播延时350ps。由于设计需要实现250MHz的脉冲信号,而方波信号含有大量的谐波成分,3 GHz的带宽已经是250MHz的10倍多,能够保证脉冲信号5次以内的谐波分量不被滤除,能够很好的保持脉冲信号的完整性。80ps的建立时间和40ps的保持时间能够保证脉冲信号能够在上升沿触发信号和下降沿触发信号极窄的情况下快速的触发和清零,保证脉冲合成的高效和稳定。所以选择该触发器可以很好满足设计需求。

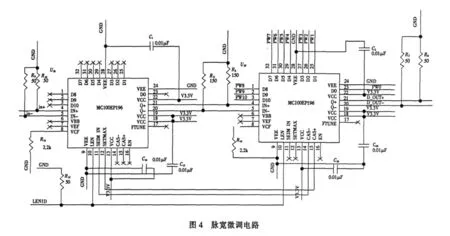

3.4 脉宽微调电路

由于单纯依靠FPGA内部的脉宽粗调计数器对脉宽进行调整是不能满足脉宽可调分辨率为10 ps的设计要求。所以必须在FPGA外部进行脉宽微调来满足设计要求。该电路所选用的是ONSEMI公司的可编程延迟芯片作脉宽微调,该可编程延迟芯片型号为MC100EP196,其主要参数为:最大工作频率大于1.2 GHz,固定延迟为2.4 ns;可调延迟范围为0~10 ns;分辨率为 10 ps;并行输入数据端 D[0∶9]可兼容 LVTTL、LVCOMS和 ECL电平,设计中选用 LVTTL电平[3]。

如图4脉宽微调电路所示,设计中选用两片可编程延迟芯片级联的方式构建电路,这样可调脉宽范围为0~20 ns,而其10 ps的分辨率也正好满足设计要求。

具体脉宽微调原理如下:由设定的所需脉宽值和FPGA内部脉宽粗调值共同计算出脉宽微调值,将该值转化为延迟芯片的控制字,通过FPGA将该控制字配置好并通过延迟芯片的len信号将其载入延迟芯片即可。

4 实验结果与分析

图5中(a),(b)所示是用泰克公司的 TPO7104示波器作为测试仪器所测得的实测数据及波形图。

设置时钟频率为100MHz、脉冲宽度为5ns时,如图5(a)所示,测得的实际脉冲宽度为5.27ns。

设置时钟频率为10MHz、脉冲宽度为5ns时,如图5(b)所示,测得的实际脉冲宽度为5.322ns。

由实际测得结果可知,不同时钟频率所测得的脉宽实际值和所设置值之间有一定误差,但该误差值基本相等,约为0.3ns。经过在其他时钟频率时的多次测量,可以看到所测脉宽值和设置脉宽值也同样存在该固定误差。经分析,该误差的产生是FPGA内部走线和绘制电路板时布局布线的影响所致,但该固定误差不影响所预想的指标。综上所述,该设计所用方法可以实现预想目标。

[1]John F.wakerly.数字设计原理与实践[M].北京:机械电子出版社,2003.

[2]冼 进,戴仙金,潘懿萱.Verilog HDL数字控制系统设计实例[M].北京:中国水利水电出版社,2007.

[3] ONSEMI.MC100EP196 3.3 V_ECL programmable delay chip[DB/OL].http://www.onsemi.cn.

[4] ONSEMI.MC100EP51 3.3 V/5 V_ECL D flip_flop with reset and differential clock[EB/OL].http://www.onsemi.cn.

[5]MAXIM.Single LVDS/anything-to-LVPECL translator MAX9375[DB/OL].http://www.maxim-ic.com.cn.

[6] 褚振勇,齐 亮,田红心,等.FPGA设计及应用[M].西安:西安电子科技大学出版社,2006.

[7]Zeiaman B.基于FPGA/CPLD的数字IC设计方法[M].北京:北京航空航天大学出版社,2004.

[8] 吴继华,王 诚.设计与验证Verilog HDL[M].北京:人民邮电出版社,2006.

[9] 夏雨闻.Verilog数字系统设计[M].北京:北京航空航天大学出版社,2003.

[10]Altera.Cyclone device handbook,volume1[DB/OL].http://www.altera.com.