12位电容电阻混合式SAR ADC IP核的设计

裴晓敏,吴学军,宋立新

(襄樊学院 物理与电子工程学院,湖北 襄樊 441053)

模数转换器(ADC)是模拟系统与数字系统接口的关键部件。在各种类型的模数转换器中,逐次逼近型的模数转换器(SAR ADC)具有中等的精度和中高分辨率。因其转换过程中只使用1个比较器对输入电压和1个N位数/模转换器(DAC)输出进行比较,其芯片面积及功耗均小、性价比高,有着良好的应用前景,是目前应用最多的模数转换器类型。

IP设计过程中采用正向设计方法:从芯片定义—系统设计—电路设计—电路仿真—版图绘制以及流片,实现了12 bit的适用于工业控制器的SAR ADC IP核的设计。为了在IP核的面积和性能之间进行合理的折衷,在内置DAC的设计过程中,综合比较了多种结构的优缺点,采用了电阻电容混合式的DAC结构。同时,为了使SAR ADC获得更好的性能,设计中对DAC结构中的电容阵列进行优化设计,以减小微分非线性误差,保证输出数码的单调性。

1 IP核的基本结构与工作原理

图1为整个IP的功能结构。它由时钟产生器、逐次逼近寄存器(SAR)和控制逻辑(ControlLogic)、电阻串(R_string)和电容阵列(Cap_array)构成的内置 DAC、比较器等组成。

图1 整个IP的功能结构图

工作原理:先将模拟输入电压VIN以电荷的形式存储在电容节点上,然后,将N位寄存器设置为中间值(即100...0),以执行二进制查找算法。此时DAC的输出VDAC为外接参考电压VREF的1/2;之后,执行一个比较操作,如果VIN<VDAC,比较器输出逻辑低,N位寄存器的最高位清 0;如果 VIN>VDAC,比较器输出逻辑为高(或 1),N 位寄存器的最高位保持为1;其后,SAR的控制逻辑移动到下一位,将该位强制置为高,再执行下一次比较。SAR控制逻辑将重复上述顺序操作,直到最后一位。当转换完成时,寄存器中就得到了1个N位数码。

SAR ADC的速度受限于:(1)内部DAC的建立时间。在这段时间内必须稳定在整个转换器的分辨率以内。(2)比较器的速度。比较器必须在规定的时间内能够分辨VIN与VDAC的微小差异。因此,DAC和比较器的设计是整个SAR ADC设计的关键。

2 内置DAC的设计与优化

图2为传统的电阻电容DAC结构,M位MSB位采用电荷按比例缩放的子DAC,而K位LSB位采用电压按比例缩放的子DAC。经过面积和精度的折中考虑,设计时通常取 M为 5,K为 7。

图2 传统C-R混合结构DAC

2.1 传统C-K结构DAC优缺点

(1)优点:采用了在最大最小组件比和分辨率之间进行权衡的方法,使匹配精度不会随DAC的分辨率的增加而下降,同时DAC需要的面积也相应地有所减小。而且MSB位由电容组成,工艺上它的精度与电阻串组成相比更高。而LSB采用电阻串构成,是单调的,整体的性能不会出现非单调性。

(2)缺点:传统结构中,16C、8C、4C,2C 等分别为集总型的电容连接结构,转换时,每一组集总电容的下极板在各位的逼近代码为1或0的控制下分别接VREF或地,由于电容之间的匹配误差和单调性难以保证而容易产生 DNL误差。以一个 6 bit的 C-R结构为例(M=3,K=3),其传统的集总电容阵列结构如图 3所示。4C由C1、C2、C3、C4集总而成,2C由 C5、C6集总。 如果输出代码为 001_111 时 ,C1、C2、C3、C4 和 C5、C6 接 地 ,C7 接VREF,附加电容 C8 总是固定接 V′REF,而此时 V′REF=7/8×VREF,则等效总电容 Ceq=C7+C8×(7/8);如果下一个输出代码为 010_000,则 Ceq=C5+C6;因此,C7、C8 及 C5、C6在版图设计和制造过程产生的匹配误差将直接导致DNL误差,影响IP核的动、静态性能。

图3 传统的集总电容阵列

2.2 优化设计分析

针对上述误差因素,IP核设计首先从电容阵列的结构出发,对传统的C-R结构进行了优化,如图4所示。电容阵列由相同的单位电容组成,所有电容并不集总在一起,每一个单位电容都有可能接VREF或 V′REF。

图4 非集总电容阵列结构

以代码 001_111为例,此时 C1接 VREF,而 C2接 V′REF,则:

当代码增加1个LSB为010_000时,C1和C2接VREF,则:

由公式可以看出,虽然输出代码增加了1个LSB,但是连接的相关电容并没发生任何变化,因而可极大地降低DNL误差。

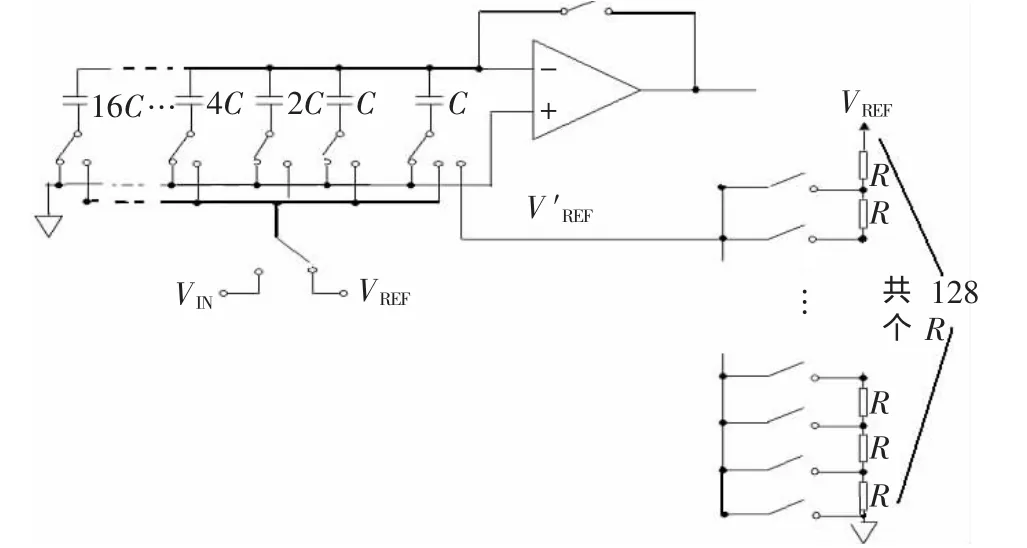

同理,在12位的SAR ADC IP核的设计过程中,把MSB位DAC中的16C:8C:4C:2C:C:C电容阵列变为由32个单位电容C组成的非集总电容阵列结构,改进的C-R结构如图5所示。

图5 改进的C-R混合结构DAC

逐次逼近过程中,由于SAR的逻辑控制不同,而使电容的连接方式不同。D[11:0]从 100 000 000 000开始进行逼近转换,此时前面的16个单位电容接VREF,第 17个电容接V′REF,其他的电容接地。如果比较器的最终比较结果大于1,则最高位的 1保留,D[11:0]变为110 000 000 000,此时前面的 24个电容接 VREF上,第 25个电容接到V′REF,其他的电容接地。如果比较器的最终比较结果小于 1,则 D[11:0]变为 010 000 000 000,则前面的 8个单位电容接到 VREF,第 9个电容接 V′REF,其他的电容接地。依此类推,最终在转换结束后,并行输出寄存的D[11:0]的值,即得到所需要的转换结果D[11:0]。

转换过程中,利用数字逻辑的控制,输出代码每增加1个LSB,所连接的电容并不会发生变化,这样可极大地降低DNL误差,从而实现较好的静、动态特性。

3 采样、转换电路分析及比较器的设计

3.1 采样、转换过程分析

由于电路DAC中电容阵列的存在,采样保持电路直接镶嵌在DAC之中。因模拟输入为单端信号,为了减小噪声干扰,比较器采用准差分结构。在比较器的反相输入端接入1组与采样电容完全相同的dummy电容,并且dummy电容全部接地。结构如图6所示。

图6 采样、转换电路

采样时,图中的32单位电容全部接模拟输入VIN,同时开关S1闭合,第1级比较器的输入输出电压最终被拉至一相同的电平Vdummy=VIN,即采样电压 VIN以电荷的方式存储在输入电容节点上。

转换时,反馈开关 S1断开,Vdummy=VIN保持不变,电容上存储的电荷Q不变。下一个时钟周期,开始进行逼近转换。VDA随着逼近代码的转变而改变,通过比较器判断 VDA与 VIN的大小,若 VDA>VIN,比较器的输出为 0;VDA<VIN,比较器的输出为 1。

3.2 比较器的设计与优化

比较器由两级结构相同的前置放大器和一级带有复位再生的高速锁存器组成。前置放大器使输入的变化足够大,其输出被接入到锁存器的输入端,这样的组合电路具有最佳特性。传统的前置放大器结构如图7所示,由1个差分输入对、1个伪电流源和1对交叉耦合负载组成的一种内置正反馈比较器。

为提高比较器的翻转速度,在前置放大器的设计上也进行了简单的优化,如图8所示:(1)增加复位功能。利用RS与两个相反时钟信号来控制比较器的复位,当 RS为高时,比较器处于复位状态;RS为低时,比较器开始进行比较。通过每次比较前的复位,可以进一步提高比较器的翻转速度;(2)在两输出端之间增加2个钳位(clapping)二极管,用来控制两个差分输出端的电压差。即限制Vo1和Vo2电压的摆幅,提高比较器的速度。

图7 前置放大器电路

图8 优化后的前置放大器的设计

4 版图设计及仿真结果

4.1 版图设计

整个 IP版图设计采用 0.18 μm的 IP6M的工艺,面积较小,仅为 810 μm×410 μm。

4.2 仿真结果

抽取寄生参数后的仿真结果如表1所示。

表1 Fvin=19 kHz的仿真结果

图9为用仿真结果所画的SAR ADC输出代码的FFT图形。

图9 Fvin=19.35 kHz时的FFT_PLOT

本文在深入分析SAR ADC的基础上,实现了12 bit的适用于工业控制器的SAR ADC IP核的设计。为提高IP核的性能,设计对C-R混合式的DAC结构中的电容阵列进行了改进,采用了一种新的非集总的电容结构,并且还进一步优化了比较器的设计。

芯核采用 0.18 μm CMOS Mix_singal IP6M 工艺,分别采用3.3 V的模拟电源电压和1.8 V的数字电源电压供电。 IP 核的 面积为 800 μm×420 μm,FF case(VDDA=3.63 V VDDD=1.98 V VREF=3.63 V)下功耗为 1.2 mW,DNL<0.5 LSB,实现了12 bit的低功耗、芯片面积小的SAR ADC IP核的设计。

[1]PHILLIP E,ALLEN D R H.CMOS analog circuit design(Second Edition)[M].Oxford University Press,2005.

[2]CHANG Y K, WANG C S, WANG C K.A 8bit 500KS/s low-power SAR ADC for biomedical applications[C].in Proc.IEEE Asian Solid-State CircuitsConf.(ASSCC),2007:228-231.

[3]HAMMERSCHMIED CM.CMOSA/Dconvertersusing MOSFET-only R-2R ladders[D].Swiss Federal Institute of Technology,Zurich.2000.

[4]ELZAKKER M.A 1.9 μW 4.4fJ/conversion-step 10b 1MS/s charge redistribution ADC[C].International Solid State Circuits Conference(ISSCC),2008:244-246.

[5]BOSCH A V.A 10 bit 1 G sample/s nyquist current-steering CMOS D/A converter[J].IEEE J.Solid-State Circuits,2001,36(3):315-323.