一种基于数字AGC的定点字长控制算法研究与实现

沈智翔,万明康,于宏毅

(信息工程大学 信息工程学院,河南 郑州 450002)

目前以数字信号处理为核心的软件无线电得到越来越广泛的应用。在工程实现中,数字信号在FPGA、DSP以及其他各种数字信号处理芯片中多采用定点计算,所以处理流程中的定点字长与量化误差是必须考虑的问题。

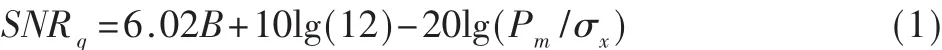

数字信号采用有限位二进制数表示,假设A/D量化误差为均匀分布白噪声且与信号不相关[1],则经B bit均匀量化后,量化信噪比[2-3]可表示为:

对于零均值高斯信号可取Pm/σx=3,在 8 bit量化时量化信噪比约为50 dB。可见在保持一定有效量化位数的情况下量化信噪比是比较高的。但实际应用中信号经过一级运算后结果往往会超出规定字长,需要进行截短处理。多次截短产生的误差会不断累积,同时需要考虑如何保证一定的有效量化位数。如选择简单的取高位截短,在多级处理后有效量化位数可能远小于字长,带来信噪比损失和计算效率的降低。因此,实现时需针对具体算法流程进行定点设计,这样就大大降低了处理算法的灵活性和通用性。本文通过建立信号多级定点处理模型,对字长选取和截短问题进行分析,提出了更为灵活通用的数字信号处理字长选取策略及字长截短控制处理算法。

1 信号模型

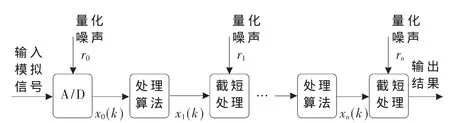

连续随机信号经过等间隔采样量化后得到离散随机序列 x0(k),k=0,1,2…,一次信号处理的运算结果可看作该随机序列经过系统后的输出序列:x1(k),k=0,1,2…,输出序列经过字长截短后进入下一级处理。则经 n次处理后依次得到输出序列x1(k),x2(k)…xn(k)。假设每次截短带来的截短误差相互独立,便可以将截短误差等效为处理流程中依次引入的若干个噪声源,从而得到信号多级定点处理模型如图1所示。

图1 信号多级定点处理流程图

模型中以截短处理为节点,将信号处理流程划分为多级。模型假设A/D满量程采样,采样序列为零均值平稳序列,处理算法均为线性处理。

2 多级处理中的字长选取

当一次运算输出结果超出规定字长时,需要进行尾数截短。截短处理相当于重新量化,可由截短量化噪声的产生、噪声过系统及量化信噪比损失等方面,考虑字长选取问题。

2.1 截短量化噪声分析

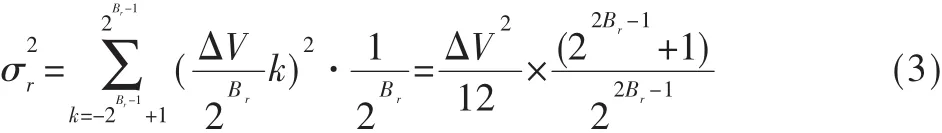

式(1)中A/D量化误差取值是连续的,服从均匀分布,而截短量化误差是取值非连续的数字序列。若截去字长为Br,则量化噪声有 2Br种取值,可认为其满足离散均匀分布,各取值出现的概率相同,均为1/2Br。

若被截短数据为有符号数表示,则对负值数据,量化噪声取值范围为[-ΔV/2,ΔV/2],均值为-ΔV/2Br+1。 根据数据序列的零均值假设,可认为总的量化噪声均值为零,则方差为:

由式(2)、式(3)可得,截短量化噪声功率由最小量化电平 ΔV=Pm/2B′以及截短字长 Br决定。 随着 Br的增加趋近于均匀分布:均值趋近于零,方差趋近于ΔV2/12。

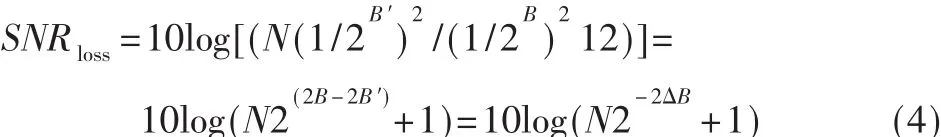

2.2 截短处理的量化信噪比损失

其中B为 A/D量化位数,B′为截短后保留字长,ΔB=B′-B。不同截短处理次数、不同保留字长下的量化信噪比损失如图 2。

图2 截短后量化信噪比损失

图中N为截短次数,N增加则量化信噪比损失增大;当 ΔB为负时,量化信噪比损失较大,ΔB=2时损失小于3 dB。综上可得,在实际A/D量化信噪比较高的情况下,算法保留字长只要大于A/D量化字长(3~4)bit,就可以大大降低截短量化噪声的影响。

3 数据截短处理算法

假设在L位字长中保留B位,则保留高B位可保证不溢出,但无法保证有效量化数。即量化器的满幅度值与信号均方差的比值Pm/σx可能变得较大,而信号实际只占用满量程的一部分。

3.1 截短位置的等效增益因子

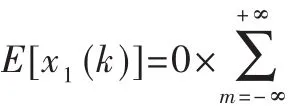

3.2 基于数字AGC的截短位控制算法

在实际系统中应用的截短处理算法,需要能够应对较复杂的处理流程,适应输入信号的变化。通过建立前馈自动增益控制模型[4-5]确定增益因子,可较好地完成截短位的自适应调整。首先采用参数估计的方法计算信号均方差;而后将均方差的估计值与参考值R=Pm/3比较,其中α为误差信号修正系数,通过迭代收敛到最佳增益值。实现流程如图3。

图3 截短位控制算法流程

实现过程中,复杂度较大仍是该模型的一个主要缺点。尤其在多次截短处理时,为进一步降低计算复杂度,可以采用直接统计信号动态范围方法代替均方差估计。

设信号均值为零,动态范围表示为[+Xm,-Xm],Xm为信号幅度的最大值。以分段统计最大幅值代替均方差估计。若样本长度为M,参数估计时需进行M次乘累加运算和一次除法运算,而最大幅值统计只要进行M次比较。理论参考值可取R=2B-1-1,为保留字长所能表示的最大幅值。与参数估计相比,模型输出随机误差相对较大,需要保证足够的统计长度,并判断剔除错误数据以保证稳健性。

4 FPGA仿真与实现

下面通过基于FPGA的仿真实现在实际信号处理流程中对算法进行验证。经宽带采集的中频信号在FPGA中完成数字变频、采样率变换以及数字滤波等处理,基本流程如图4。

图4 信号处理定点仿真流程图

仿真信号由载波频率分布于 0.3 MHz~1.4 MHz范围内的若干路QPSK信号组成,码元速率 64 kb/s,升余弦成型,滚降系数 0.5,采样频率 3.072 MHz,8 bit量化。信号在计算机中生成并量化,以初始化文件的形式下载至FPGA的RAM中。

FPGA采用Altera公司的Stratix II EP2S90,读取采样信号后,首先经过正交下变频,数字频率合成模块输出字长为16 bit。而后进行降采样,包括一级3阶CIC滤波器和两级14阶半带滤波器,将采样率降至256 kHz,最终经过一级高阶FIR低通滤波器提取出一路信号。在正交下变频、降采样和FIR滤波器后进行字长截短,每次截短保留12 bit字长。所有滤波器基于FIR Compiler生成,双通道完成实部与虚部的滤波,输入字长12 bit,系数字长16 bit。

正交下变频为8 bit与16 bit的乘法,输出字长24 bit;CIC滤波采用级联的方式增加阻带衰减,输出字长16 bit;FIR Compiler在滤波器生成时会根据滤波器系数和输入字长自动确定输出字长:HB滤波器输出字长28 bit,FIR滤波器输出字长29 bit。则5次截短分别需截去 12 bit、4 bit、16 bit、16 bit、17 bit。 算 法 中 求 对 数 取 整 运 算 通 过查找表实现,在SignalTap II Logic Analyzer中采集仿真结果。表1给出3组不同信号收敛后的移位长度Ba。

信号一为功率相等的2路QPSK信号,中心频率分别为1 MHz和 1.1 MHz,下变频频点为 1 MHz;信号二为8路功率相等的QPSK信号,中心频率分布于0.3 MHz~1.4 MHz范围内,下变频频点为 960 kHz;信号三在信号二的基础上随机调整了信号功率。误差信号修正系数取α=0.5,参数估计模型中采用滑动窗进行方差估计,滑动窗长取500点,最大值统计模型中分段统计长度为500点。2种模型取整后的输出结果与参考值一致,参考值为由信号实际取值范围得到的理想截短方案,可以看出在不同的信号条件下,理想移位长度Ba是不同的。若进行取高位截短,对于信号一将损失3 bit有效量化位,而对于信号三将损失8 bit有效量化位。

表1 3组信号截短方案仿真结果

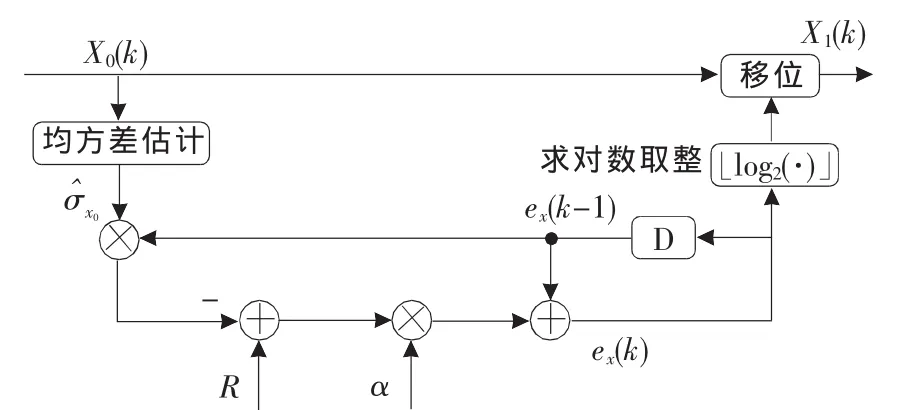

为进一步检验模型的收敛跟踪性能和输出结果的方差,将取整前的输出结果进行对比。采集查找表前的输出数据,在Matlab中取对数并做出曲线图。2种模型样本长度M取500点和200点时的跟踪收敛曲线如图5。

图5 字长控制算法取整前输出

图5中横坐标为样点数,纵坐标为DDC后截短移位长度(取整前)。输入信号在2 400采样点处由信号二变为信号三,在7 200点处由信号三变回信号二。样本长度相同时,参数估计模型抖动较小,而动态范围统计模型则相对较大,相比较而言前者更加充分地利用了样本数据,受随机性影响较小。参数估计模型收敛跟踪速度与滑动窗长有关;最大值统计对于信号动态范围增大的情况能够快速跟踪从而避免溢出(7 200点处),而信号动态范围减小时输出有一个样本长度左右的延迟(2 400点处)。

本文从两个方面分析了定点计算中的有限字长保留问题。首先将字长的截短等效为重新量化,分析了量化信噪比损失及计算中所需的最小保留字长;而后讨论了最佳截短方案及其实现,将截短位选择等效为信号增益调整,利用自动增益控制模型完成实时信号截短处理;最后通过硬件仿真,在典型软件无线电处理流程中对算法进行了验证,并对比讨论了基于参数估计与最大值统计两种模型的计算量和算法性能特点。本文关于定点计算有限字长保留问题的分析和实现,在工程实现中有实际参考价值和应用价值。

[1]WIDROW B, KOLLAR I, LIU M C.Statistical theory of quantization [J].IEEE Transactions on Communications,1964,12(4):162-165.

[2]陈亮,杨吉斌,张雄伟.信号处理算法的实时 DSP实现[M].北京:电子工业出版社,2008.

[3]丁玉美.数字信号处理[M].西安:西安电子科技大学出版社,2000:262-290.

[4]GUESALAGA A, TEPPER S.Synthesisofautomatic gain controllers forconicalscan tracking radar[J].IEEE Transactions on Aerospace and Electronic Systems,2000,36(1):302-309.

[5]JOHNSON C R.软 件 无 线 电 [M].北京:机械工业出版社,2008.