基于FPGA的IRIG-B(DC)码产生电路设计

雒俊鹏

(中国电子科技集团公司 第 39研究所, 陕西 西 安 7 10065)

在测控系统中,时统信息不仅是各个分系统工作的基础,也是有些分系统进行测控时推算弹道和其他复杂运算必不可少的信息,IRIG-B时间码作为一种重要的时间同步传输的方式,成为时统设备首选的标准码型。IRIG全称Inter-Range Instrumentation Group(靶场间测量仪器组)。IRIG串行时间码,共有6种格式。即IRIG-A、B、D、E、G、H,IRIG-B(DC)码又分为DC和AC码,DC码的接口通常采用TTL接口和RS422(V.11)接口。

1 IRIG-B(DC)码介绍

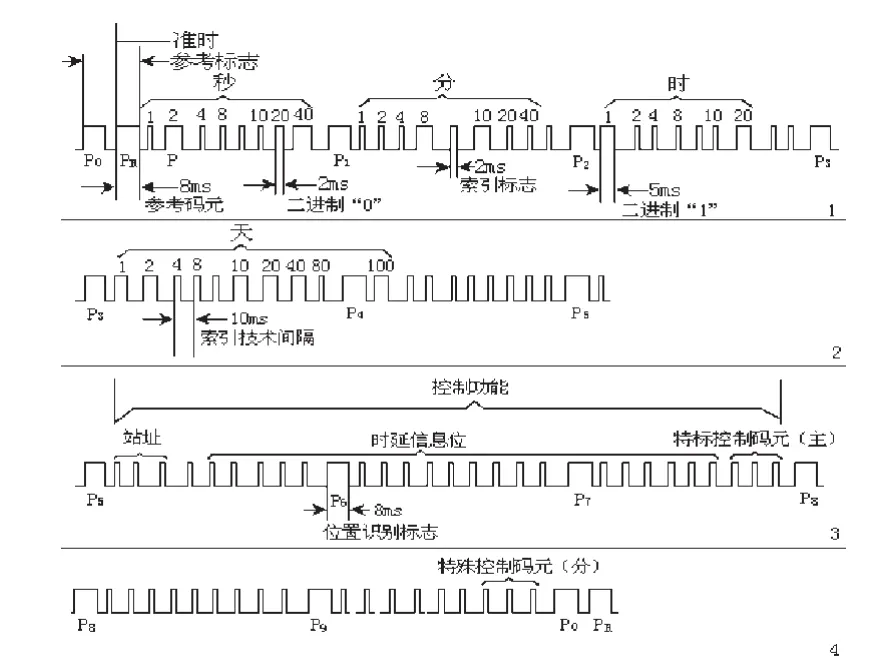

IRIG-B(DC)码的时帧速率为1帧/s;可传递100信息位,每个信息位宽度10 ms,称为一个码元,每10个码元为1组。每帧有一个高电平宽度8 ms、低电平宽度2 ms的起始码元PR和结束码元P0,PR和P0之间有P1、P2、…,P9标志码元,标志码元之间包含秒、分、时、天和控制功能等信息,码元高电平宽度5 ms代表二进制的“1”,高电平宽度2 ms代表二进制的“0”,IRIG-B(DC)码的示意图如图1所示。

2 系统硬件电路设计

图1 IRIG-B(DC)码示意图

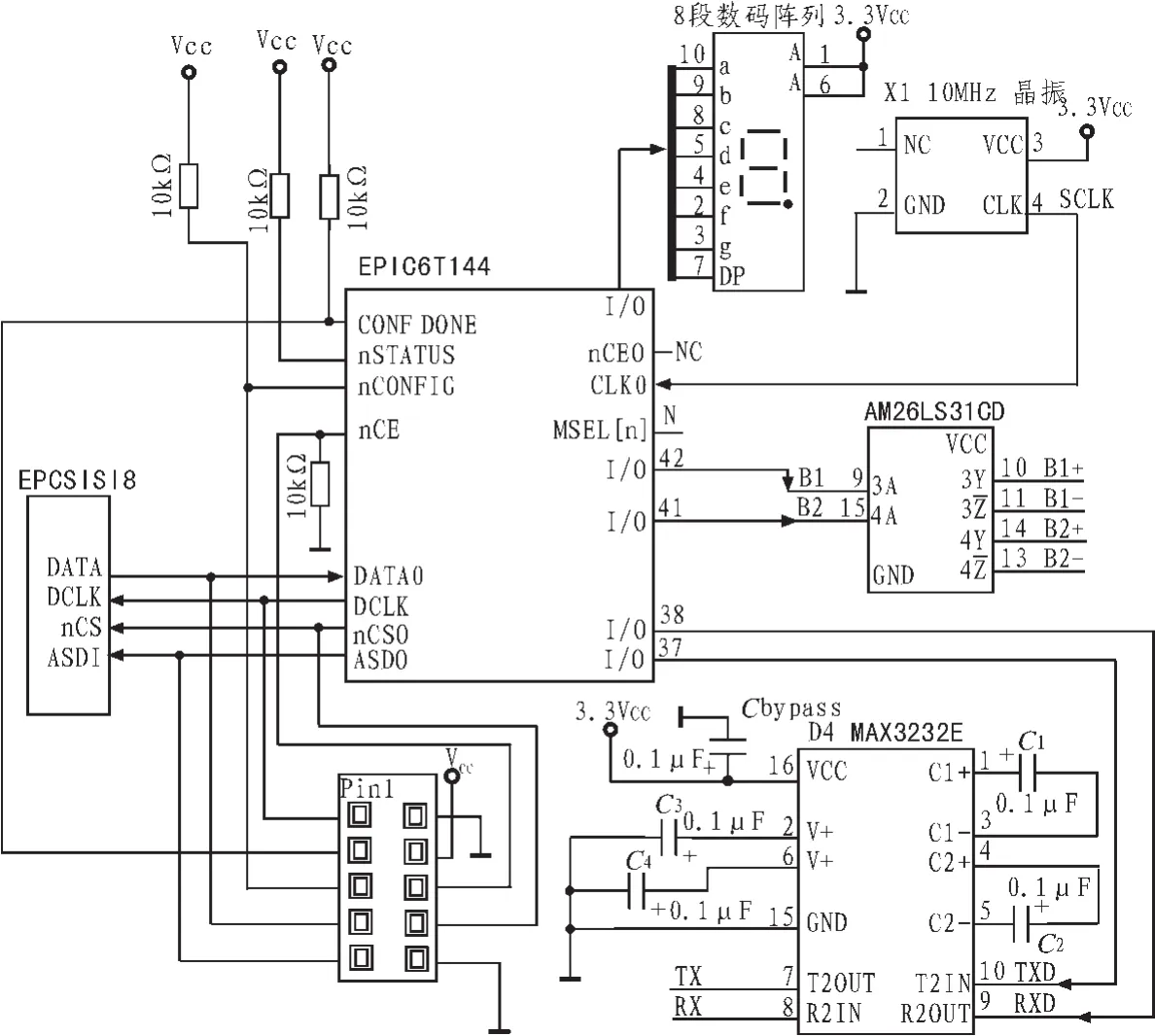

本设计的硬件电路如图2所示,采用Altera低功耗、低成本Cyclone FPGA系列的EP1C6T144,总引脚数144,I/O引脚数98,有3种配置方式,分别为AS方式、PS方式和JTAG方式,本设计采用AS方式,当使用AS方式时,必须将FPGA EP1C6T144的MSEL0和MSEL1这2个引脚接到低电平,即为逻辑的00,AS方式还需与一片串行配置器件并用[1],本设计采用低成本的Altera公司的EPCS1SI8,具体连接如图2所示,采用这种方式上电后可直接通过下载电缆对FPGA进行编程,使用灵活方便。在设计时注意引脚上的上拉电阻和下拉电阻必须连接上。

晶体振荡器采用10 MHz晶振,将晶振的SCLK输出引脚与EP1C6T144的CLK0输入引脚连接,检测晶振信号脉冲的上升沿并进行计数,以此计数作为时间基础。

图2 系统硬件电路图

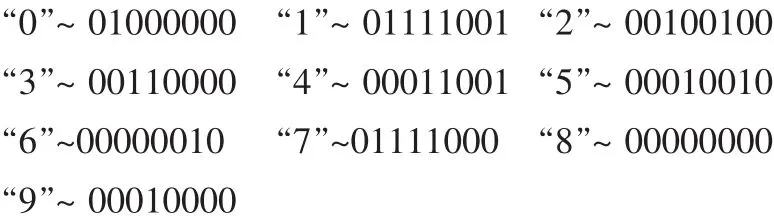

选择EP1C6T144的37引脚作为异步串行输出引脚,与MAX3232E的10引脚(T2IN)连接,将从FPGA出来的TTL电平转换为串行输出电平从7引脚(T2OUT)输出,串行电平转换器采用MAX3232E。选择EP1C6T144的41、42引脚作为2路IRIG-B码信号输出[1],因为IRIG-B(DC)码采用RS422电平输出,而从EP1C6T144的41、42引脚输出脉冲是TTL电平,所以必须进行电平转换,本设计采用TI公司的AM26LS31CD差分驱动器。采用8段数码管作为时间显示器件,显示的信息有天、时、分和秒,共需9个器件,每个8段数码管的0~9个数字显示逻辑为:

3 系统软件程序设计

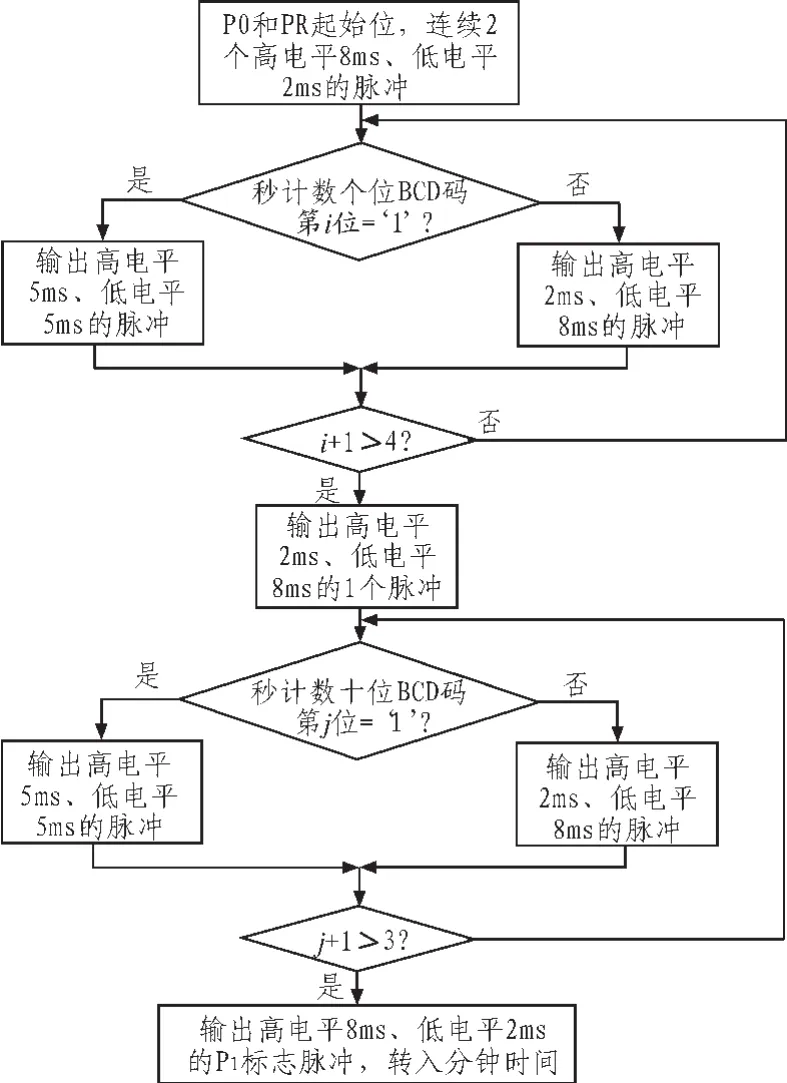

使用VHDL硬件描述语言进行编程,编译环境采用Altera公司的Quartus II 7.1[2]。根据图1所示B码脉冲序列宽度图谱,以秒的B码串产生为例,说明VHDL编程设计过程,流程图如图3所示。分、时和天的软件设计根据图1所示的B码示意图,参考秒的设计流程来设计,将100个码元对应的脉冲串按照图1的脉冲宽度输出,就形成整个一帧IRIG-B(DC)码的脉冲串[2-6]。

4 电路仿真

图3 秒时间B码生成软件流程图

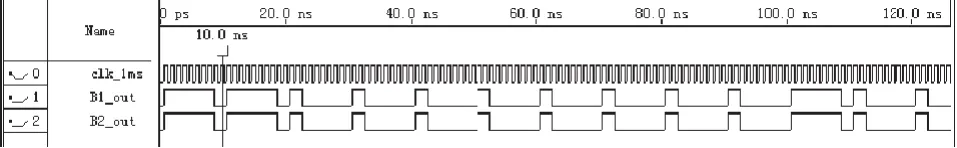

图4 电路仿真脉冲输出图

电路仿真脉冲输出[6]如图4所示,图中B1_out和B2_out是IRIG-B(DC)码的输出脉冲,clk_1ms是根据晶体振荡器输入脉冲而产生的模拟1 ms信号脉冲,可以看出,当连续8个clk_1ms的脉冲时,B1_out和B2_out保持高电平,即保持了8 ms的高电平,后面的脉冲都严格的遵守图1所示的IRIG-B(DC)码的规则。

5 结论

通过仿真和实际使用表明,该设计电路所产生的IRIG-B(DC)时间码稳定、连续、准确,电路板功耗低、成本低,操作灵活简单,在测控领域有广阔的应用前景。

[1]Altera公司.Cyclone device handbook[EB/OL].2008.http://www.altera.com.cn/literature/hb/cyc/cyc_c5v1.pdf.

[2]曾繁泰,陈美金.VHDL程序设计[M].北京:清华大学出版社,2001.

[3]郑燕,赫建国,党剑华.基于VHDL语言与QuartusII软件的可编程逻辑器件应用与开发[M].北京:国防工业出版社,2007.

[4]Pedroni V A.VHDL数字电路设计教程[M].乔庐峰,译.北京:电子工业出版社,2005.

[5]吴继华,王诚.Altera FPGA/CPLD设计[M].北京:人民邮电出版社,2005.

[6]周润景,图雅,张丽敏.基于QuartusⅡ的FPGA/CPLD数字系统设计实例[M].北京:电子工业出版社,2007.