CORDIC算法数字瞬时测频的FPGA设计与实现

伍小保,王 冰,何 勤

中国电子科技集团公司第三十八研究所,安徽合肥 230088

CORDIC算法数字瞬时测频的FPGA设计与实现

伍小保,王 冰,何 勤

中国电子科技集团公司第三十八研究所,安徽合肥 230088

数字瞬时测频(DIFM)技术是现代电子战中的关键技术之一,要求在极短的时间内完成对输入信号频率的测量。瞬时测频的基本思路是将频率信息转化为相位信息,再把相位信息转化为幅度信息,通过对幅度信息量化编码,从而完成对频率的测量。本文提出了基于数字下变频、CORDIC算法相位测量以及相位推算法的数字瞬时测频方法以及在FPGA中的实现,对单频信号该方法具有测频精度高、瞬时性好的优点,特别适合现代电子战接收机数字瞬时测频的需求。

数字下变频;CORDIC算法;数字瞬时测频;FPGA

0 引言

现代电子战环境下,雷达、通信信号非常密集,在同一个时间内会有多个信号出现,且频率覆盖范围广,为实现对这些同时信号的全概率覆盖,侦察接收机一般采用模拟和数字信道化技术,将一组固定通带滤波器输出的数字信号进行快速、宽频带、全概率的粗测频,然后再对各通道中被检测出的信号进行相对窄带、高精度的精测频[1]。信号经过信道化处理后,如果子信道的带宽取得比较窄,则每个信道输出一个信号的概率比较大,此时可以采用一些时域测频算法进行测频,如相位推算法、瞬时自相关法、曲线拟合法和过零检测法等方法。其中相位推算法具有运算量小、速度快、精度高、利用很少采样点就可以实现频率的估计,特别适合实时处理的场合,因此是DIFM精测频的比较好的方法。

本文提出了基于数字下变频的数字正交化、CORDIC算法的相位测量的相位推算法数字瞬时测频方及其在FPGA中的工程实现,该方法适用于信道化后的单频信号的高精度、快速频率测量,在窄脉冲的情况下也可以获得比较好的测量精度,同时该方法也适用于线性调频信号的调频参数测量。

1 CORDIC算法数字瞬时测频基本原理

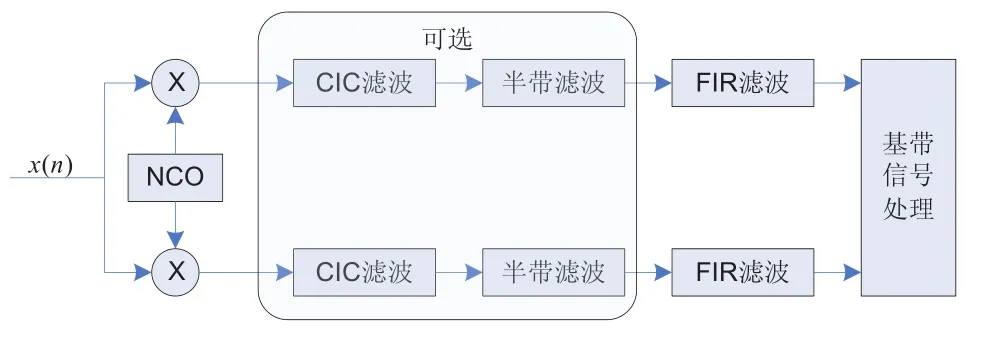

CORDIC算法数字瞬时测频实现的功能框图如图1所示,该模块包括一下几个主要组成部分:射频前端、ADC采样、数字下变频、CORDIC算法相位测量、相位推算法频率测量以及脉冲描述字产生等几个组成部分。

图1 CORDIC算法数字瞬时测频系统功能框图

射频前端完成天线侦察信号的低噪声放大、滤波、变频以及信道化等功能,将信号变换到ADC采样合适的频率、带宽和幅度。数模变换ADC部分完成模拟信号的数字化,考虑到窄脉宽的测量条件以及测频的瞬时性、精确性,该ADC的采样率要求比较高,如可以采用TI公司的14位210MHz的ADS5547,对于P波段信号可以进行直接射频采样,其它频段的信号可以通过变频到一个合适的中频再进行采样。

数字瞬时测频算法等功能都在FPGA中实现,包括数字下变频采用FPGA实现的优点是其流水线技术可以提高测频的瞬时性,同时易于高速并行实现以获得精度更高的脉冲到达时间、脉冲宽度等参数的测量。

1.1 数字下变频设计

数字下变频器(DDC)[2]的基本功能是实现信号从数字中颇/射频搬移到基带,即从输入的宽带高速数据流的数字信号中提取所需的窄带信号,并滤除带外噪声,获得低速数据流的基带信号。数字下变频器使得模拟下变频存在的混频器的非线性、本振的频率稳定度、边带和相位噪声等问题得到解决。DDC的基本结构包括:数控振荡器NCO、数字混频器(数字乘法器)、级联积分梳妆滤波器(CIC)/半带滤波器(采样率变换)和低通滤波器,在带宽相对较宽的情况下没有CIC滤波器部分,DDC的基本功能原理框图如图2所示。

图2 数字下变频功能框图

本设计中DDC采用数字混频、半带滤波加FIR滤波实现。数字混频采用基于CORDIC算法的数字本振NCO设计,该方法特别适合FPGA实现,优点是流水线高速实现,不需要占用FPGA片内ROM,且性能良好。

半带滤波器适用于抽取率为2n情况,计算效率高,实时性强,HB滤波器的定义为:

半带滤波器特性有:1)滤波器偶数序列号(不包括0)冲击响应为0;2)HB滤波器频输出抽取1/2后过渡带有混叠,通带无混叠;3)HB滤波器要求通带和阻带纹波相等。根据上述特点,以及滤波器系数对称性,设计的HB滤波器需要的乘法器的数目是普通FIR滤波器的1/4,设计结构采用常用的横向滤波器结构,适合FPGA中高速实现,一般作为DDC的前级滤波器。本设计中半带滤波器的输出采样率相对比较高,同时输出为数字检波信号(去载波信号),因此适合于作为脉冲包络参数的测量(脉冲到达时间、脉宽等),该测得的参数同时也是数字测频的同步信号。

DDC中FIR滤波器主要目的是对整个信道进行整形滤波,由于FIR滤波器位于CIC或HB滤波器之后,数据率相对较低,因此阶数可以设计的比较高,可以获得较好的性能(通带纹波,阻带衰减以及过渡带带宽等)。DDC输出的高信噪比、高镜像抑制度I/Q复信号可以作为后续相位测量以及频率测量的输入信号。

1.2 CORDIC算法相位测量的设计

相位推算法测频的基础是I/Q基带信号的数字鉴相,传统数字鉴相的方法是基于ROM查找表法,该方法缺点是当精度要求较高时ROM表非常大,本设计中采用坐标旋转接收机(CORDIC)算法来实现数字鉴相。

CORDIC算法最早是由J.Voider于1959年提出,包括旋转和向量两种模式,可进行向量旋转、求三角函数、反三角函数和求向量的模等运算,1971年J.Walther提出了统一的改进型CORDIC算法可工作在6种不同的模式,其中CORDIC算法相位测量的基本原理如式2所示:

其中(xi,yi)为输入矢量,(xi+1,yi+1)为输出矢量di,αi是每次旋转的角度,di是每次迭代旋转的方向,旋转的目标是使z趋近于0。CORDIC算法通过n次微旋转αi来获得φ相位值,由zi+1=zi-di·αi,则当n→ ∞,|yn|→ 0,z∞→φ=arctan(y1/x1)从而完成输入向量(x,y)的相位提取。

由于CORDIC算法可采用流水线型蝶形旋转结构实现[3],特别适合FPGA技术的实现,同时每级流水线只包括加减法、移位寄存器和tan-1(2-i)系数存储器,适用FPGA实现时占用的逻辑单元以及存储器资源比较少,如果输入的I/Q信号位数足够高,同时CORDIC算法流水线技术合适,可以获得高精度的相位输出。

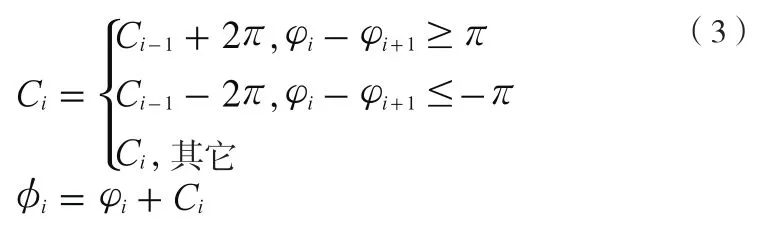

CORDIC算法获得的相位值在[-π,π]之间,对于单频信号随着样本点的增加,信号的实际相位会不停跨越周期,因此在频率计算之前需要对相位进行解模糊,相位解模糊的公式如式(3)所示:

1.3 相位推算法数字瞬时测频设计

模拟信号的瞬时频率f(t)与瞬时相位φ(t)的关系为:

则在数字域瞬时频率和相位的关系为:

其中φi为CORDIC算法计算获得的第i个样本点的相位值,Ts为采样间隔。因此相位推算法频率测量的基本思路是首先获得输入信号的I/Q复信号,通过CORDIC算法获得瞬时相位值,然后计算相邻样本点的相位差,根据相位差以及采样间隔就可以获得信号的频率值。

由于相位推算法测频对噪声的影响比较敏感,因此通过多点平均可获得高精度的频率。

2 基于FPGA的实现结果

本设计中ADC选择TI公司的14位ADS5547,采样率设为200MHz,ADC中频为425MHz,信号带宽为48MHz,FPGA选择ALTEAR公司STRATXI-II系列的EP2SGX60EF1154I4芯片。算法设计中DDC采用一级18阶半带滤波器加一级31阶FIR滤波实现,滤波器内部乘法器输入位宽为18比特,CORDIC算法输入I/Q信号位宽为18比特,并采用23级流水线实现CORDIC算法相位测量。

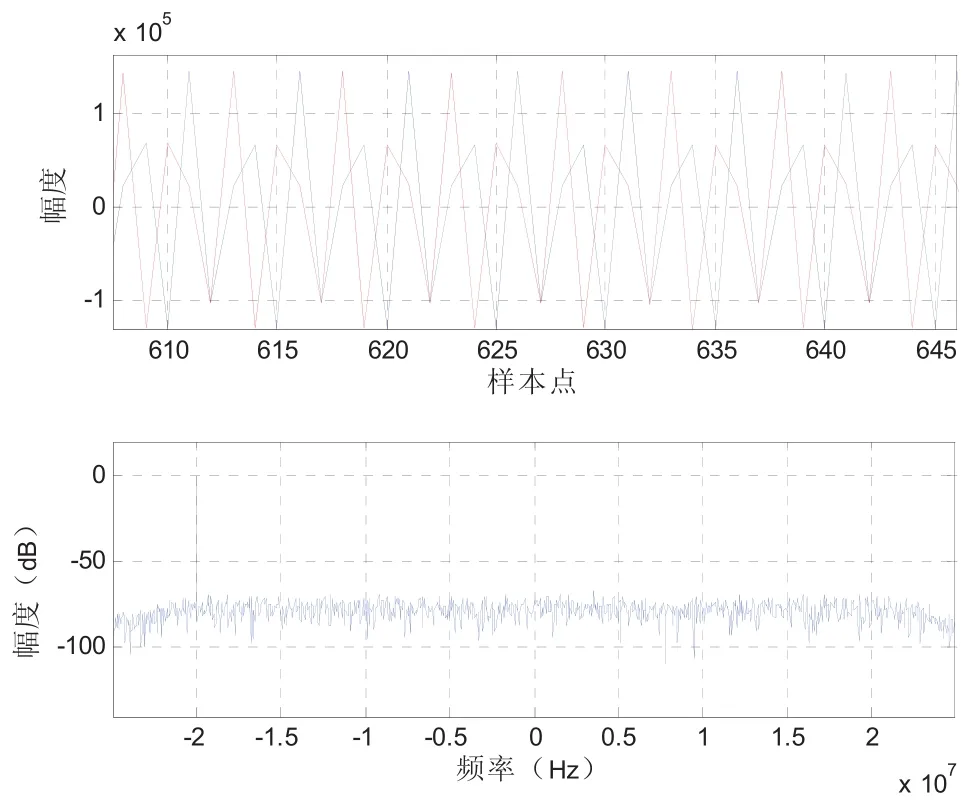

测试时输入频偏20MHz的单频脉冲信号,通过FPGA实现以及板级调试,将FPGA的各级输出结果通过SignaltapII调试工具导入到Matlab中进行分析,结果见图3和图4所示。通过实现可见瞬时测频精度基本在0.1MHz以内,如果通过多点平均,脉冲测频精度可达100Hz以内(图4中中间的粗线为误差均值线)。

图3 DDC输出信号时域和频谱图

图4 CORDIC算法测频误差图

3 结论

本文对对基于CORDIC算法瞬时测频的FPGA设计与实现进行了详细的论述,包括各关键子模块设计,并给出了FPGA实现的的结果,从结果看对单频信号该方法具有测频精度高、瞬时性好的优点,特别适合现代电子战接收机数字瞬时测频的需求。同时该方法已成功应用于某雷达侦察接收机数字瞬时测频模块中,获得了较好的测频瞬时性和测频精度。

[1]胡来招著.瞬时测频[M].国防工业出版社,2002:189.

[2]伍小保,章仁飞,王冰.数字阵列雷达数字下变频器ASIC 芯片设计[J].雷达科学与技术,2008:496-500.

[3]Andraka Ray. A survey of CORDIC Algorithms for FPGA Based Computers. In Proceedings of the 1998 ACM/ SIGDA Sixth International Symposium on Field Programmable Gate Arrays, 1998:191-200。

TM935

A

1674-6708(2010)22-00199-02

伍小保,工程师,工作单位:中国电子科技集团公司第三十八研究所微波技术部,主要从事雷达接收机及中频信号处理相关工作 王冰,研究员,工作单位:中国电子科技集团公司第三十八研究所微波技术部,研究方向:雷达、电子战、通信接收系统,高速数 据采集与信号处理