一种采用斜波比较的精细步进延时系统

摘" 要: 为了实现高频信号在欠采样条件下的波形重构,步进延迟脉冲信号的产生成为顺序等效时间采样技术用于触发取样系统进行高频信号采样的关键。为此,对精细延时方法进行研究,采用斜波比较的方法设计了一种精细步进延时系统,该系统基于微波三极管的开关特性,结合恒流源、充放电电路、高速电压比较器以及可编程DAC产生可调步进延迟时间的触发序列。对该系统进行仿真分析以及实验测试。实验结果表明,电容放电的线性区域下降沿时间为10 ns,幅度为4~7 V,与DAC比较后输出延迟脉冲的步进范围为10 ns,单位步进延迟精度可达1 ps。该斜波比较精细步进延迟系统可应用于取样示波器、矢量网络分析仪等测试仪器中,实现通信、雷达等信号探测与分析,对于高频信号的获取与分析具有重要意义。

关键词: 高频信号; 波形重构; 等效时间采样; 高精度步进延迟; 斜波比较; 微波三极管

中图分类号: TN710⁃34; TN78" " " " " " " " " " " 文献标识码: A" " " " nbsp; " " " " " 文章编号: 1004⁃373X(2025)03⁃0155⁃06

Precision step delay system employing ramp comparison method

WEI Chenbo1, 2, ZHANG Minjuan1, 2, HU Yuanyuan1, 2, LIU Wenyan1, 2, WANG Xuyang1, 2

(1. School of Information and Communication Engineering, North University of China, Taiyuan 030051, China;

2. Research Institute of Frontier Interdisciplinary Sciences, North University of China, Taiyuan 030051, China)

Abstract: In the process of achieving waveform reconstruction of high⁃frequency signals under the condition of undersampling, the generation of step delay pulse signals becomes critical for the sequential equivalent time sampling technique used in triggering sampling systems for high⁃frequency signal acquisition. Therefore, this paper strives to study the method for precise delay. The ramp comparison method is used to design a precision step delay system. On the basis of the switching characteristics of microwave transistors, this system integrates constant current sources, charge⁃discharge circuits, high⁃speed voltage comparators and programmable DAC to generate trigger sequences with adjustable step delay times. The system underwent simulation analysis and experimental testing. The experimental results demonstrate that the linear region of capacitor discharge has a falling edge time of 10 ns and an amplitude of 4~7 V. After the comparison with DAC, the step range of the output delay pulse is 10 ns, with a unit step delay accuracy of 1 ps. The precision step delay system based on ramp comparison can be applied in instruments such as sampling oscilloscopes and vector network analyzers, which enables communication and radar signal detection and analysis. To sum up, the proposed system is of significant importance for acquiring and analyzing high⁃frequency signals.

Keywords: high⁃frequency signal; waveform reconstruction; equivalent time sampling; high⁃precision step delay; ramp comparison; microwave triode

0" 引" 言

信号测试与表征是现代移动通信、光纤通信等高速通信中的必备环节,其中,高带宽测量设备是确保通信系统性能和可靠性的关键技术之一。伴随着光电信号频率的逐渐提高,USB 4.0和雷电3/4在商业和工业通信中实现40 Gb/s的理论传输速度,PCIe 5.0单通道传输速率达到64 Gb/s,光接入网中的数据传输速率正在由100 Gb/s向400 Gb/s、800 Gb/s乃至1 Tb/s的方向发展。在信号频率逐步提高的过程中,瞬态特性也会愈发明显,边缘陡度处于各个数量级之间会存在着较大的差异,信号的完整性难以得到保障,其携带的数据会受到各种因素干扰,进而导致传输过程中信息缺失等问题[1]。

随着信号的传输速率及带宽向更快、更高趋势发展,故现有信号测量表征设备与技术亟待提高,仅依靠模数转换器(Analog to Digital Converter, ADC)对信号进行连续实时采集,采样速率、信号带宽指标均难以进一步提升,且性能提升成本非常高[2]。等效时间采样技术能以较低的采样率[3]对高频信号进行取样分析,该原理的核心技术就是在外部时钟的驱动下实现精细步进延迟触发,并在延迟序列边沿进行低速采集。精细延迟技术在探地雷达、穿墙雷达、取样示波器和时域反射仪(TDR)中的特殊触发和基于时间的测量中被广泛应用。如取样示波器采用顺序等效时间采样技术对被测信号进行采样[4],由于信号具有周期性,可根据这个特性在时域内通过采样将模拟信号的频率从高频变为低频,然后再由低速模/数转换器(ADC)对模拟信号进行相对实时采样,使其以较低的采样速率对高频信号进行采样,不仅有较高的带宽,还克服了对A/D转换器转换速率的限制[5],但也带来了如何实现高带宽的取样门电路及在取样门打开的情况下如何实现高精度步进延迟脉冲的问题[6]。

在等效时间采样技术中,能够采用斜波比较法、可编程延时法以及步进相移法获得步进延迟脉冲,斜波比较法借助高速比较器对快斜波与慢斜波的电压进行对比,从而达到比较器的翻转条件并产生延迟脉冲,然而,由于比较器本身并非理想运放,其开环增益有限并且存在线性响应区域,这导致产生的延迟脉冲并非完全位于电压变化的理想交叉点,而是出现在电压翻转的某一范围内;可编程延时法所需的延迟芯片造价高且数量有限[7],在实现大延迟量时,需将多个芯片串联起来,输出信号电平复杂[8];步进移相法产生步进延迟取样脉冲的关键技术在于DDS的相位调谐分辨率以及D触发器的工作带宽,电路系统比较复杂,整机系统拥有较大的固有噪声以及固有抖动,取样脉冲信号的延迟精度无法低于10 ps。为此,本文研究了一种有效的斜波式步进延迟系统,以电阻、电容、微波三极管等组成的分立式元件为基础,比较器由两个微波三极管组成的具有开关特性的差分放大器代替[9],加上恒流源和充放电电容电路共同构成能够产生步进延迟的电路,实现步进延迟量为1 ps。

1" 精细延迟触发电路工作原理

1.1" 顺序等效采样原理

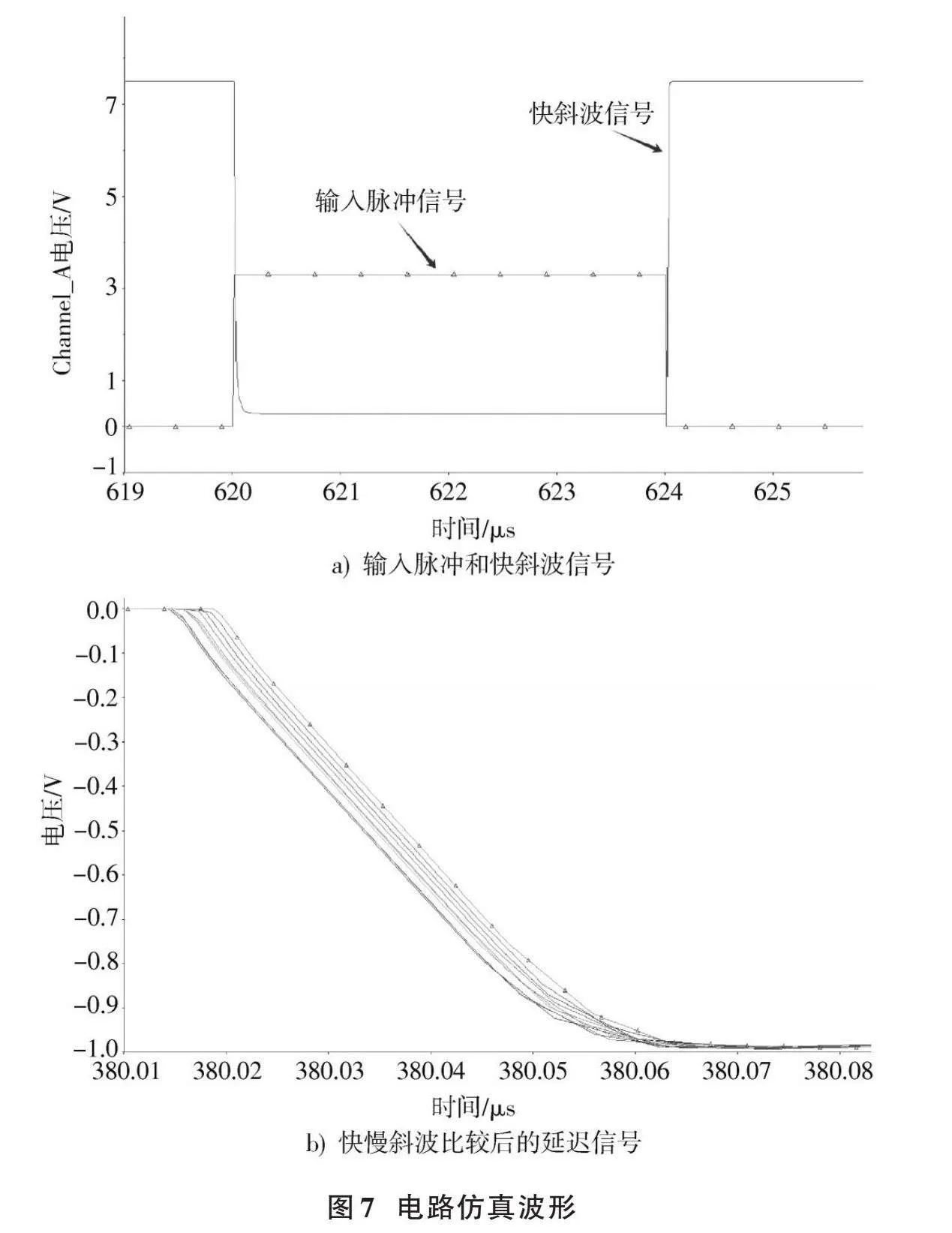

顺序等效采样是以时间为顺序依次进行采样,具有重构算法更加简化、信号重构更加准确、系统响应时间更短的特点[10]。顺序等效采样示意图如图1所示,图中的外部时钟信号作为触发信号与被测信号同步,且周期为被测信号的整数倍,以系统启动后到来的第一个触发信号为起始点进行采样,得到该采样点处的幅值信息,在随后的每一个触发信号到来时,每次采样的时刻相比上一次采样时刻都有一段相同的延迟增量,以此类推,一旦收集了足够的采样点以覆盖信号的整个周期,通过上位机就可重构出被测信号的波形[11]。上位机可以通过设定时基刻度和采样点数来控制每一次触发后的延时增量,每一次触发之后,延时增量越小,则在一个周期中被测量的信号收集的点数就越多,收集的波形承载的信息也就越精确[12]。

1.2" 斜波比较步进延迟原理

快慢斜波比较产生步进延迟脉冲原理如图2所示。外部时钟信号作为触发脉冲,快斜波电路由触发脉冲进行驱动,并产生与触发脉冲相同频率的快斜波信号[13]。慢斜波信号由FPGA配置DAC产生固定线性增量的阶梯电压。在等效采样方法中,步进延迟脉冲的产生依赖于高速比较器对快斜波信号和慢斜波信号的比较。当快斜波信号的下降沿达到慢斜波信号的幅度时,高速比较器将反转并输出步进延迟脉冲信号。这个延迟脉冲信号从首个触发脉冲到来时开始形成,并且在整个步进延迟时间窗内逐渐升高。随着慢斜波信号幅度的递减,与触发脉冲相比,输出的步进延迟脉冲信号延迟时间增加。

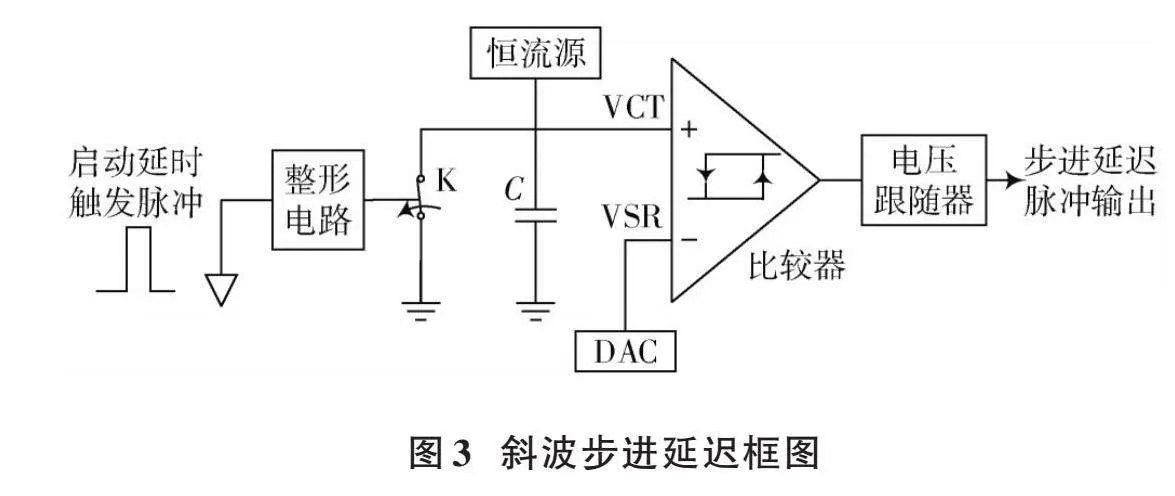

精细步进延迟系统的设计采用了斜波比较延迟原理,其构成框图及原理图如图3和图4所示。斜波步进延迟框图由等效开关K、恒流源、充电电容、高速比较器以及数/模转换器(DAC)组成。斜波步进延迟工作过程为:启动延时触发脉冲作为输入信号,经过整形电路触发开关K,当触发脉冲处于低电平时,K断开,恒流源开始给[C]进行充电;当触发脉冲为高电平时,K闭合,[C]对地放电。在放电过程中,电容上的电压呈线性减少,比较器比较VCT(快斜波电压)与DAC输出的VSR(慢斜波电压),当VCT的电压达到VSR时,比较器发生翻转并输出步进延迟脉冲信号,相对于启动延时的触发脉冲信号而言,比较器输出的延迟脉冲信号具有一定的相位差。通过改变电压跟随器的参数,可以调节延迟脉冲的幅值大小。

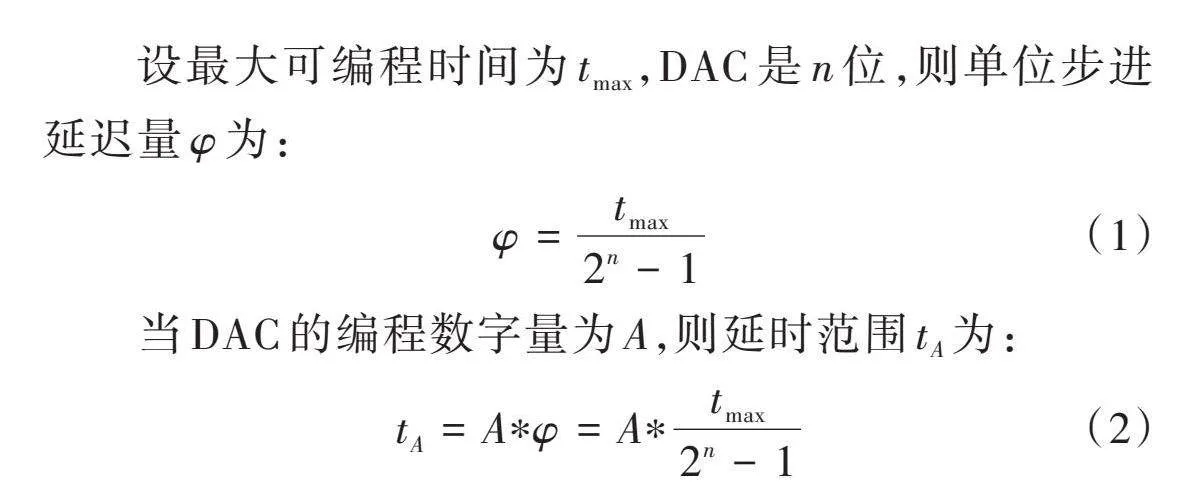

设最大可编程时间为[tmax],DAC是[n]位,则单位步进延迟量[φ]为:

[φ=tmax2n-1] (1)

当DAC的编程数字量为[A],则延时范围[tA]为:

[tA=A∗φ=A∗tmax2n-1] (2)

DAC可编程电压范围为[Vmin~Vmax],步进延迟最大时间[tmax]由[Vmax]决定,[Vmin]确定步进延迟的起始点。电容的充放电斜率与[Δt]成反比,VSR电压越高,步进延迟量越大,实际样本数量越多。

2" 精细步进延迟系统设计

2.1" 电容放电线性区及步进延迟量分析

在充放电电路中,由于电容放电过程是非线性的,特别是在电荷快要放空时,放电过程会逐渐变得非线性。这种非线性特性会导致DAC输出的步进延迟量在不同数字量区域变化不均匀。因此,需要确定电容放电的近似线性区域,并确保在该区域内,DAC单位数字量变化引起的步进延迟量变化是均匀的。

设恒流源对电容充电的满电电压为[V1],则放电过程中电容电压[Ut]随时间的变化规律为:

[Ut=V1*e-tτ] (3)

式中[τ]为时间常量。

将[Ut]在某点[t0]处展开为泰勒级数,得:

[Ut=Ut0+Ut0t-t0+12!Ut0t-t02+…] (4)

由式(4)可知,[Ut]的变化趋势主要由第一项直流分量和第二项一阶导数分量决定。而一阶导数项表示[t0]处的斜率,故可用切线法确定线性区域[14]。设在线性域的两端电压为[Va]和[Vb],对应的时间点为[ta]和[tb],[ΔV=Va-Vb],[Δt=tb-ta],DAC的数字量为[A],位数为[n],可以得出:

[ΔVΔA=Vmax2n-1] (5)

由式(5)可推导出:

[ΔA=2n-1∗ΔVVmax] (6)

式中:[Vmax]为DAC的满量程输出电压值;[ΔA]为对应[ΔV]下的数字量。因此,单位步进延迟量为:

[φ=ΔtΔA] (7)

2.2" 电路设计

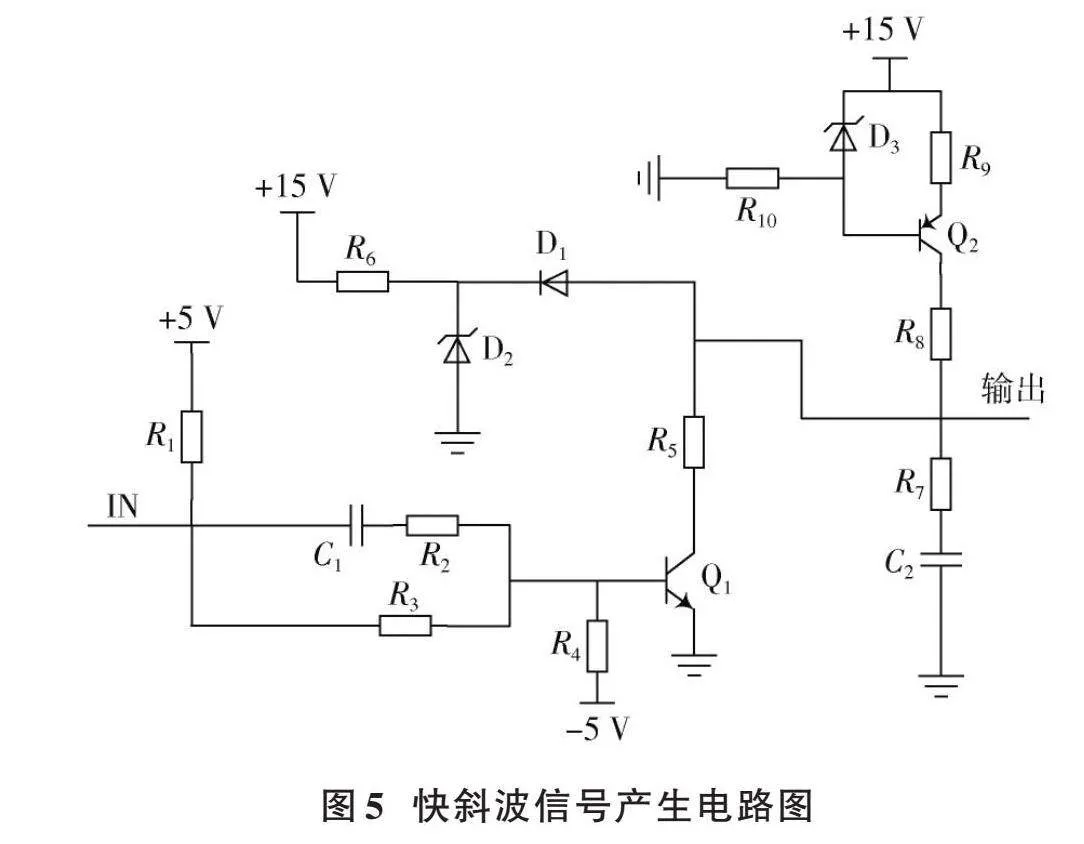

电路结构根据对斜波步进延迟原理以及电容放电线性区的分析进行设计,所设计的电路由微波三极管作等效开关[15]、恒流源、充电电容、DAC以及差分比较器共同构成。将所设计的电路分为两部分进行分析:一部分为快斜波信号产生电路图;另一部分为DAC和比较器电路图。

快斜波信号产生电路图如图5所示,输入信号为50 kHz的脉冲信号,[C1]、[R2]、[R3]和[R4]组成的电路结构有助于改进开关Q1的输入信号使其达到饱和效果。当输入脉冲处于低电平时,电阻[R4]下拉[T1]基极上的电平,可以加速三极管的关断,根据此方法,快速斜波产生的速度更快;[C1]与[R2]进行串联,有助于减少快速斜波启动脉冲过冲和振铃。开关Q1的选择需要根据电路参数让其工作在饱和区,低阻值[R5]、[R7]跟输入电路[R2]一样用来限定快速斜波电压启动阶段的振铃。恒流源电路由Q2、[D3]、[R8]、[R9]和[R10]构成,选用击穿电压为3.6 V的稳压二极管,可以保证整个电路的热稳定性,因为该稳压二极管的温度系数与Q2的PN结非常相近,[R8]可以减小Q2结电容对充放电电容[C2]的影响。D1、D2、[R6]构成的电路可以限制[C2]充电的最高电压,过高的VCT电压可能会导致三极管Q2、比较器和输出电路中Q3、Q6的B⁃E结击穿,需要很长的时间才能恢复到稳定状态。

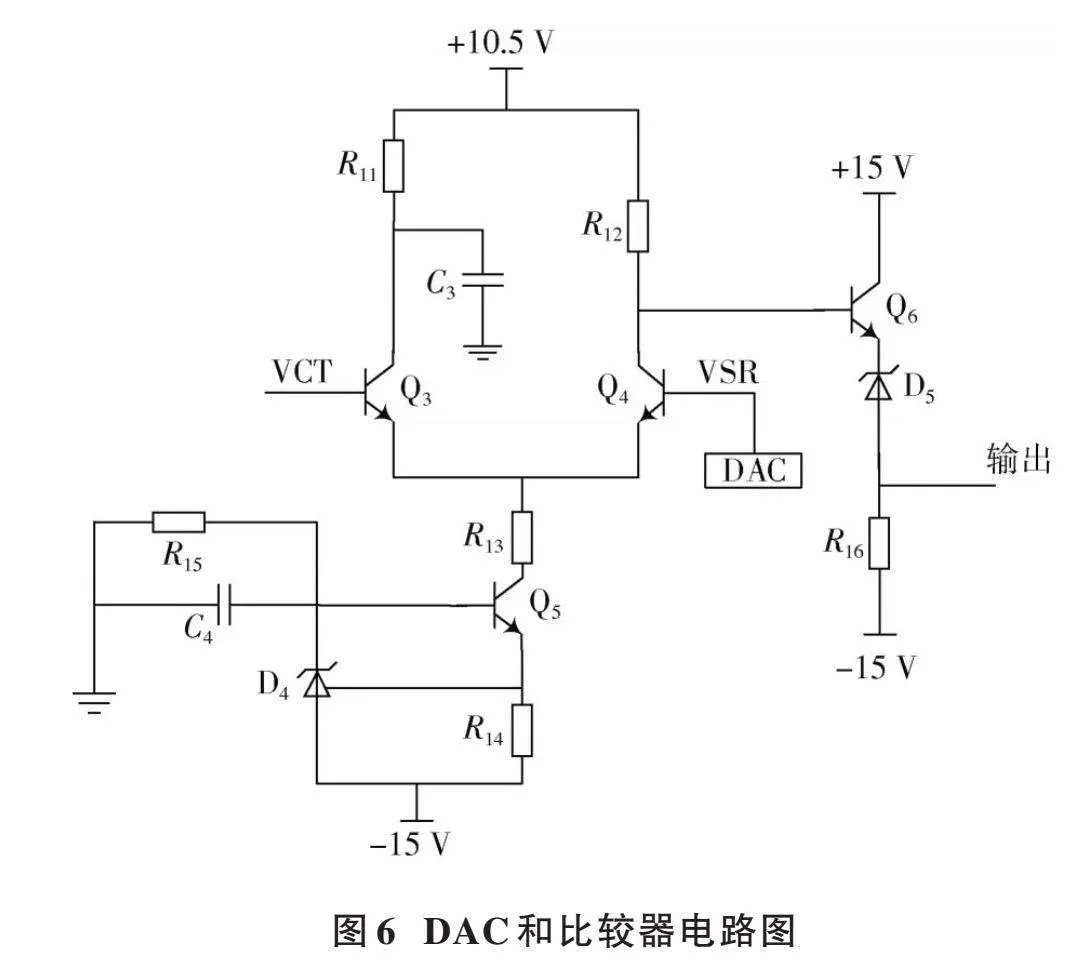

DAC和比较器电路图如图6所示。在Q3、Q4中比较了快斜波(VCT)和慢斜波(VSR)的电压,三极管发射极由Q5、D4、[R14]等器件组成的电流源电路偏置,通过偏置电流源,可以使输出信号的工作点固定在某一特定值附近,避免工作点漂移,使输出信号更加稳定。此外,采用可控精密稳压源D4,可确保电路具有良好的热源稳定性。调节差分比较器的电源电压为+10.5 V来满足以Q6、D5构成的电压跟随器的输入阈值要求,通过调节Q6、D5的参数,可对步进延迟脉冲进行幅值调节。DAC部分由FPGA控制芯片AD5764生成慢斜波信号(VSR)。

3" 实验验证与数据分析

3.1" 电路仿真与分析

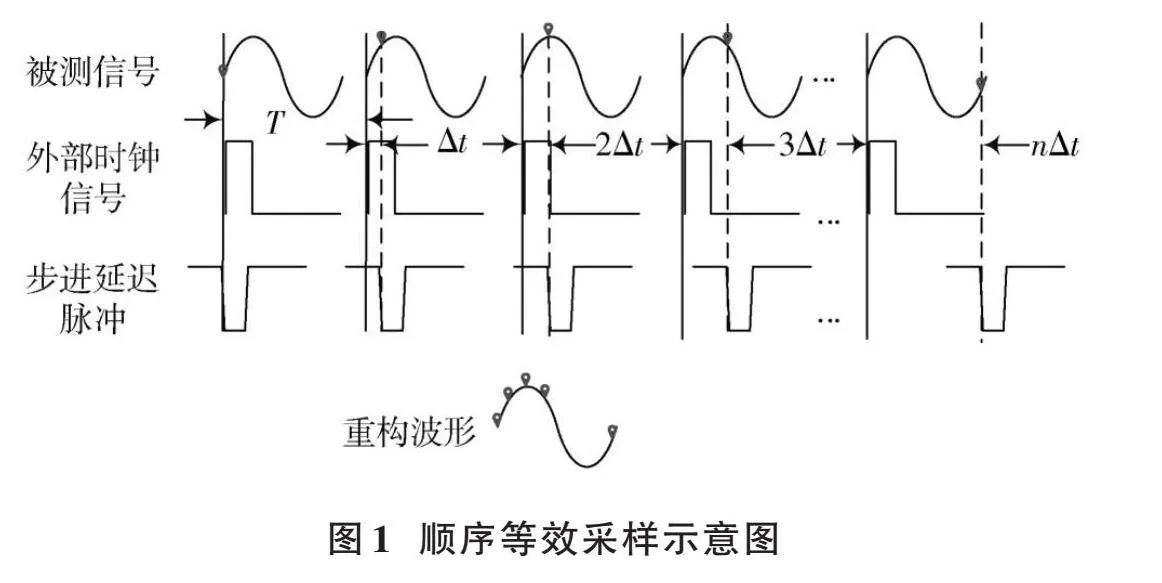

在仿真电路中,微波三极管Q1、Q3、Q4选择高性能MMBT4401,Q2选用BF812,电容[R7]的大小为1 pF,在仿真过程中,利用参数扫描法,设置4~7 V的模拟电压,采样点数为10代替DAC模块,电路仿真波形如图7所示。由仿真结果可以看出,当输入脉冲由低电平到高电平时,Q2开关闭合,电容经过放电产生下降的波形,从高电平到低电平时,Q2开关打开,恒流源对电容进行充电产生上升波形。当设置的模拟电压越大,与快斜波比较的电压值越高,比较后产生的步进延迟信号的延迟量就越大,所以通过改变DAC的电压值,可以对步进延迟脉冲信号的延迟范围和延迟时间做出改变。

图8为FPGA的在线逻辑分析仪模拟DAC产生慢斜波(VSR)的结果,采用的DAC位数为16,数字量为65 536,可模拟电压范围为-10~10 V,根据快斜波范围,设计的慢斜波的幅值范围为1~7 V,对应的数字量为36 044~52 428,FPGA通过检测所给时钟的上升沿进行计数,每次加1,当计数达到52 428时,重置为36 044,以此类推,就可得出锯齿形的慢斜波。

3.2" 实测验证

为了验证所设计电路的性能,对设计的步进延迟脉冲产生电路进行测试,搭建的硬件测试平台如图9所示。电路板为设计的斜波比较电路实物,采用两个模拟电源对电路板进行供电,通过信号发生器产生启动延时触发脉冲信号,使用采样率为20 Gsa/s、带宽为4 GHz的示波器(RT02044)对产生的延时信号进行测量。

斜波比较电路作为等效采样的关键,其步进延迟脉冲延时范围、边沿时间及幅值是重要的分析参数。使用信号发生器产生50 kHz、0~3.3 V、占空比为20%的正弦波作为输入脉冲,经过整形电路后电压可达三极管的关断电压如图10a)所示,在电容[C2]点测量的快斜波幅值为0~7.4 V、边沿27 ns,由于存在非线性区,根据电容放电区域的线性分析,线性区域幅值为4~7 V,边沿可达10 ns;图10b)显示DAC的输出引脚的慢斜波与仿真结果一致,周期为100 ms;图10c)表示步进延迟脉冲信号,以50 kHz的输入脉冲为同步参考,将其上升沿作为触发条件,在示波器余辉模式下,从示波器的时域上分析,最终步进延迟脉冲信号相对于初始相位依次位移10 ns,即动态延迟范围为10 ns,输出幅值为-1~0 V。

采用的DAC芯片为16 bit,根据快斜波的线性区域范围4~7 V,可得[ΔV]=3 V,[Δt]=10 ns,代入式(5)得[ΔA]=9 830,故由式(7)可计算出所设计电路的单位步进延迟量[φ]≈1 ps。

4" 结" 论

精密延迟触发电路为了实现宽动态范围和高分辨率取样脉冲延迟,引入了快斜波和慢斜波比较的方法。快斜波和慢斜波分别由微波三极管关断控制电容充放电和DAC产生,经过由差分放大电路作比较器输出步进延迟脉冲。

测量结果表明,步进延迟脉冲的动态延迟范围和单位步进延迟量可以达到10 ns和1 ps。若想改变延时范围,需要调整充电电容的电容值或者改变DAC的编程幅值。本次设计的精密步进延时触发电路可应用于取样示波器电路,实现宽带射频信号的采样。

注:本文通讯作者为卫晨博。

参考文献

[1] 王超.10 GHz宽带信号时域获取技术的研究与实现[D].成都:电子科技大学,2019.

[2] 蒋俊.基于信息熵的实时信号测量技术及其应用研究[D].成都:电子科技大学,2017.

[3] LI H T, LI B K, LÜ Z J, et al. Research on a step delay method in sequential equivalent time sampling (ETS) [J]. Review of scientific instruments, 2022, 93(11): 114708.

[4] 邱渡裕.宽带等效取样示波器关键技术研究[D].成都:电子科技大学,2015.

[5] YANG K J, WEI W T, SHI J L, et al. A fast TIADC calibration method for 5GSPS digital storage oscilloscope [J]. IEICE electronic express, 2018, 15(9): 20180161.

[6] TANKELIUN T, ZAYTSEV O, URBANAVICIUS V. Hybrid time⁃base device for coherent sampling oscilloscope [J]. Measurement science review, 2019, 19(3): 93⁃100.

[7] 余甜.皮秒级可编程精密延迟触发及同步采集技术研究[D].太原:中北大学,2023.

[8] CHEN Z Y, WANG X H, ZHOU Z W, et al. A simple field programmable gate array (FPGA) based high precision low⁃jitter delay generator [J]. Review of scientific instruments, 2021, 92(2): 024701.

[9] 孔令茹.微波液体探测装置中的回波信号等效采样技术研究[D].南京:东南大学,2019.

[10] 程亚昊.取样示波器同步触发延时系统设计[D].太原:中北大学,2022.

[11] 李子桐.取样示波器精密时基模块技术研究[D].太原:中北大学,2020.

[12] 姚鼎一,景宁,张敏娟,等.一种可调延时超窄脉冲触发序列产生技术[J].电子技术应用,2024,50(1):50⁃54.

[13] GU J, ZHAN H Q, YANG H Y, et al. Design of guided wave radar level meter based on equivalent time sampling [J]. IEEE computer society, 2013, 2: 139⁃142.

[14] 沈绍祥,冯炜,纪奕才,等.TDR波形传输时间的切线法判定与实现[J].科学技术与工程,2009,9(24):7537⁃7541.

[15] 程院莲,刘修泉.基于Multisim12的晶体三极管开关电路应用研究[J].电子制作,2016(7):13⁃15.