智能座舱域控制器FPD⁃Link Ⅲ检测系统设计

摘" 要: 随着汽车电子技术的进步,FPD⁃Link Ⅲ作为高速串行视频传输接口,正广泛应用于智能座舱系统。为对其进行检测,提出一套基于DS90UB948解串芯片的FPD⁃Link Ⅲ视频处理方案。系统采用ZYNQ作为处理核心,对解串芯片输出的并行信号进行图像压缩拼接和输出,输出的拼接视频流用于实时显示。采集的单路图像用于质量检测,通过图像相似度算法进行定量分析。实验结果表明:系统可正确接收、处理三路FPD⁃Link Ⅲ视频流,拼接图像连贯流畅,采集图像清晰;并且SSIM图像相似度算法可准确定位异常通路,满足了FPD⁃Link Ⅲ的质量验证要求,为构建高阶智能驾驶仿真测试平台的图像采集与传输提供了技术支持与保障。

关键词: FPD⁃Link Ⅲ; 智能座舱; 座舱域控制器; 视频压缩; 视频拼接; SSIM

中图分类号: TN919⁃34; TP274" " " " " " " " " "文献标识码: A" " " " " " " " " " " 文章编号: 1004⁃373X(2025)02⁃0021⁃08

Design of intelligent cockpit domain controller FPD⁃Link Ⅲ detection system

WU Bin1, ZHENG Yongjun1, WANG Xueying1, GUO Bin1, 2

(1. College of Metrology amp; Measurement Engineering, China Jiliang University, Hangzhou 310018, China;

2. Wolei Intelligent Technology Co., Ltd., Hangzhou 310018, China)

Abstract: With the progression of automotive electronic technology, FPD⁃Link Ⅲ, as a high⁃speed serial video transmission interface, is extensively employed in intelligent cockpit systems. In order to conduct its examination, a FPD⁃Link Ⅲ video processing solution based on the DS90UB948 unstring chip is proposed. In this system, ZYNQ is used as the processing unit to compress, splice, and output the parallel signals output by the unstring chip. The output splice video stream is used for real⁃time display. The collected single image is used for quality detection, and the image similarity algorithm is used for the quantitative analysis. The experimental results show that the system can receive and process three channels of FPD⁃Link Ⅲ video streams correctly, providing coherent and smooth spliced images along with clear captured images. The SSIM image similarity algorithm can accurately locate abnormal paths, meet the quality verification requirements of FPD⁃Link Ⅲ, and provide technical support and guarantee for image acquisition and transmission of the construction of high⁃level intelligent driving simulation test platform.

Keywords: FPD⁃Link Ⅲ; intelligent cockpit; cockpit domain controller; video compression; video stitching; SSIM

0" 引" 言

随着汽车电子技术的不断进步,汽车行业正迎来一场巨大的变革。汽车已经从简单的机械交通工具变成复杂的移动平台,现代汽车智能座舱中液晶显示器、车载娱乐系统及驾驶信息显示屏不断增多,为驾驶员和乘客提供了丰富的信息和娱乐方式[1⁃3],但也对视频传输带来了巨大的挑战。

传统的视频传输接口有USB、MIPI、Camera Link等。其中USB传输带宽低,难以满足高清视频传输需求;MIPI传输距离有限,对电磁干扰较为敏感;Camera Link虽提供了高带宽,但是抗干扰性差、成本较高,难以用于工业量产[4⁃5]。相比之下,FPD⁃Link接口集高带宽、抗干扰性以及成本效益于一身。发展到第三代的FPD⁃Link Ⅲ芯片组满足AEC⁃Q100汽车可靠性标准和ISO⁃10605电磁兼容性标准,为车载摄像系统、显示器面板等图像传输[6⁃8]提供了解决方案,其应用领域还扩展至医疗、航空工程的图像传输[9⁃10],得到了这些行业的高度认可。尽管FPD⁃Link Ⅲ在视频传输领域展现了巨大的潜力,但现有研究主要集中于视频传输、重构与显示[11]等方面,对于FPD⁃Link Ⅲ的检测仍处于空白阶段。在现有文献中,缺乏针对这方面的全面检测方案,工业上往往依赖人工进行视频流畅性和眼图完整性判断,但这种方式不仅效率低下,且缺乏统一的检验方法,容易受到主观判断影响,导致检测结果不稳定。因此,研究一种对汽车域控制器FPD⁃Link Ⅲ接口可靠性的高效测试方案势在必行。

本文就某公司的智能座舱域控制器,提出了一种基于ZYNQ 7000与DS90UB948的三路FPD⁃Link Ⅲ的检测系统。该系统通过HDMI进行三路视频拼接显示,并采用以太网进行视频图像采集,最后使用图像相似度比对来完成FPD⁃Link Ⅲ功能性测试。

1" FPD⁃Link介绍及系统整体设计

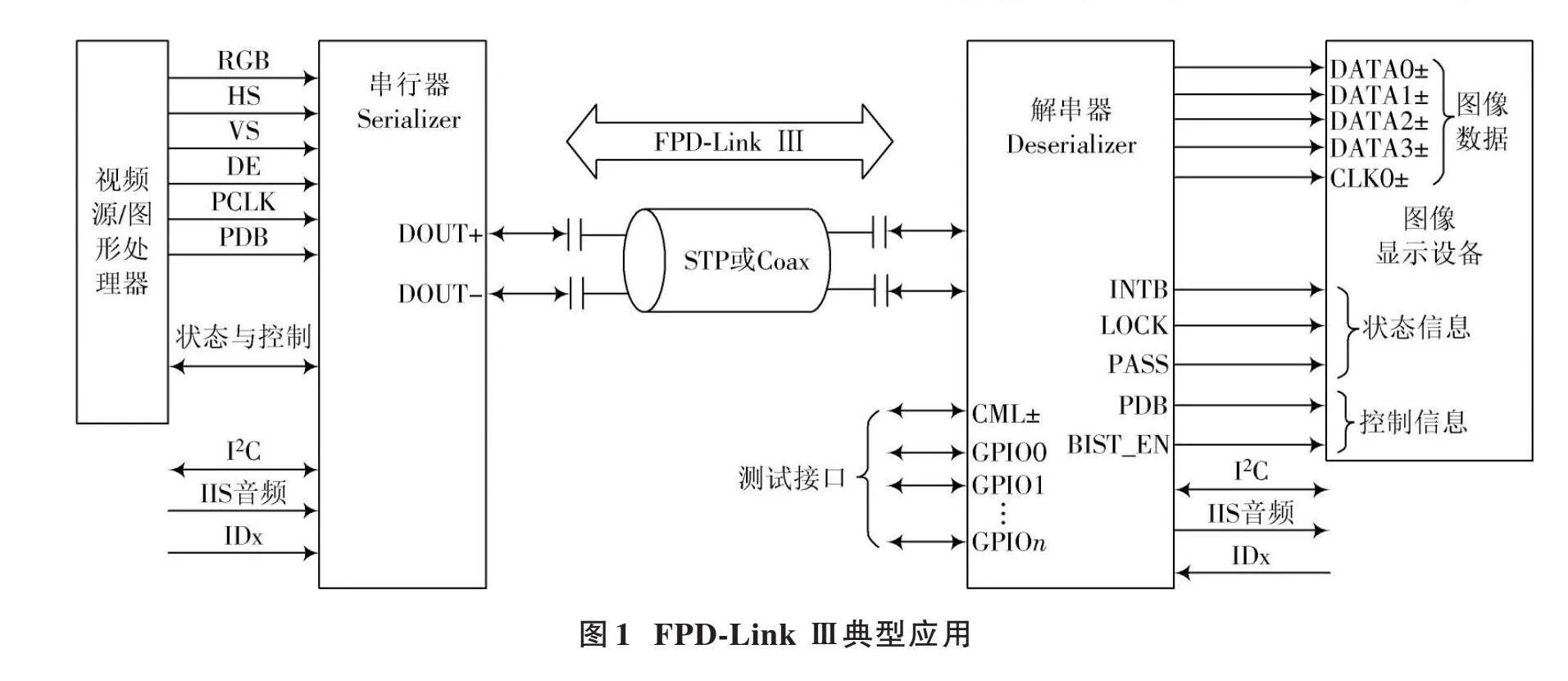

FPD⁃Link Ⅲ是由TI公司研发的一种点到点高速串行视频接口标准,可实现多通道无损视频传输。它通过双绞线或同轴线缆进行低压差分传输以抑制共模噪声,来获得更远的传输距离。根据FPD⁃Link Ⅲ传输协议,其线缆上主要传输电力和图像数据、时钟、状态与控制信息。FPD⁃Link通过时分复用技术完成线缆上的正反通道叠加,正向通道使用8b/10b编码进行高速视频数据和部分控制信息的传输,反向通道进行低速状态和控制信息传输。接收端IC集成解串器进行串/并转换、时序恢复等操作。图1为FPD⁃Link Ⅲ的典型应用。

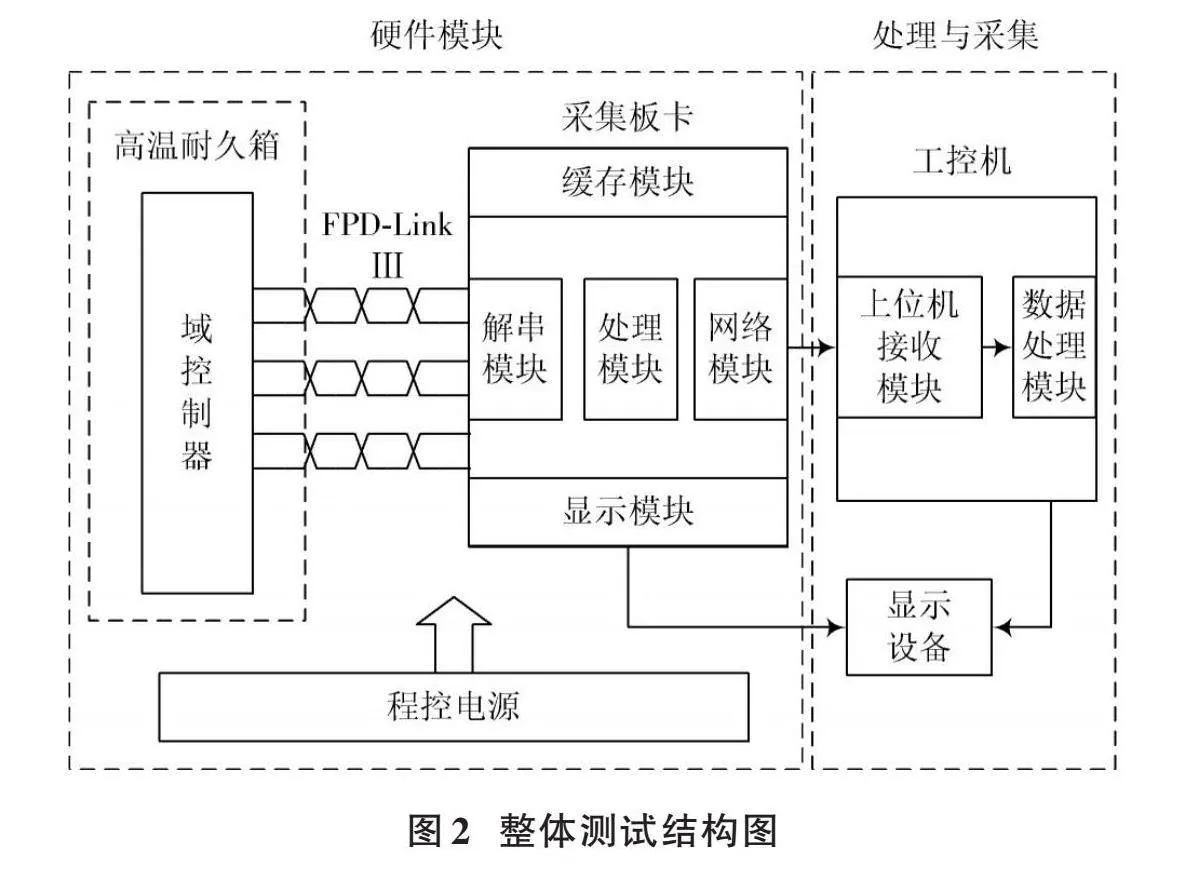

某公司提供的智能座舱域控制器有多种接口,涵盖了图像与显示、感知与检测、导航与通信等功能。其仪表屏、中控屏、下控屏均采用FPD⁃Link Ⅲ接口输出1 920×720、30 Hz的视频。为了高效检测这三路输出,所设计的整体测试结构如图2所示,将智能座舱域控制器置于高温箱模拟实车工作环境。板卡同时接收、处理三路FPD⁃Link Ⅲ视频,拼接视频流通过HDMI接口传输至显示器,以方便测试人员实时观测多路信号;板卡同时通过网络模块发送单路视频图像至上位机进行接收采集,接着通过数据处理模块完成对采集图像的自动检测和判断。

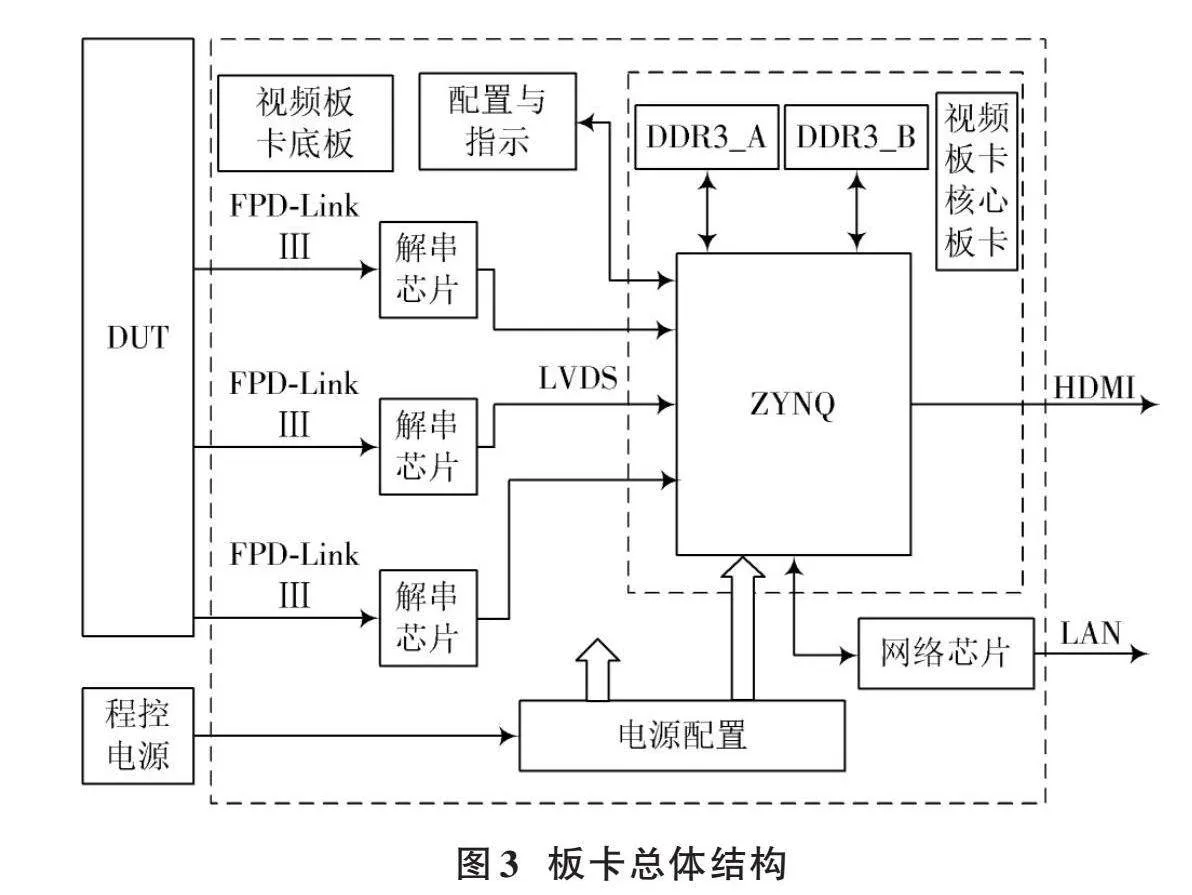

2" 系统硬件设计

为了对智能座舱域控制器FPD⁃Link Ⅲ信号进行解串、处理和输出,设计板卡的总体结构,见图3。为了模块化设计与标准化设计,板卡主要由视频板卡底板与搭载的核心处理板构成。智能座舱域控制器输出的三路FPD⁃Link Ⅲ信号经过3颗解串芯片,得到FPD⁃Link Open LDI格式的LVDS信号。ZYNQ对3组LVDS信号进行处理,并用双通道DDR3进行缓存,同时还负责外围设备的通信与配置。最后图像通过HDMI和LAN进行输出。

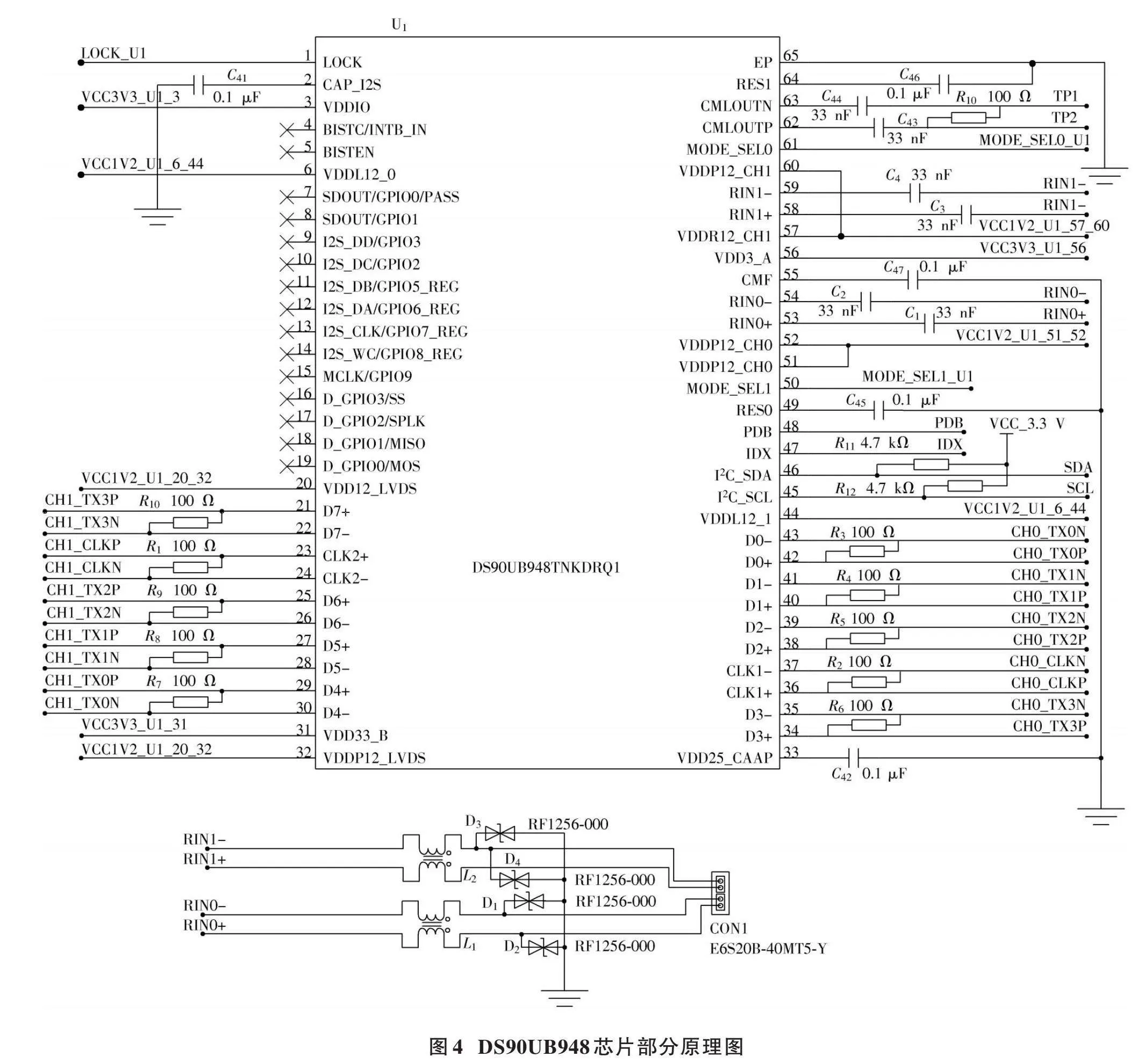

2.1" FPD⁃Link Ⅲ解码设计

作为TI公司开发的高速串行视频接口协议,解码模块采用专用的DS90UB948芯片完成FPD⁃Link Ⅲ至并行的FPD⁃Link Open LDI的LVDS接口转换设计,以确保最佳性能与兼容性。该芯片支持最高192 MHz像素时钟频率,并能实现2K分辨率的视频处理,自动时钟对齐和补偿功能简化了系统设计并提高了信号的稳定性。以芯片手册为指导并结合实际应用,设计的DS90UB948芯片部分原理图如图4所示。

在设计中,PDB引脚被设置为高电平以使能芯片。由于FPD⁃Link Ⅲ信号源与芯片间存在电位差,因此芯片输入端RIN0±和RIN1±需串联33 nF的AC耦合电容以提供直流隔离。采用分压电阻将MODE_SEL0设置在0.757 V,并将MODE_SEL1接地使芯片工作在STP输入、单路OLDI输出模式下。为区分3颗解串芯片,分别将IDx引脚电压设置成0 V、0.559 V、0.757 V,以设定初始I2C地址。为了增强信号的完整性并减少传输过程中的信号衰减,每对差分数据与时钟信号都通过100 Ω的终端匹配电阻以实现阻抗一致。最后通过引出LOCK信号显示内部时钟数据,恢复电路工作状态。

2.2" 其余模块与整体图

为适配机柜统一的DC 24 V电源,本文采用分级降压获取各芯片所需供电。第一级采用LMR33630芯片将24 V降至5 V,第二级采用TPS563201芯片将5 V降至3.3 V、1.8 V和1.2 V。分级降压设计不仅确保了转换效率,还有利于后期进行故障排查。网络传输模块采用RTL8211芯片,其支持千兆以太网通信和嵌入式自诊断。

RTL8211芯片采用25 MHz晶振为时钟参考,并通过RGMII接口连接ZYNQ,同时通过MDI差分对连接网络变压器。

在对外围的指示灯模块、JTAG、电平转换模块等进行设计布局之后,为了适配机柜的槽位尺寸,视频板卡整体设计如图5所示。

板卡左侧为三路FPD⁃Link Ⅲ接口,中间部分采用2个100 PIN与1个60 PIN基板连接器与核心处理板相连;右侧通过2个接插器接至外部电源,输出至外部的RJ 45网口与HDMI接口。板卡采用四层板设计,分区建立功率地和电源地铺铜区域,以降低不同地线间的电磁干扰。螺丝孔位与板卡EARTH网络相连以保持接地。

3" 系统软件设计

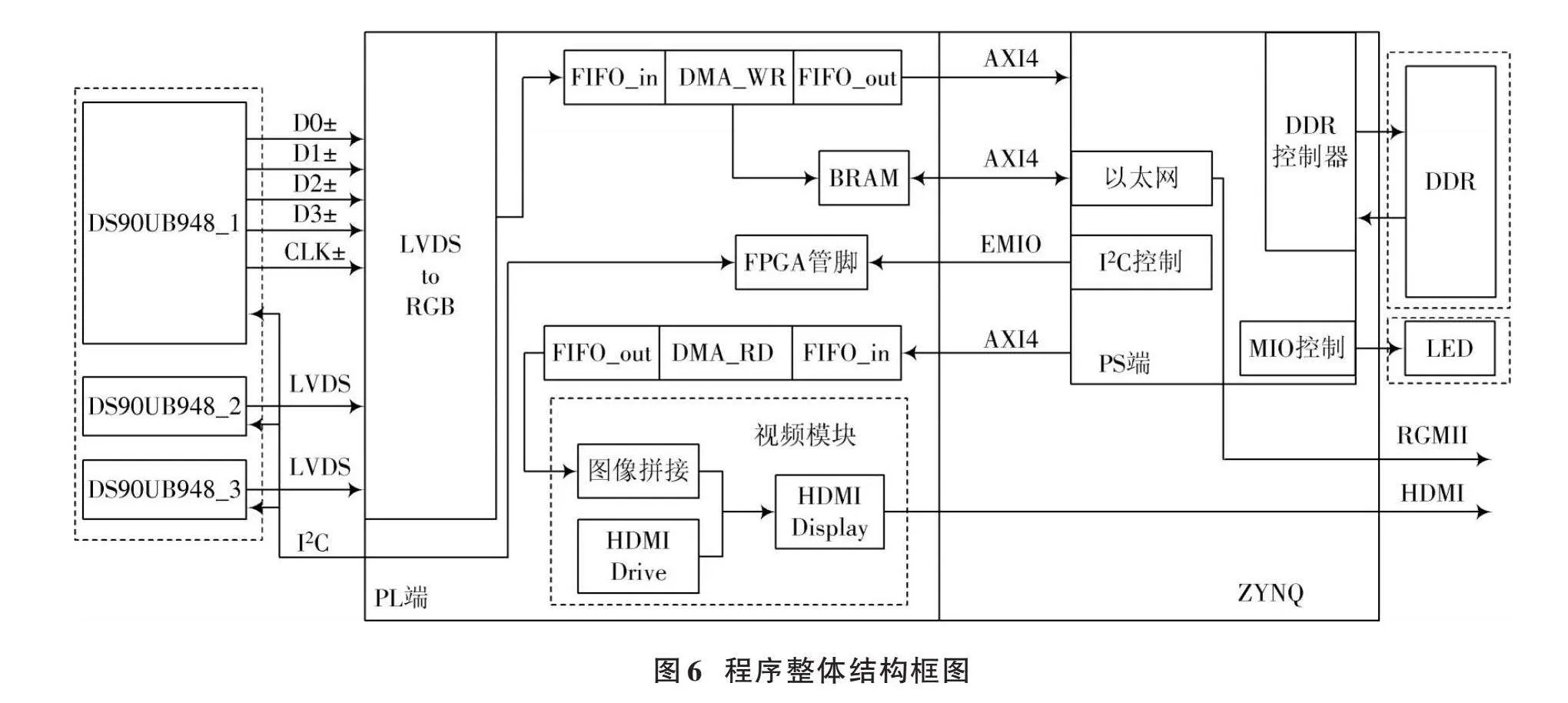

ZYNQ⁃7000系列融合了FPGA和ARM,内部分别有PL和PS模块,可发挥各部分优势来完成软件层面的设计。图6为本次程序结构框图,主要由LVDS to RGB、DMA_WR、DMA_RD、视频模块构成。输入的D0~D3差分数据与差分时钟LVDS信号通过LVDS to RGB模块得到像素数据及时钟、使能标志信号。数据通过由FIFO封装的DMA_WR和DMA_RD模块,经片内AXI4总线访问挂载在PS端的DDR3进行缓存。PL同时将单帧视频图像存入BRAM内。PS端使用AXI4协议同步读取位于BRAM内的视频图像数据,通过RGMⅡ协议发送至RTL8211FD,完成以太网的传输。PL端对DDR3缓存的数据进行处理拼接后,配合HDMI的时序驱动与显示程序,完成HDMI的图像输出。

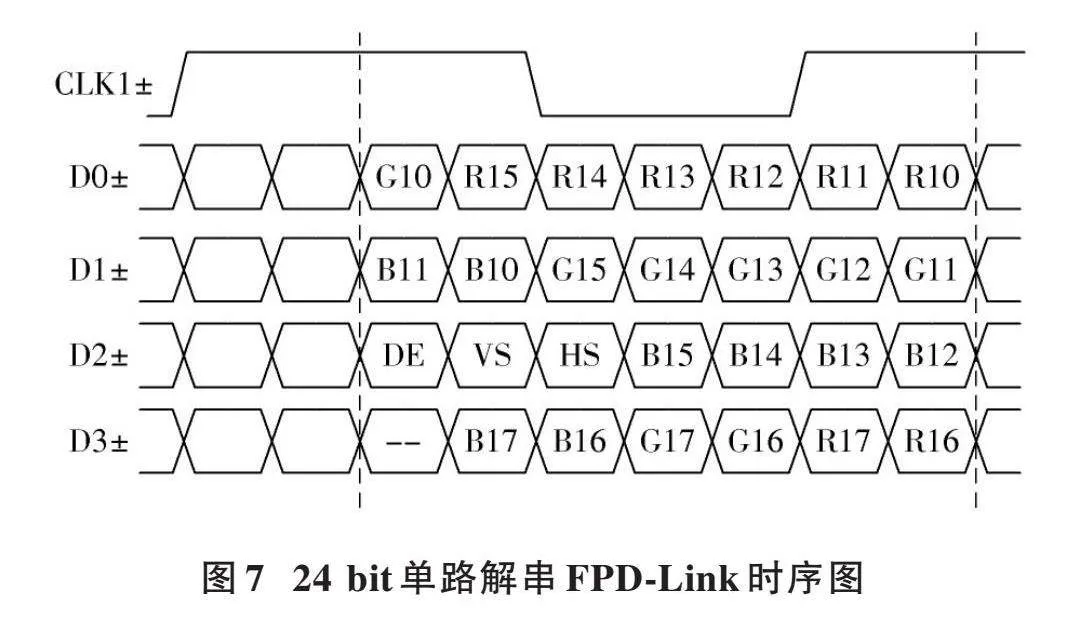

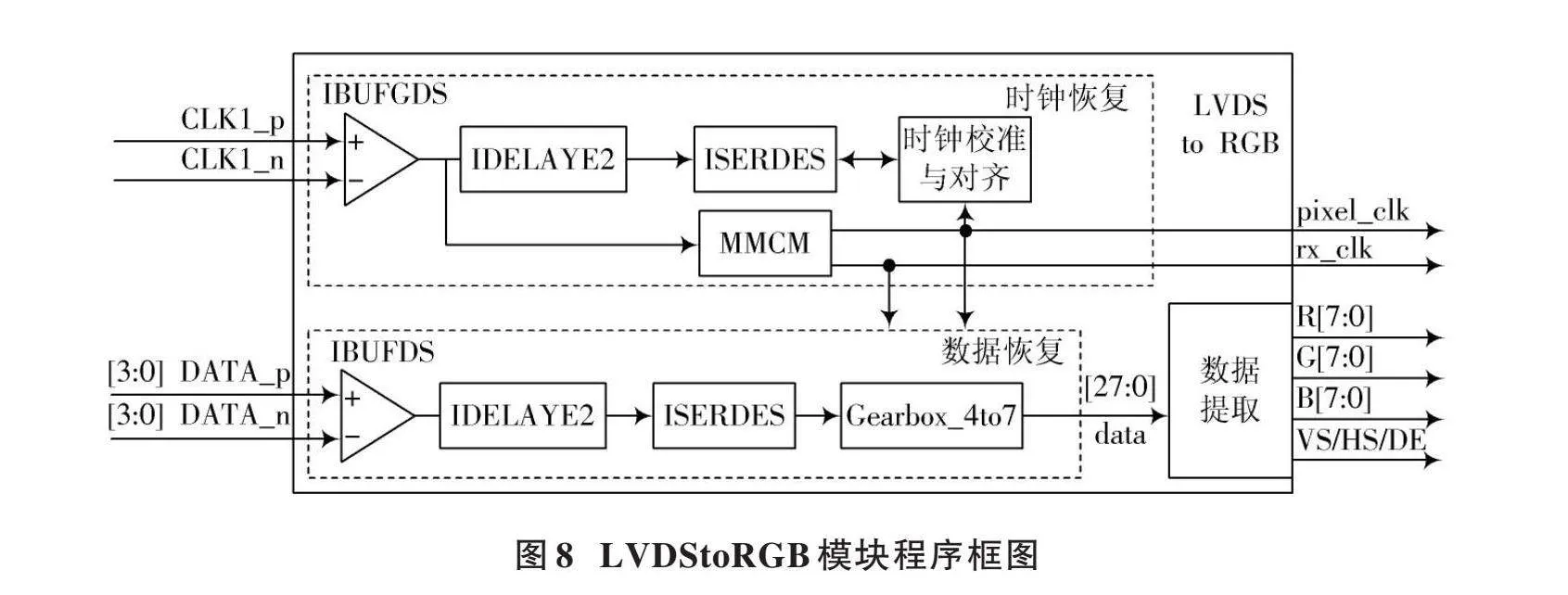

3.1" LVDS to RGB模块

在解串芯片配置条件下,FPD⁃Link Ⅲ的解串时序图如图7所示。输入ZYNQ的差分时钟遵循4∶3的占空比,每一帧包含了28像素时钟及RGB888像素数据与行场同步、使能信号。每一帧都从2个像素时钟的高电平开始,并包含之后的3个像素时钟低电平,以下一帧2个高电平结束。

LVDS to RGB模块设计在遵循赛灵思官方文档XAPP585的基础上,通过参数调整和时序优化以保证处理FPD⁃Link Ⅲ视频流的高稳定性和低延迟。该模块的程序框图如图8所示,使用IBUFGDS和IBUFDS模块作为输入缓冲器,将差分信号转换为单端信号。其中一路单端时钟数据用于MMCM,生成包括ISERDES采样时钟和像素时钟等时钟;剩余单端时钟和单端数据通过IDELAYE2模块完成时序校准后,通过ISERDESE2模块变成并行4位数据。受限于架构,ISERDESE2模块只能完成1∶2、1∶4的转换,而本设计需要4∶7的非标转换,所以需通过Gearbox模块完成4∶7的速率转换,最终恢复出4通道共28位的数据。按图7时序图对其进行提取组合即可得到RGB数据和行场同步、使能信号。

3.2" DMA读写模块

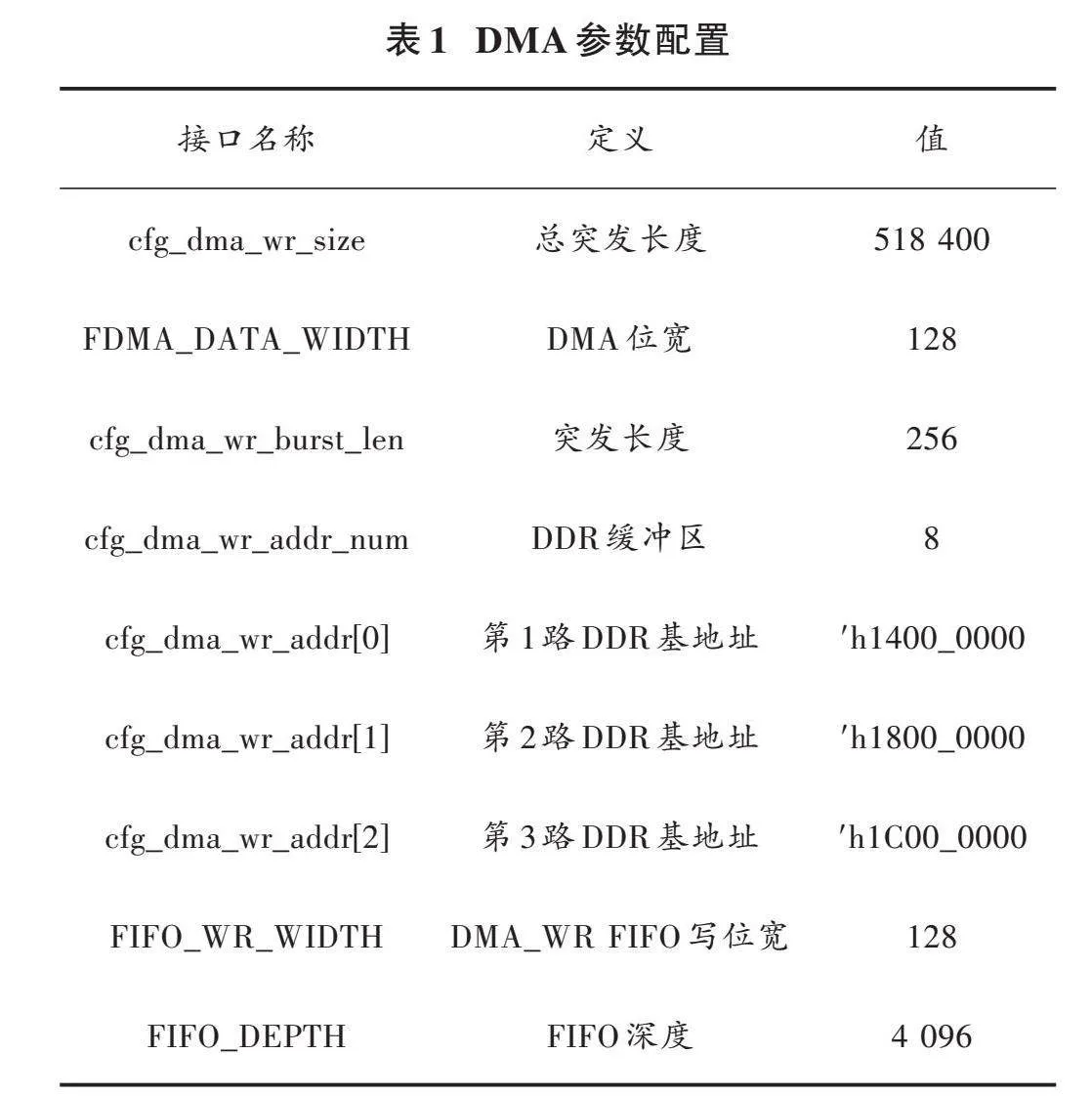

由于DDR3挂载在PS端,因此PL端需通过AXI4⁃DMA(Direct Memory Access)进行内存数据的访问[12],利用DMA高效、低延迟的传输能力,完成高带宽FPD⁃Link Ⅲ数据的实时读写。因为读写模块逻辑近乎镜像,主要介绍DMA_WR模块。该模块主要由DMA PS端配置、DMA读信号、DMA控制信号和DMA FIFO信号构成,通过异步FIFO完成跨时钟域的数据传输。来自LVDS to RGB的RGB888数据以pixel_clk为时钟参考存入FIFO,以PS端的ui_clk为参考进行数据读取。该模块使用异步FIFO配合DMA写状态机完成数据的突发写。为了传输一帧1 920×1 080的图像,每个像素数据为4 B,需传输8 294 400 B数据,以128位宽的DMA来传输,总突发长度为518 400。为了减少数据丢失风险,在DDR内设立8个缓冲区,每一个缓冲区存放一帧视频图像,因此DDR内每一路FPD⁃Link Ⅲ视频图像存储必须单独留出至少'h3F4_8000空间。在对DMA突发长度进行定义之后,DMA各参数配置如表1所示。

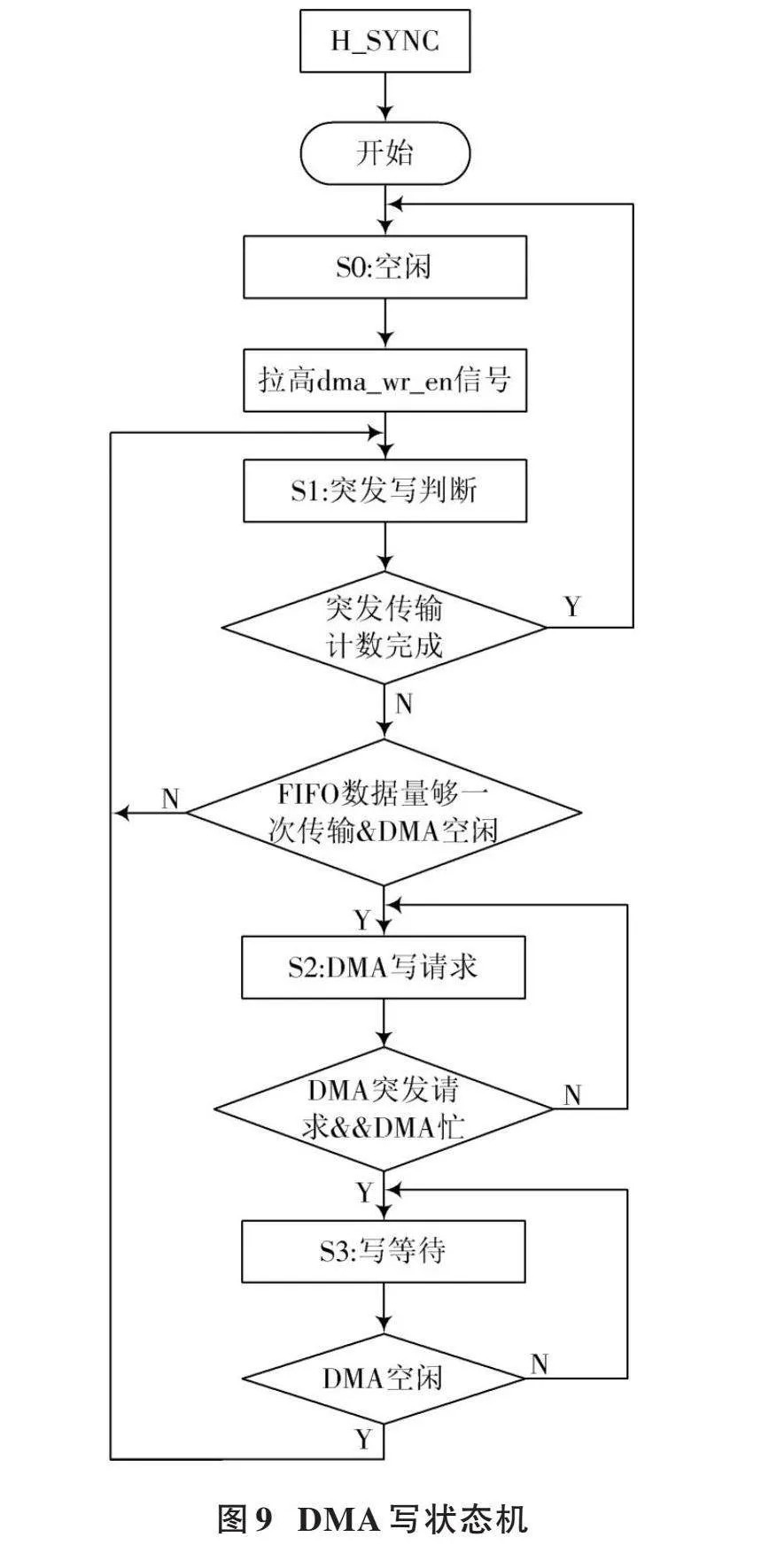

在异步FIFO完成对跨时钟域的数据缓存后,还需通过状态机将数据发送至端口。如图9所示,DMA写状态机抓取LVDS to RGB模块输出的行同步上升沿作为开始信号,经一段时间的等待完成FIFO的复位,待FIFO正常工作之后,拉高dma_wr_en信号,写状态机从空闲S0进入DMA突发写判断S1状态。首先使用突发次数计数器来判断是否为最后一次读写,以确定本次突发写数据个数,同时输出缓冲区计数器值以确定当次写地址;接着采用FIFO读数据计数器来判断是否够一次突发传输,若外部DMA同处于空闲状态,便可进行DMA突发写请求,并跳转至DMA写请求状态机S2。待外部DMA忙碌时,状态机跳转至S3写等待状态。当外部DMA写响应完成时,重新跳转至突发写判断S1状态,开始新一轮的写入。

3.3" 视频模块

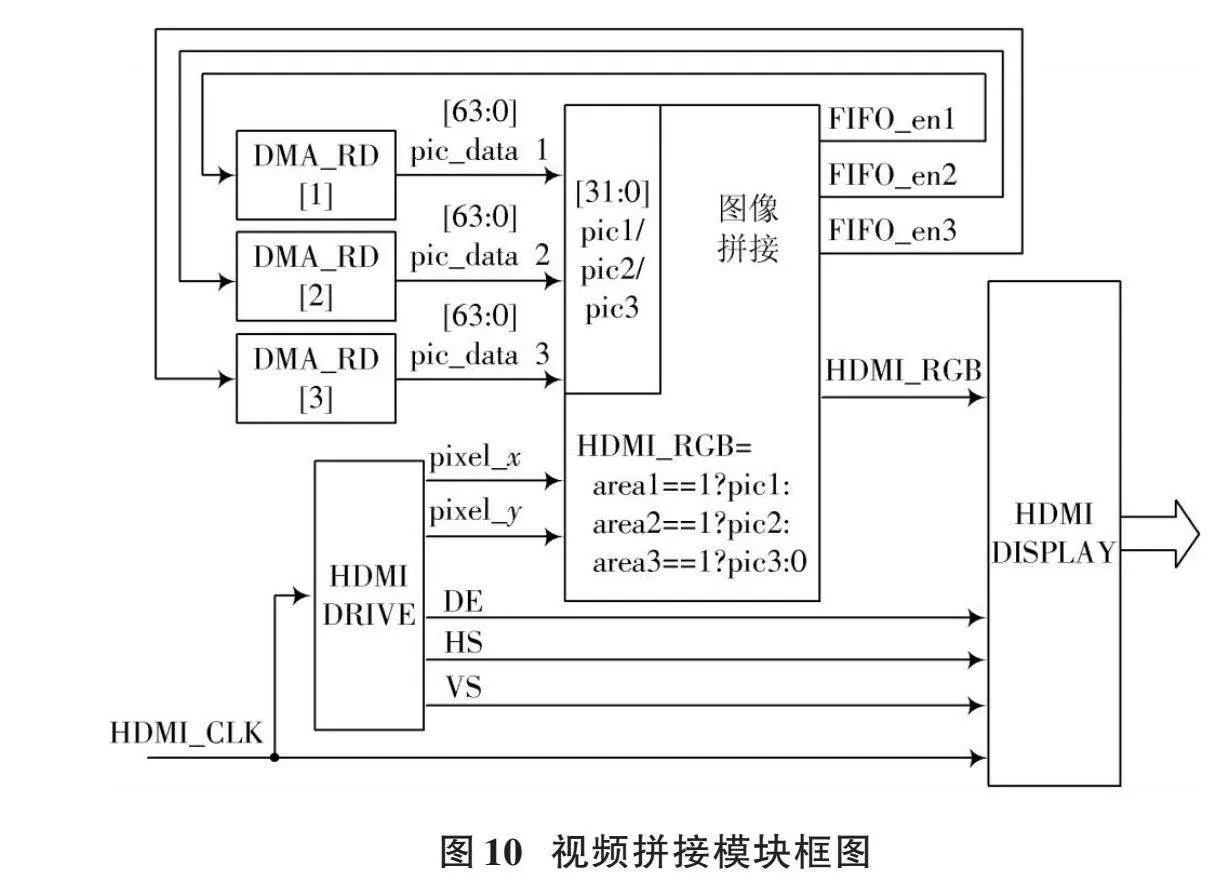

智能座舱域控制器单路FPD⁃Link Ⅲ为1 920×720、30 Hz视频输出。为将三路视频同时显示在1 920×1 080分辨率的显示器上,需进行视频的压缩和拼接。

在顶层模组配置中,DMA_RD模块异步FIFO读位宽为64,图像拼接模块像素数据位宽为32。由于位宽不匹配,DMA_RD模块每次读出的两个32位像素点数据,在传入图像拼接模块高位都会被舍弃。通过间隔一位丢弃一个像素,完成了单幅图像像素总数的对半压缩,宏观上即为1 920×1 080至1 920×540的画幅转变。视频拼接模块使用HDMIDRIVE模块生成的像素坐标信号pixel_x、pixel_y,将显示区域按田字格均匀划分成4个区域。视频拼接模块框图如图10所示,当像素坐标处于某区域时,将该路压缩完的像素数据赋值给HDMI_RGB;当像素坐标处于该区域之外时,该路像素数据被舍弃,HDMI_RGB由对应路像素数据替代。通过区域划分并选择输出,完成了1 920×540至960×540的画幅转变,使得1 080P显示器能同时显示三路FPD⁃Link Ⅲ视频流。

若三路DMA_RD中的FIFO只按LVDS to RGB模块的RGB像素锁定信号来读取,会因同时读取速度过快而出现像素错位、画面撕裂的问题,所以需定义使能信号分别控制各路FIFO读取使能。当像素行场坐标处于上半幅位置时,只有通道1、2的FIFO读取;当显示到下半幅图像时,通道3的FIFO才能进行读取。这样设计不仅确保了时序无误,还配合高效的间隔像素丢弃压缩策略,确保了图像的连续和完整。简洁的模块设计不仅提高了系统运行稳定性,还使其更易调试与优化。最终视频拼接模块输出的HDMI_RGB配合HDMI驱动与显示模块,完成压缩视频图像的输出。

4" 测试结果与分析

为了对软件关键模块的正确性进行评估,采用Testbench进行波形仿真,并通过ILA探针进行信号抓取验证,得到的波形如图11所示。

对于LVDS to RGB模块,Testbench模拟了解串芯片输出的89 MHz差分时钟与623 MHz数据信号输入。该模块能正确恢复出与原频率相同的rgb_clk。像素数据与使能信号经9个rgb_clk周期处理后同步输出。对于DMA_WR模块,当DMA空闲且FIFO内部数据个数超过一次突发传输个数,状态机进行跳转进入写模式,DMA进入忙碌状态。FIFO内部数据逐渐减少至一次突发传输完成后,DMA重回空闲状态并开始等待下一次传输。

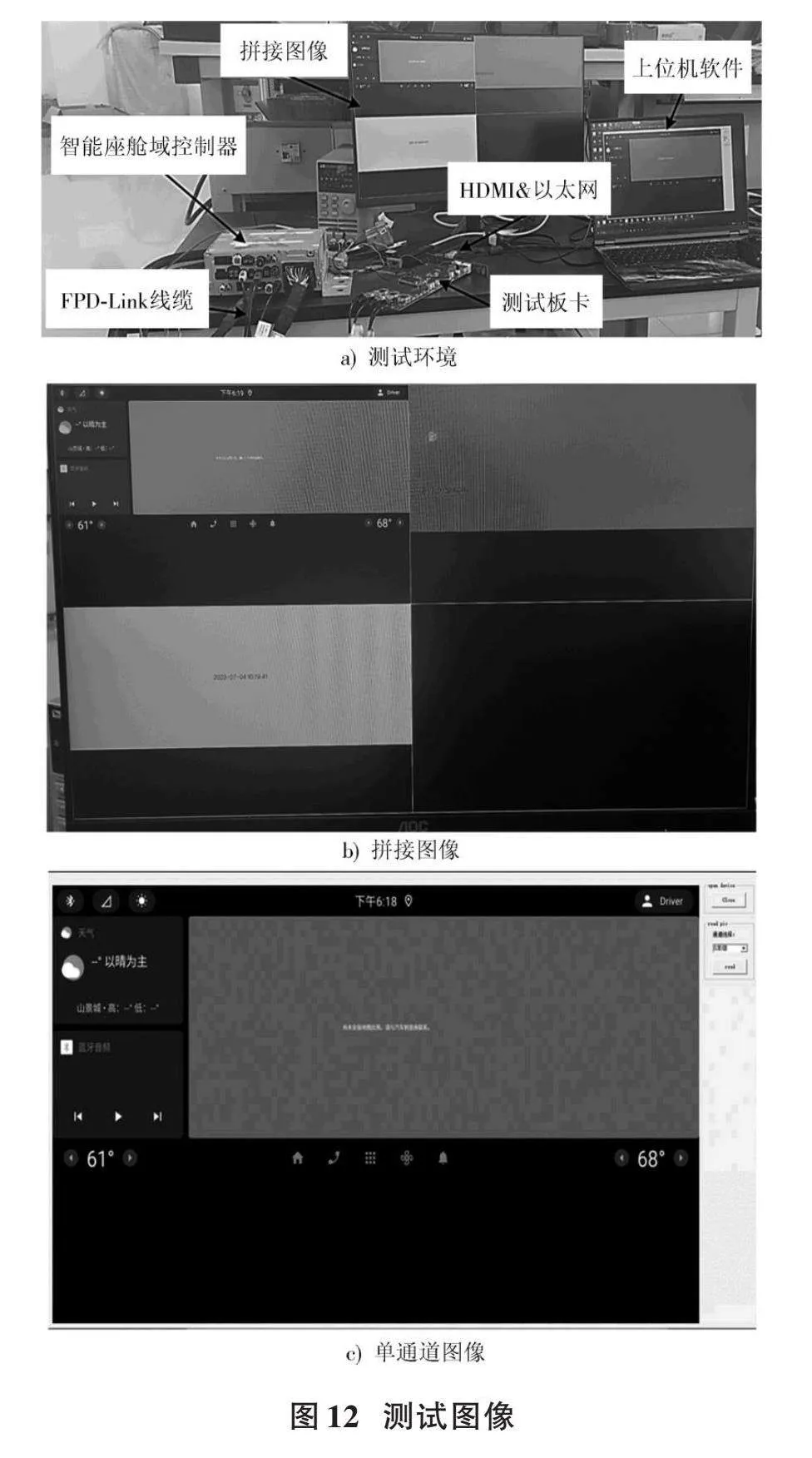

系统关键模块测试无误后,实物测试平台搭建如图12a)所示。智能座舱域控制器通过FPD⁃Link Ⅲ线缆连接至测试板卡,经板卡处理的数据分别通过HDMI和以太网传输至显示器和上位机。三路拼接图像如图12b)所示,上位机单通道采集图像如图12c)所示。从检测结果来看,系统可正确接收处理三路FPD⁃Link Ⅲ视频流。显示器上拼接的1 080P视频显示流畅,画面无撕裂;上位机能快速切换、显示并采集各路未压缩的视频图像,以进行FPD⁃Link Ⅲ质量检测。由于工业现场需对多个域控制器进行同时自动化检测,而采用人力进行逐路检测效率低下、易产生主观偏差,因此在FPD⁃Link Ⅲ自动化测试中,采用SSIM算法实现图像相似度检测。其相似度检测函数如下:

[SSIM(x,y)=l(x,y)α⋅c(x,y)β⋅s(x,y)γ] (1)

[l(x,y)=2μxμy+C1μ2x+μ2y+C1] (2)

[c(x,y)=2σxσy+C2σ2x+σ2y+C2] (3)

[s(x,y)=σxy+C3σxσy+C3] (4)

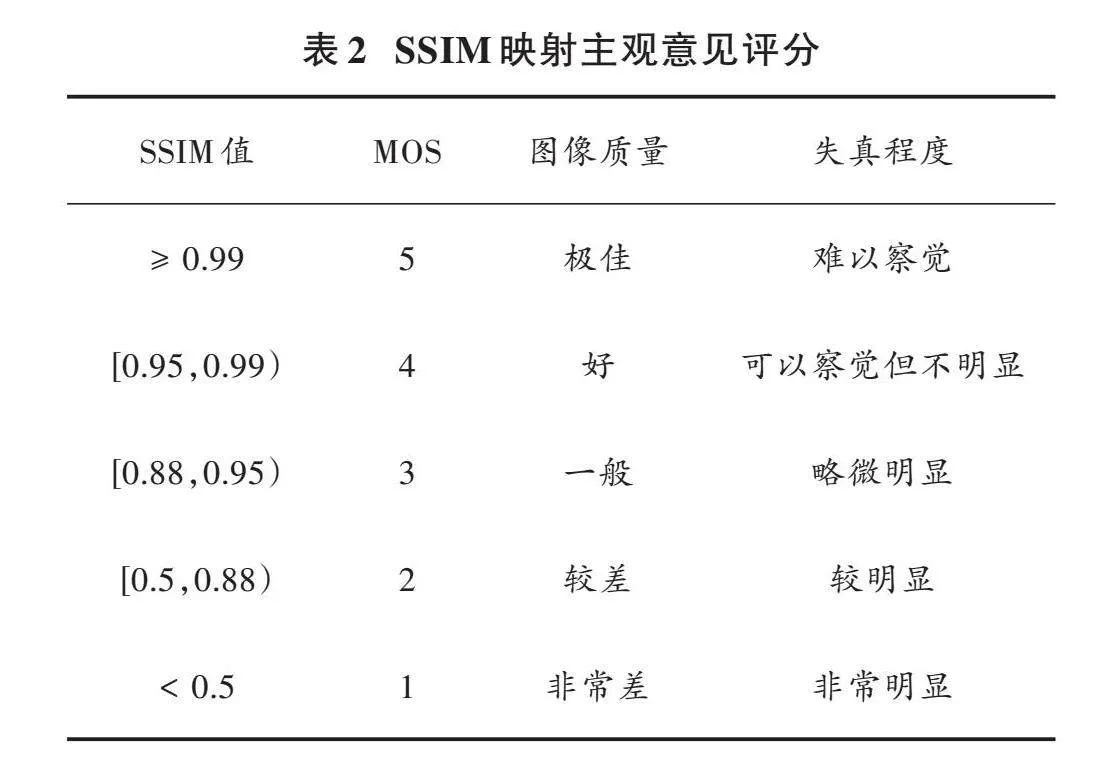

式中:[l(x,y)]为亮度比较;[c(x,y)]为对比度比较;[s(x,y)]为结构比较;通过三个不同的权重系数[α、β、γ]完成整体的SSIM指数评定。相较于其他算法,SSIM不仅考虑像素值差异,还充分考虑了亮度、对比度和结构三个方面的信息,使其更加接近人类感知[13]。SSIM值映射至主观意见评分MOS如表2所示[14]。

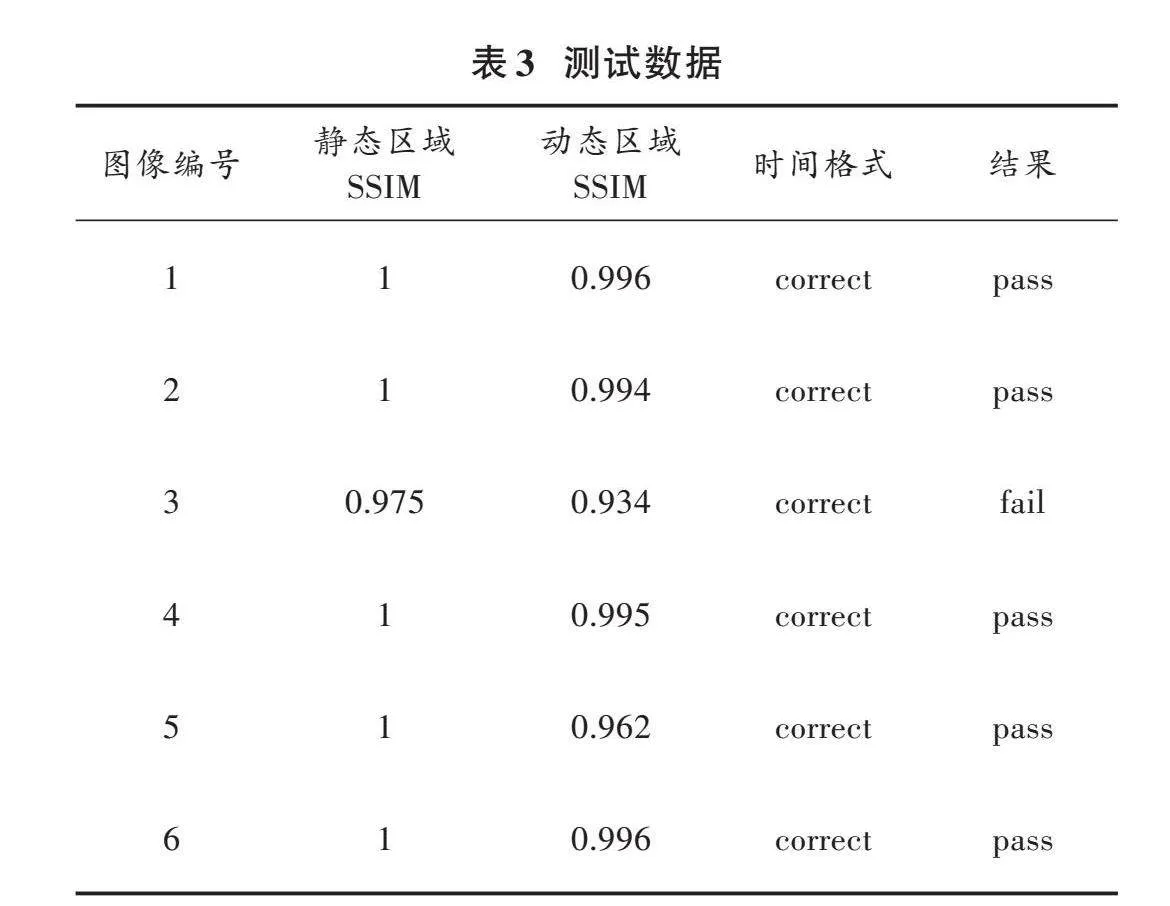

智能座舱域控制器FPD⁃Link Ⅲ输出的仪表图像只有时钟显示区域发生变化,通过区域分割,将采集图像划分为时钟变化动态区域和静止图像区域。动态区域变化的总时间像素点约为35 000个,将周围像素值代入时间像素点,得到SSIM值约为0.956。

由此并结合表2给出:测试图像的SSIM评价标准为静态区域≥0.99,动态区域gt;0.956。与此同时,对动态区域变化时钟进行OCR提取识别,若提取字符也符合YYYY⁃MM⁃DD HH⁃MM⁃SS时间格式,则输出pass以示测试通过。

部分测试数据如表3所示。

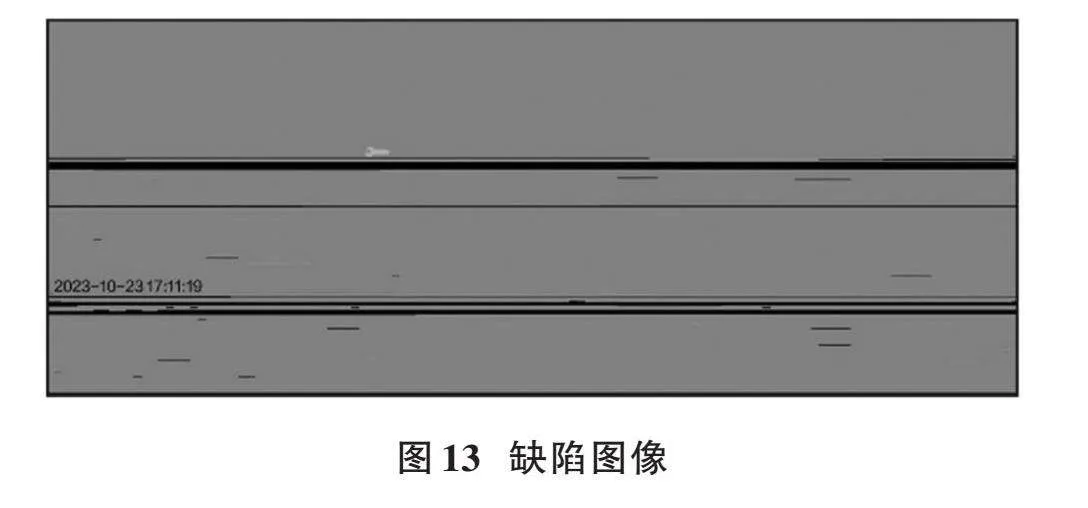

对测试记录进行检查,发现一路尽管时间识别正确,但静态与动态区域SSIM值均显著偏小,检查如图13所示的通道采集图像,发现有条状缺陷。结合自动化检测报警机制,测试人员只需查看报警信息,即可快速从多个被测产品中定位异常通路并进行故障排查,大大提高了检测与故障响应效率。lt;E:\未做件\现代电子技术202502\Image\22T12.tifgt;

5" 结" 语

相较于传统视频接口,FPD⁃Link Ⅲ因其高速率、差分传输与串行编码等特点,目前尚无成熟的检测方案。本文设计系统借助ZYNQ强大的并行处理能力与定制化优势,高效完成多路智能座舱域控制器FPD⁃Link Ⅲ信号的接收与恢复。本文通过时间格式比对和设置,以0.956与0.99为SSIM相似度阈值,给出了图像质量评价方案,其相较于其他算法更加贴近人眼主观感受,最终实现了对FPD⁃Link Ⅲ信号质量与完整性的自动化检测与判断。该系统现已在某汽车制造有限公司正式投入使用,实践应用表明其能完成预期测试目标,填补了FPD⁃Link Ⅲ检测领域的空白。此外,智能座舱域控制器还集成了CAN、USB、以太网等接口,未来可进一步整合这些接口的检测,积极推动高阶智能驾驶仿真测试发展,建设更加全面、高效的检测平台。

注:本文通讯作者为郑永军。

参考文献

[1] 郁淑聪,孟健,郝斌.基于驾驶员的智能座舱人机工效测评研究[J].汽车工程,2022,44(1):36⁃43.

[2] 刘尧,李亚楠.智能座舱多模态交互技术发展现状及趋势[J].汽车实用技术,2023,48(1):182⁃187.

[3] 杜曾宇,黄晓延,蒙锦珊.智能座舱的关键技术[J].时代汽车,2021(5):143⁃144.

[4] 张赫,李刚,张叶.手机摄像头MIPI⁃PHY的FPGA实现与显示[J].液晶与显示,2014,29(4):553⁃558.

[5] 贾建禄,王建立,郭爽,等.基于Camera Link的高速图像采集处理器[J].液晶与显示,2010,25(6):914⁃918.

[6] HUO H Y, MEI Z Y. Research on the coding of vehicle camera system [C]// 2020 5th International Conference on Mechanical, Control and Computer Engineering (ICMCCE). Harbin: IEEE, 2020: 660⁃663.

[7] KER M D, WU C H. Design on LVDS receiver with new delay⁃selecting technique for UXGA flat panel display applications [C]// 2006 IEEE International Symposium on Circuits and Systems (ISCAS). Kos, Greece: IEEE, 2006: 4.

[8] 张平,李磊,平新建.基于域控制器的硬件架构及FPD⁃Link Ⅲ关键技术研究[J].上海汽车,2021(10):37⁃42.

[9] 邱永华.一种基于医疗硬管内窥镜高清图像采集方案的设计[J].电子技术,2018,47(2):53⁃54.

[10] 白书尧,何贻珺,王若尘.多制式视频转换切换显示模块设计[J].信息技术与信息化,2023(2):168⁃171.

[11] 徐晓明,赵清潇,赵宪臣.采用FPD⁃Link Ⅲ技术实现数字视频信号远传设计[J].电子设计工程,2016,24(22):138⁃141.

[12] 谭景甲,何乐生,王俊,等.基于Zedboard平台AXI DMA数据传输与显示的设计[J].电视技术,2018,42(6):41⁃45.

[13] 吴兰,范晋卿,文成林.道路交通模糊图像多尺度清晰化复原方法研究[J].现代电子技术,2022,45(9):21⁃28.

[14] ZANFORLIN M, MUNARETTO D, ZANELLA A, et al. SSIM⁃based video admission control and resource allocation algorithms [C]// 2014 12th International Symposium on Modeling and Optimization in Mobile, Ad Hoc, and Wireless Networks (WiOpt). Hammamet, Tunisia: IEEE, 2014: 656⁃661.