倒装集成电路可靠性研究

摘 要:随着封装技术的发展,倒装焊技术在集成电路领域的应用日益广泛,其可靠性问题也受到了更多的关注。本文深入探讨了倒装集成电路的结构特点、失效模式,并对关键工艺过程进行了系统分析。通过工艺试验方法的研究和试验验证,提出了倒装集成电路的工艺过程试验检验要求,并对X射线和超声检测的判据进行了试验确认。

关键词:倒装,失效判据,试验

DOI编码:10.3969/j.issn.1002-5944.2024.23.033

0 引 言

倒装封装在满足集成电路引出端数量提升、封装体积/重量减少和高频性能提供等方面具备许多优势,因此被认为是一种适用于核心高端芯片的最佳封装解决方案。

倒装封装被广泛应用于核心高端芯片,如CPU(中央处理器)、GPU(图形处理器)、DSP(数字信号处理器)、FPGA(现场可编程门阵列)和网络交换电路等。它为这些芯片提供了高性能、高密度和轻量化的封装解决方案,有助于推动电子产品的创新和发展。

随着电子系统对国产集成电路的可靠性提出更高要求,急需开展倒装集成电路产品的可靠性评估、关键工艺过程控制以及失效分析等工作,但是目前缺乏相关标准及规范。

本文通过对倒装集成电路的结构、工艺分析,通过试验验证,提出倒装集成电路的工艺过程试验检验要求。

1 倒装封装集成电路工艺和失效模式

1.1 倒装工艺

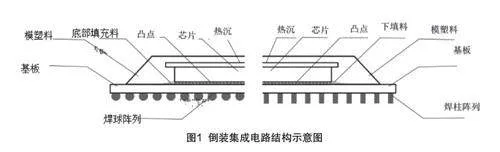

倒装集成电路的产品结构如图1所示,一般由、芯片、热沉、凸点、下填料(底部填充料)、模塑料、焊球/焊柱等几部分组成。

倒装集成电路的封装工艺主要有以下七步骤。

第一步:芯片底部金属化(或凸点下金属化层)(UBM,under bump metallization),这一步骤是为了在芯片底部创建金属化层,以便后续与进行互连。UBM通常使用金属材料如铜、镍或钛等,用于提供电流传导、防止锡的扩散以及增强焊接强度。

第二步:芯片上制作凸点,这一步骤主要是在芯片表面上制造凸点,用于在倒装过程中与进行连接。有多种方式可实现,例如蒸发/溅射法、焊膏印刷-回流法、化镀法、电镀法、钉头法、置球凸点法和转移法等。

第三步:芯片和焊盘互连(倒装芯片),这一步骤是将制作好的芯片与上的焊盘进行互连。常见的方式包括回流焊接、热压焊接、热声焊接和导电胶连接等。

第四步:底部填充,这一步骤用于填充芯片底部的空隙,以增加机械强度、提高散热性能和保护芯片。底部填充有两种主要方式:底部流动填充和底部不流动填充。填充材料常用的有树脂、胶粘剂等。

第五步:片式元件安装(适用时),将片式元件安装到芯片或基板上,可提供为产品电源稳定性、储能功能、信号耦合和解耦,以及抑制电磁干扰的作用。

第六步:热沉粘接(适用时),在某些情况下,为了提高倒装芯片的散热性能,可以使用热沉进行粘接。热沉通常由金属制成,并具有较好的导热性能,可通过与芯片和基板接触来有效散热。

第七步:焊球/焊柱(适用时),通过热压或回流焊接的方式将焊球/焊柱连接到焊盘上。

1.2 主要失效模式

根据上述倒装集成电路的工艺过程分析,可以梳理出倒装集成电路常见的失效模式有以下五种。

(1)焊点热疲劳失效:长时间以高温工作时,焊点可能会发生热膨胀和收缩,导致焊点材料的疲劳损伤。这可能导致焊点断裂、电性能下降或电连接中断。

(2)机械应力致互连撕裂失效:由于应力不均匀或温度变化等因素,互连结构(如焊盘、凸点等)受到机械应力,可能导致互连结构的撕裂。这会导致焊盘或凸点与芯片/基板之间的连接中断。

(3)下填料分层开裂失效:下填料在底部填充过程中可能出现分层或开裂现象,特别是在温度循环或机械应力作用下。这会导致填充胶与芯片/基板之间的界面不稳定,影响封装的可靠性。

(4)化学腐蚀失效:在倒装芯片封装过程中,存在某些环境因素可能引起化学腐蚀。这可能导致金属材料的腐蚀破坏,进而导致焊点或互连结构失效。

(5)电迁移失效:在倒装芯片中,由于电流通过焊点、凸点等导体结构,会引起离子迁移现象。长时间以高电流工作时,离子迁移可能导致互连结构的损坏、断裂或短路,从而导致封装失效。

倒装集成电路的失效模式多种多样,失效形式是一种或几种共同作用的结果,失效还跟基板材料、基板及芯片尺寸,凸点材料及结构和尺寸、基板焊盘材料及其与基板粘附、底部填充料有关。

2 工艺过程检验方法

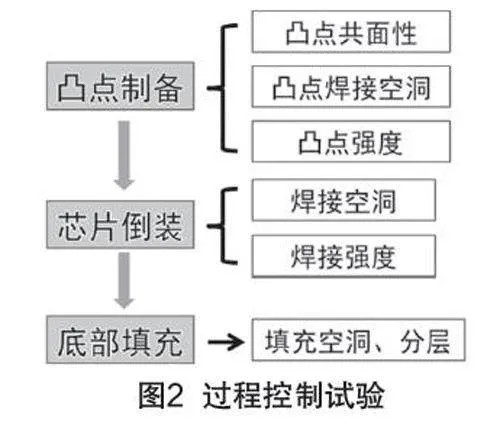

通过严格控制工艺环节并采取相应的检测措施,可以有效地降低倒装集成电路的失效风险并提高产品的可靠性,检验要求如图2所示。

针对组装工艺过程中可能出现的失效,需进行必要的检验,相关试验主要包括:凸点共面性、凸点剪切、芯片拉脱、芯片剪切、超声检验、X射线。

2.1 凸点共面性

凸点共面性是用来描述芯片上各个凸点与基准平面之间的距离,它是评估凸点一致性的重要指标。共面性越小,表示凸点之间的高度差越小,凸点的位置分布越一致,这意味着倒装芯片的焊点连接更加可靠[1]。

如果凸点共面性过大,也就是凸点与基准平面之间的距离较大,可能会导致以下问题:

焊点无法正常焊接:共面性过大可能导致焊盘高低不平,使得焊点无法与基板焊盘正常连接,从而影响焊接质量和可靠性。

虚焊:共面性不好可能导致某些凸点处于虚弱位置,无法实现有效的焊接,从而出现虚焊问题,即焊点与基板没有真正结合在一起。

为了评估凸点共面性,通常采用基准面法或最小二乘法:

基准面法:通过在基准平面上选择多个基准点,并测量各凸点到这些基准点的垂直距离来计算凸点共面性。这种方法需要确定一个可靠的基准平面,并且需要高精度的测量设备。

最小二乘法:通过采集大量的凸点高度数据,并利用最小二乘法拟合出一个最佳平面,然后计算凸点到该平面的垂直距离。这种方法可以对多个凸点进行统一分析,更加全面。

通过评估凸点共面性,可以及早发现凸点位置偏移或不一致的问题,并优化倒装芯片的设计和制造过程,以提高焊接质量和倒装芯片的可靠性。

2.2 凸点剪切

凸点剪切力是用来评估倒装芯片凸点的制备质量和抗剪切能力的指标。它描述了应用在凸点上的力所产生的剪切应力。确保凸点剪切力满足最小剪切力要求可以提高倒装芯片的可靠性。

最小剪切力是指倒装芯片中每个凸点所需的最小剪切力量。如果凸点的剪切力低于最小剪切力要求,可能导致以下问题:

(1)凸点脱落:凸点在工作过程中受到外部力的作用,如果剪切力不足以保持凸点与基板之间的牢固连接,就会出现凸点脱离的情况,从而导致焊点失效或设备故障。

(2)电迁移:凸点之间的电流通过焊点流动,如果凸点的剪切力不足以提供足够的电流通道,就会导致电迁移现象,从而影响芯片的电性能和可靠性。

2.3 芯片拉脱或芯片剪切

倒装芯片后焊点位于芯片和基板之间,内部焊点不能通过光学显微镜直接观察到,所以倒装芯片焊接缺陷检查成为倒装芯片工艺质量控制的关键难点之一。为了保障倒装芯片的焊接质量,可以采用剪切或拉脱测试来评估芯片与基板之间的抗剪切/拉脱强度或底部填充工艺质量。

剪切测试是一种常用的手段,通过施加垂直于芯片表面的剪切力来检验焊点的强度。该测试方法需要使用专用设备,将倒装芯片置于夹具中,然后施加适当的剪切力来模拟芯片在使用条件下的受力情况。通过测量施加到芯片上的剪切力和导致焊点剪切断裂的最大力值,可以评估焊点的抗剪切强度。如果焊点强度不足,剪切测试可能导致焊点断裂,暴露出焊接质量问题。

拉脱测试则是通过施加垂直于芯片表面的拉力来检验焊点的强度。该测试方法同样需要专用设备,倒装芯片被夹持在上下两个夹具之间,然后施加逐渐增加的拉力。通过测量导致焊点断裂的最大拉力值,可以评估焊点的抗拉脱强度。如果焊点强度不足,拉脱测试可能导致焊点断裂,暴露出焊接质量问题。

2.4 X射线

倒装芯片后焊点位于芯片和基板之间,内部焊点不能通过光学显微镜直接观察到,为了保障倒装芯片接质量,通过使用X射线检测设备,可以对倒装芯片进行非破坏性检测。X射线能够穿透芯片和基板,通过对射线的散射和吸收情况进行分析,可以探测到焊点的结构和缺陷。X射线检查可以帮助发现焊点周围是否存在空洞、畸变、偏移等问题,从而评估焊接质量并进行相应的调整和改进[2]。

芯片与基板的临时对位,需要对装片机的装片速度、装片力的大小、芯片对中过程的控制等,最后将芯片贴在对应的涂有助焊剂的基板焊盘上。芯片与基板的贴装将直接影响凸点与焊盘的回流焊过程,因此需要开发合适的工艺参数,控制合适的偏移量,确保最终凸点焊接的质量与可靠性,如图3所示。

倒装焊后焊点位于芯片和基板之间,内部焊点不能通过光学显微镜直接观察到,所以倒装焊焊接缺陷检查成为倒装焊工艺质量控制的关键难点之一。为保障倒装焊焊接质量,通过X射线检查倒装焊点偏移、桥连及焊点空洞等缺陷。

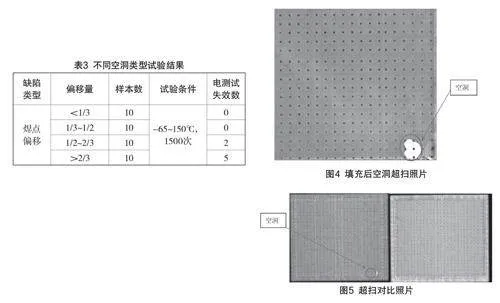

针对倒装焊点偏移量、空洞缺陷,对样品进行相关试验,分析其对焊接质量的影响。抽取空洞和偏移的电路,按照-65~150℃循环1500次的条件进行温度循环试验。结果带空洞电路于1000次循环开始发生失效,未产生空洞电路未失效。失效位置为偏移过大或有空洞的焊点。

为确定焊点空洞的判据,选取不同总空洞面积电路各20只进行上述温度循环试验,具体试验条件及结果如表1所示。

由结果可知当总空洞率大于20%时电路出现失效,并随着空洞率增大,失效数量也随之增多。

同针对单个空洞进行上述温度循环试验,具体试验条件及结果如表2所示,由结果可见,单个空洞大于10%电路出现失效。

针对焊点偏移尺寸进行上述温度循环试验,具体试验条件及结果如表3所示,由结果可见当偏移大于1/2焊盘直径时出现失效。

根据上述试验,总结得出X射线的试验判据标准如下:

(a)单个焊点的最大空洞直径大于焊点直径的10%;

(b)空洞面积大于焊点横截面最大面积的20%;

(c)器件上焊点总的空洞面积大于焊点截面总面积的10%;

(d)出现桥连、多球、少球等焊接缺陷;

(e)焊点出现偏移且偏移量大于焊点直径的1/2。

2.5 超声检测

底部填充工艺主要利用液体的毛细作用使底部填充材料流到芯片底部,并在一定温度下固化形成对封装的保护。通过底部填充增加了封装的机械强度,在温度发生变化时部分吸收由于热膨胀系数的不匹配产生的应力和形变,从而提高倒装芯片的可靠性。底部填充流动性不好会发生填充不完全,导致填充层空洞的形成从而引发可靠性问题,如果空洞在焊点周围存在会形成局部应力集中导致焊点早期失效。

底部填充可增加封装的机械强度,并缓解由于芯片与基板热膨胀系数不匹配产生的应力和形变,从而提高封装的可靠性[3]。底部填充过程中,如果流动性不好会发生填充不完全,从而出现空洞和分层,引发质量与可靠性问题。为了检测底部填充过程中潜在的界面分层缺陷,超声扫描是一种非常有用的方法。超声扫描利用超声波在材料中传播的特性,通过对声波的反射、折射和散射等数据进行分析,可以检测出填充材料中的内在界面分层缺陷。通过超声扫描,可以评估填充材料的均匀性和完整性,发现可能存在的空洞、分层或其他缺陷,并及时采取措施进行修正。

针对底部填充容易产生的缺陷类型及缺陷尺寸,采用样品进行相关试验,分析各类缺陷对底部填充质量影响。

针对尺寸为22 mm×20 mm、间隙为80~90 um的芯片进行底部填充。填充后空洞如图4所示。

抽取有空洞电路及未产生空洞样品,按照-65~150℃循环2000次的条件进行温度循环试验。结果带空洞的样品于1000次循环失效,未产生空洞样品未失效。失效位置为空洞处焊点,对失效焊点进行分析发现焊点开裂。经分析认为该处由于没有填充胶保护,由热膨胀系数的不匹配产生的应力和形变致使该处较其他位置先失效。

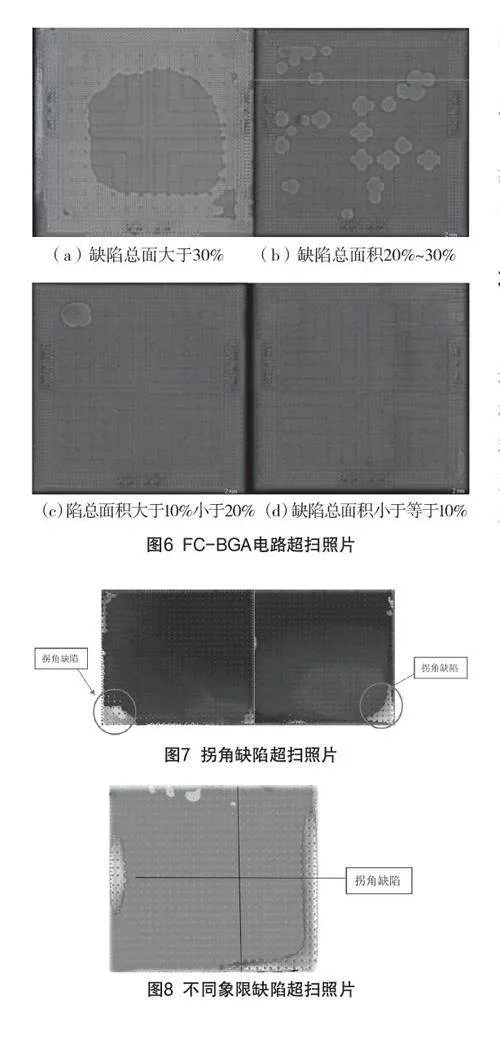

为确定底部填充空洞判据,选取总空洞率不同样品各20只进行上述温度循环试验,具体超扫结果结果如图6所示。经试验,当总空洞率大于20%时电路出现失效,并随着空洞率增大,失效数量也随之增多。其中发现当空洞于某一区域聚集时,电路失效较明显。为验证该情况具有普适性,选取其他倒装封装电路进行相同的验证试验。

针对缺陷位置进行了相关试验,首先针对拐角空洞与非拐角空洞添加对比试验,图7、图8为拐角空洞超扫图。经试验验证,当拐角空洞大于5%,单个空洞大于10%电路出现失效,并随着空洞率的增大,失效数量随之增多。

根据上述试验,总结得出超声检测的试验判据标准如下:

(a)底部填充区多个空洞总和超过应该具有的总底部填充区的 20%;

(b)超过总填充区10%的单个空洞,或超过总底部填充区5%的单个拐角空洞;

(c)当用平分方法把图像分成四个面积相等的象限时,任一象限中的空洞超过该象限预计的填充区面积的30%。

3 结 语

本文对倒装集成电路工艺过程、失效模式和检测方法进行了系统研究,并基于试验数据分析,确立了X射线、超声扫描在检查焊点空洞、焊点偏移等关键参数的判据标准,这些试验判据标准可以为行业提供参考依据,有助于提高倒装集成电路产品质量的一致性和可靠性。

参考文献

[1]吕晓瑞,林鹏荣,刘建松,等.倒装焊封装工艺缺陷及检测方法研究[J].信息技术与标准化,2021(7):16-20.

[2]王爽.三维X射线检测技术在倒装焊器件中的应用[J].电子测试,2018(24):31-33.

[3]陈志健,高娜燕,罗佳明.倒装工艺中底部填充胶孔洞的分析与改善[J].电子产品可靠性与环境试验,2020,38(4):94-97.

作者简介

李锟,本科,高级工程师,研究方向为半导体集成电路领域标准化。

(责任编辑:张瑞洋)