一种高PSRR低温漂无运放带隙基准

摘" 要: 针对无运放带隙基准电压源温度特性及电源抑制比差的问题,设计一种高电源抑制比、低温漂的无运放带隙基准电路。该电路通过电流镜进行钳位,避免运算放大器失调电压对输出基准的影响,利用晶体管栅极与三极管基极生成稳定的补偿电流,以降低基准电压的高阶温度系数,输出端采用共源共栅结构提高电源抑制比。基于SMIC 0.18 μm BCD工艺在Cadence环境下对电路进行仿真,仿真结果表明:在-40~125 ℃范围内,电路的温度系数为3.187×10-6 /℃,10 Hz时电源抑制比为-88.6 dB,1 MHz时电源抑制比为-50.2 dB。在考虑启动电路影响的情况下,电路在5 V电源下的静态电流为3.78 μA,带隙基准的版图面积为160 μm×183 μm。可实现对基准电压高阶温度项的补偿,降低温度系数,并在没有滤波电容的条件下提高带隙基准的PSRR。

关键词: 带隙基准; 无运放; 电源抑制比; 温度系数; 补偿电流; 启动电路

中图分类号: TN41⁃34" " " " " " " " " " " " " "文献标识码: A" " " " " " " " " " " " " 文章编号: 1004⁃373X(2024)23⁃0171⁃05

A high⁃PSRR and low⁃temperature drifting op⁃amp⁃free bandgap reference

WANG Kai1, ZHANG Fanghui1, YANG Xu2, WANG Yichen1, LI Ziteng1

(1. School of Electronic Information and Artificial Intelligence, Shaanxi University of Science and Technology, Xi’an 710021, China;

2. School of Automation and Information Engineering, Xi’an University of Technology, Xi’an 710048, China)

Abstract: A high power supply rejection ratio (PSRR) and low⁃temperature drifting op⁃amp⁃free bandgap reference voltage source circuit is designed to improve the temperature characteristics and PSRR of the op⁃amp⁃free bandgap reference voltage sources. In this circuit, a current mirror is utilized to clamp the output voltage, thereby mitigating the impact of the operational amplifier′s offset voltage on the output reference. A stable compensation current is generated by leveraging the transistor′s gate and the triode′s base, effectively reducing the high⁃order temperature coefficient of the reference voltage. In the output terminal, a common source common gate structure is employed to enhance the PSRR. The circuits is simulated in the Cadence environment based on the SMIC 0.18 μm BCD process. The simulation results indicate that within the temperature range of -40 to 125 ℃, the circuit′s temperature coefficient is 3.187×10-⁶/℃. The PSRR is -88.6 dB at 10 Hz and -50.2 dB at 1 MHz. Considering the impact of the startup circuit, the quiescent current of the circuit is 3.78 μA under a 5 V power supply, and the layout area of the bandgap reference is 160 μm×183 μm. To sum up, the designed circuit can compensate the high⁃order temperature term of reference voltage, reduce the temperature coefficient, and improve the PSRR of bandgap reference without filter capacitor.

Keywords: bandgap reference; op⁃amp⁃free; PSRR; temperature coefficient; compensating current; startup circuit

0" 引" 言

带隙基准电路是集成电路中的关键功能模块,主要用于提供稳定、准确的输出电压。在数据转换器、电源转换器、低压差稳压器和存储器等模拟和混合信号集成电路中,精确的参考电压是确保系统性能和稳定性的必要条件。带隙基准电路能够在不同工艺角、温度和供电电压条件下提供稳定的输出电压,因而被广泛应用。

目前,带隙基准电路分为有运放和无运放两种类型。文献[1]介绍了一种低压带隙基准电路,具有较低的供电电压和较高的电源抑制比(PSRR),适用于对电源噪声要求较高的应用场景。然而,该技术引入额外的电流会增加功耗,在低供电电压下尤为突出。文献[2]提出的CMOS电路采用反馈环路实现低电压、低功率和高PSRR,但其精度可能不如有运放的结构。文献[3]提出了一种带有源随器的CMOS基准电路结构,但由于器件温度特性的影响,导致温度漂移较大。文献[4]利用MOS管在亚阈值区的温度特性进行补偿,但亚阈值区MOS管对工艺参数要求较高,不同工艺导致器件性能不稳定,不易实现。

因此,本文介绍了一种新型的无运放带隙基准电路设计方案,通过特定的电路结构实现对基准电压高阶温度项的补偿,降低温度系数,并在没有滤波电容的条件下提高了带隙基准的PSRR。

1" 传统带隙基准电路结构

带隙基准电压是基于CTAT(Complementary To Absolute Temperature)电压和PTAT(Proportional To Absolute Temperature)电压的叠加,以产生稳定的参考电压。当CTAT和PTAT电压平衡时,产生的基准电压与温度无关,从而实现温度补偿。

1.1" 传统有运放带隙基准电路

如图1所示为传统有运放的带隙基准电路[5],其中[X]和[Y]节点由运算放大器输入端控制。

三极管(BJT)[Q1]和[Q2]的基极⁃发射极压差通过电阻[R1]产生PTAT电流,通过电流镜等比例复制到基准电压输出支路形成参考电压[VREF]。

[VREF=VBE3+VTlnN×R2R1] (1)

CTAT电压([VBE])的负温度系数约为-2 mV/℃,而PTAT电压([ΔVBE])的正温度系数约为0.087 mV/℃。适当选择[R2 R1]比例可实现温度系数较低的参考电压。由于PTAT电流产生环路受到三极管集电极电流和放大器输入共模电压的限制,传统参考电路在低电压条件下无法工作,因此需要采用电流模式架构来解决此问题。

1.2nbsp; 传统无运放带隙基准电路

如图2所示为无运放带隙基准电路结构[5],其工作原理如下:MOS管构成共源共栅形式的电流镜,通过互相复制形成反馈回路,使得[X]和[Y]点电压相等,从而实现运放钳位的功能。

[VREF=VBE3+ΔVBER2R1=R2R1VTlnN+VBE3] (2)

输出电压与温度关系为:

[∂VREF∂T=∂VBE3∂T+kqlnN1+R2R1] (3)

无运放带隙基准电路不需要运放来放大参考电压,具有较低的功耗,也不需要考虑运放的性能参数和环路稳定性问题,电路设计简单。但其缺乏放大参考电压的功能,对电源噪声的抵抗能力较差。

在无运放带隙基准电路的基础上,本文设计了一种低温漂、低功耗、高PSRR性能的带隙基准电路。

2" 电路结构及原理分析

本文设计的带隙基准电路包括带隙核心电路和启动电路。带隙核心电路采用无运放负反馈结构,利用电流镜进行钳位,并在输出端采用共源共栅结构以提高PSRR。引入高阶温度补偿电路,通过产生指数型补偿电压调节[VREF]的温度系数,使其在不同温度下保持稳定。启动电路确保电路能够顺利进入正常工作状态,消除简并点问题。

2.1" 启动电路

为了解决带隙基准电路可能出现的简并点问题,设计了一种自启动电路,如图3左侧所示。当电源通电时,反相器启动并产生使能信号。该信号与电阻[R1]提供的电平信号共同作用,使得MOS管MP10所在支路导通,形成对地通路,为MN6、MN7电流镜提供稳定电压。随后,将电流复制给Fb支路,消除带隙核心电路的简并点,使其顺利进入正常工作状态。

一旦带隙基准电路开始正常运行,MP1的栅极电压逐渐升高,通过电阻[R2]传递开启电压至MP9的栅极使其打开,MN3、MN5电流镜开始工作,导致MN6的漏极电压通过MN5传输到地,自启动电路退出工作状态。此时,MP10支路仍保持导通状态。通过将MP10、MP12~MP16、MN5和MN6宽长比设计为远小于1,可以最小化功耗,同时自启动电路通过Start_v信号与核心电路形成反馈回路,检测并调节自启动电路的输出。

2.2" 带隙核心电路

带隙基准核心电路由三极管Q1、Q2、Q3和MOS管NMOSFET1、NMOSFET2、MP7、MP8以及电阻[R3]~[R5]组成。其中,Q1、Q2、Q3的发射极面积比为[N]∶1∶1。MP1~MP4采用低压共源共栅结构,其正温度系数压差[ΔVBE]可以表示为:

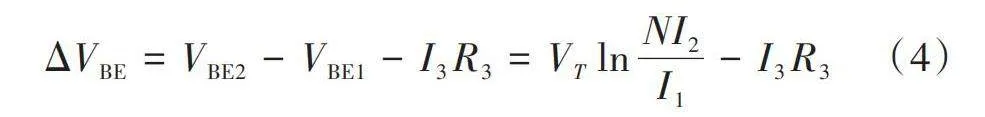

[ΔVBE=VBE2-VBE1-I3R3=VTlnNI2I1-I3R3] (4)

式中:电流[I2]为镜像[I1]的电流;[ΔVBE]通过电阻[R4]产生正温度系数电流[IPTAT]。

[IPTAT=VBE2-VBE1-I3R3R4=VTlnN-I3R3R4] (5)

电阻[R5]产生负温度系数电流[ICTAT]。

[ICTAT=VBE2R5] (6)

正温度系数电流与负温度系数电流相叠加得零温度系数电流[IO]。

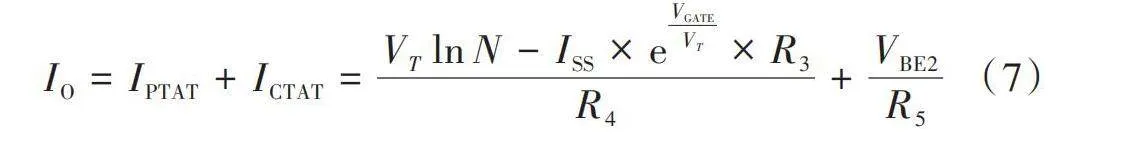

[IO=IPTAT+ICTAT=VTlnN-ISS×eVGATEVT×R3R4+VBE2R5] (7)

式中:[ISS]是场效应管的饱和电流;[VGATE]是MOS管的栅极电压。

同时零温度系数电流通过MP7、MP8组成的电流镜复制到输出支路与电阻[R6],产生零温度系数电压[VREF]。

2.3" 曲率补偿电路

传统型带隙基准电路通常仅采用一阶温度补偿,但为了获得更低的温度系数,需要对二阶温度系数进行补偿。本文提出一种新的补偿方法,将MOS管的栅极与三极管(BJT)的基极相连形成稳定的电流源,由于三极管具有高阶温度系数,通过控制栅极电压进而控制三极管的基极电压,可以产生指数补偿电流,流入电阻[R3]形成补偿电压。由于其栅极与基极相连,使得常规MOS管无法工作,因此采用耗尽型MOS管来代替。补偿原理分析如下。

三极管的高阶温度公式如下:

[VBE=VBEO+kTqlnIBISαT+βT-T02] (8)

式中:[VBE]是基级电压;[VBEO]是零温度基级电压;[k]是玻尔兹曼常数;[T]是温度;[q]是电子电荷;[IB]是基极电流;[IS]是饱和电流;[α]是温度线性系数;[β]是温度二次系数;[T0]是参考温度。

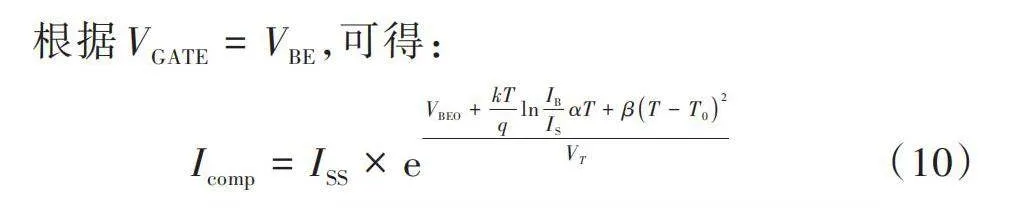

MOS管的栅极与BJT的基极相连构成的补偿电流为:

[Icomp=ISS×eVGATEVT] (9)

式中:[ISS]是场效应管的饱和电流;[VT]是温度电压,通常为[kTq]。

根据[VGATE=VBE],可得:

[Icomp=ISS×eVBEO+kTqlnIBISαT+βT-T02VT] (10)

电阻的二阶温度公式为:

[RT=R01+αT-T0+βT-T02] (11)

式中:[RT]是温度为[T]时的电阻值;[R0]是参考温度[T0]下的电阻值;[α]是电阻的温度系数,表示电阻值随温度变化的一阶变化率;[β]是电阻的二阶温度系数,表示电阻的温度系数随温度的变化率。

将电阻的二阶温度公式进行泰勒展开:

[R3R4=R3T0R4T0K1T-T0-1×1+K2T-T0+K22T-T02] (12)

式中:[K1]为[R3]的温度系数;[K2]为[R4]的温度系数。

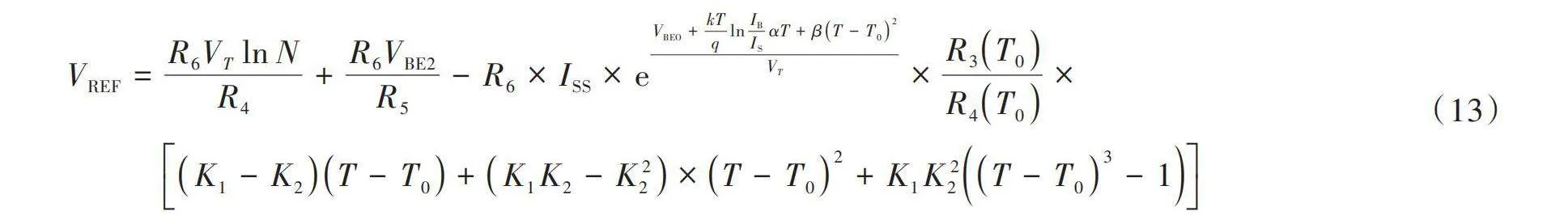

根据式(8)~式(12)得到补偿后的零温度带隙基准输出电压为:

从式(13)中可以看出,通过合理设计MOS管的栅极电压以及[R3]与[R4]的阻值,可以抵消公式中的高阶非线性项,降低电路的温漂系数。

2.4" 电路的PSRR推导

输出基准电压的表达式如下所示:

[VREF=VTlnN-I3R3R4+VBE2R5R6] (14)

进一步分析[VDD]对输出的影响。对于[VDD],设定[ΔVDD]为电源电压的变化量,则Q1和Q2的电流变化为:

[ΔID1=ΔID2=gm1∙ΔVgs1=gm1∙ΔVDD] (15)

式中:[gm2]是耗尽型MOS管的等效跨导;[ΔVgs1]为耗尽型MOS管栅源电压对电源电压的变化量。

电流镜的电流变化为:

[ΔImirror=(gm5+gm7)ΔVDD] (16)

负载电阻上的电压变化为:

[ΔVREF=(gm5+gm7)ΔVDD⋅R6] (17)

PSRR定义为电源电压变化对输出电压变化的比率。

[PSRR=ΔVDDΔVREF=1(gm5+gm7)⋅R6] (18)

式(18)表明,电流镜的跨导越大,MOS管对输入信号的影响越敏感,而负载电阻的大小也可以直接影响电路的PSRR。

3" 仿真结果分析

本文设计基于SMIC的0.18 μm BCD工艺,通过Cadence软件中的Spectre仿真环境对电路进行了全面验证。仿真涵盖了瞬态启动过程、温度系数、电源抑制比等关键性能参数,仿真结果如图4~图6所示。

图4展示了启动电路的工作时间曲线。电源电压从0 V迅速上升到5 V,通过瞬态仿真观察输出电压达到稳定所需的时间。结果表明,输出电压在经过10 μs后趋于稳定,证明了自启动电路的可靠性。

针对所提出的基准电路进行了温度稳定性模拟。在电源电压为5 V供电下,对整体电路进行静态工作点仿真,并设置温度范围为-40~125 ℃。仿真结果如图5所示,根据计算公式得出本文的温漂系数为3.187×10-6 /℃。

交流信号仿真设置为直流大信号5 V、交流小信号0.5 V,在1 Hz~1 GHz的频率范围内,通过观察输出点的电源抑制比曲线,如图6所示,在低频范围下,电路的PSRR达到-88.6 dB,在高频范围下仍有-50.2 dB的性能。

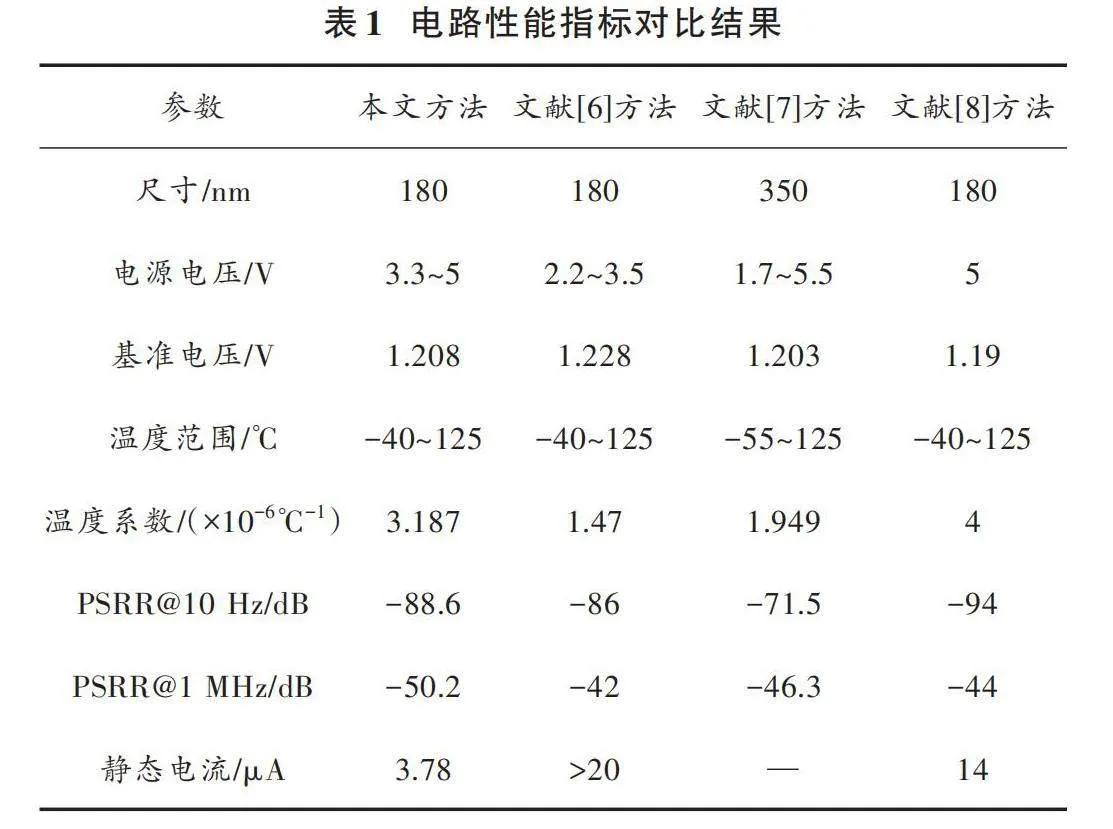

本文设计的无运放带隙基准电源在性能参数上与近几年其他文献中的结果进行了对比,如表1所示,显示出本文设计在低温度系数、高电源抑制比和低功耗方面的显著优势。

从表1中可知,本文提出的新型无运放带隙基准电路具有低温度系数、高电源抑制比和低功耗的特性,可以满足数字隔离电路等场合。

本文电路的版图布局如图7所示,包括启动电路和带隙核心电路两部分,版图的总面积为160 μm×183 μm。

4" 结" 语

本文提出了一种无运放带隙基准电路,结合高阶温度补偿电路及共源共栅结构,在降低基准电压高阶温度项的同时,简化了电路结构,提高了宽频带范围下PSRR的性能。在10 Hz时,PSRR达到-88.6 dB,在1 MHz时,PSRR仍保持在-50.2 dB。此外,电路温漂系数仅为3.187×10-6 /℃,静态电流为3.78 μA,芯片面积仅为0.018 mm2。综合考虑,该带隙基准电路适用于数字隔离器等对低功耗、高精度和高PSRR有需求的应用场合。

注:本文通讯作者为张方晖。

参考文献

[1] THAM K M, NAGARAJ K. A low supply voltage high PSRR voltage reference in CMOS process [J]. IEEE journal of solid⁃state circuits, 1995, 30(5): 586⁃590.

[2] MEHRMANESH S, VAHIDFAR M B, ASLANZADEH H A, et al. A 1⁃volt high PSRR CMOS bandgap voltage reference [C]// Proceedings of the 2003 International Symposium on Circuits and Systems. New York: IEEE, 2003: 381⁃384.

[3] 黄国城,尹韬,朱渊明,等.一种-100 dB电源抑制比的非带隙基准电压源[J].电子与信息学报,2016,38(8):2122⁃2128.

[4] 米磊,毛焜,聂海.一种无运放低温系数带隙基准源[J].成都信息工程大学学报,2017,32(1):41⁃43.

[5] BEHZAD R. Design of analog CMOS integrated circuits [M]. Amsterdam: Elsevier, 2016: 523⁃524.

[6] 王豪,代国定,唐文海,等.一种新颖的无运放高性能带隙基准设计[J].微电子学,2021,51(6):799⁃803.

[7] 熊辉,张涛,刘劲.一种低温漂的无运放带隙基准电压源[J].电子元件与材料,2023,42(6):729⁃735.

[8] 曹麒,罗萍,刘凡,等.一种高PSRR的无运放带隙基准电路[J].微电子学,2023,53(2):227⁃232.

[9] WU F Q, DENG H H, YIN Y S, et al. A high PSRR bandgap reference for LED driver [C]// IEEE Information Technology, Networking, Electronic and Automation Control Conference. New York: IEEE, 2016: 742⁃745.

[10] 丁大胜,徐世六,王永禄,等.一种分段温度补偿BiCMOS带隙基准源[J].微电子学,2012,42(3):340⁃343.

[11] 胡成煜,顾益俊,李富华.一种低功耗带隙基准电压源的设计[J].电子与封装,2017,17(2):13⁃16.

[12] 冯树,王永禄,张跃龙.一种新型无运放CMOS带隙基准电路[J].微电子学,2012,42(3):336⁃339.

[13] WANG B, LAW M K, BERMAK A. A precision CMOS voltage reference exploiting silicon bandgap narrowing effect [J]. IEEE transactions on electron devices, 2015, 62(7): 2128⁃2135.

作者简介:王" 凯(1998—),男,山西临汾人,硕士研究生,研究方向为模拟集成电路设计。

张方晖(1966—),男,山西临汾人,博士研究生,教授,研究方向为半导体技术。