一种低开销的三节点翻转容忍锁存器设计

摘 要:【目的】随着半导体技术的发展,集成电路特征尺寸不断缩小,导致其对软错误更加敏感,因此需要对集成电路存储单元进行加固。【方法】使用Hspice进行实验与仿真,基于PTM32nm CMOS工艺,提出了一种低开销的三节点翻转容忍锁存器结构。【结果】该锁存器包含2个单节点自恢复模块、1个二级错误拦截模块、3个传输门。每个自恢复模块由1个施密特触发器和1个钟控的施密特触发器组成,首尾相连形成环形结构,有效地实现了三节点翻转的容忍。【结论】仿真结果表明:与现有的其他功能相同的锁存器相比,所提出的锁存器具有完整的三节点容忍能力,并且将功耗、延迟、面积、功率延迟积分别降低了约37.58%、41.25%、27.77%、75.83%。

关键词:锁存器;软错误;三节点翻转

中图分类号:TN47 文献标志码:A 文章编号:1003-5168(2024)08-0009-05

DOI:10.19968/j.cnki.hnkj.1003-5168.2024.08.002

Design of a Low-Cost Triple-Node-Upsettolerant Latch

QIN Xuewei

(School of Computer Science and Engineering, Anhui University of Science and Technology, Huainan 232001, China)

Abstract: [Purposes] With the development of semiconductor technology, the shrinking feature size of integrated circuits has made them more sensitive to soft errors, necessitating reinforcement of the storage units in integrated circuits. [Methods] Experiments and simulations were conducted using Hspice. Based on the PTM32nm CMOS process, a low-cost triple node upsets tolerant latch (LTNTL) structure was proposed. [Findings] The latch consists of 2 single-node self-recovery modules, 1 secondary error interception module, and 3 transmission gates. Each self-recovery module consists of a Schmitt trigger and a clock-gating Schmitt trigger connected in a loop structure, effectively achieving tolerance to TNU. [Conclusions] Simulation results demonstrate that compared to other latches with same functions, the proposed latch has complete TNU tolerance capability and reduces power consumption, delay, area, and power-delay product by approximately 37.58%, 41.25%, 27.77%, and 75.83%, respectively.

Keywords: latch; soft errors; triple node upset

0 引言

自从半导体技术进入纳米时代以来,晶体管的尺寸显著减小,导致电路节点的临界电荷也显著减少。集成电路(IC)越来越容易受到高能辐射影响而发生错误[1]。当辐射环境中的中子、质子、α粒子、γ射线等高能粒子撞击电路的敏感区域时,在库伦作用下,会有电子空穴对沿着高能粒子的运动轨迹产生[2]。晶体管的漏极会收集这些产生的电荷,当收集到的电荷超过临界电荷时,电路的逻辑状态可能会发生变化,从而导致单节点翻转(SNU)的发生。近年来由于集成电路尺寸的进一步缩小,产生的电荷共享效应使双节点(DNU)和三节点(TNU)翻转也变得更普遍[3]。而锁存器是集成电路中最常用的时序结构,硬化锁存器以容忍这些错误已成为一个重要的课题。

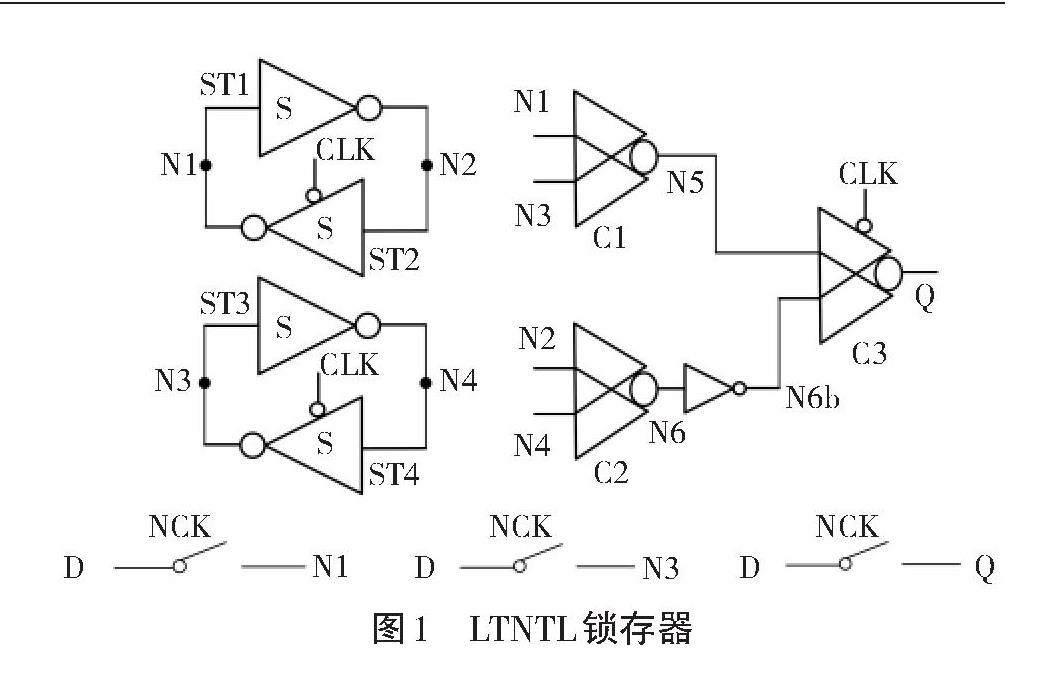

本研究设计了一种基于施密特触发器和C单元的高鲁棒性三节点容忍锁存器(LTNTL)原理,包含两个由2个施密特触发器组成的单节点自恢复模块和一个由3个C单元组成的错误过滤模块。当锁存器中出现错误时,可以防止错误传播到输出节点或直接恢复错误,实现最多三个节点的错误容忍。

1 加固锁存器设计

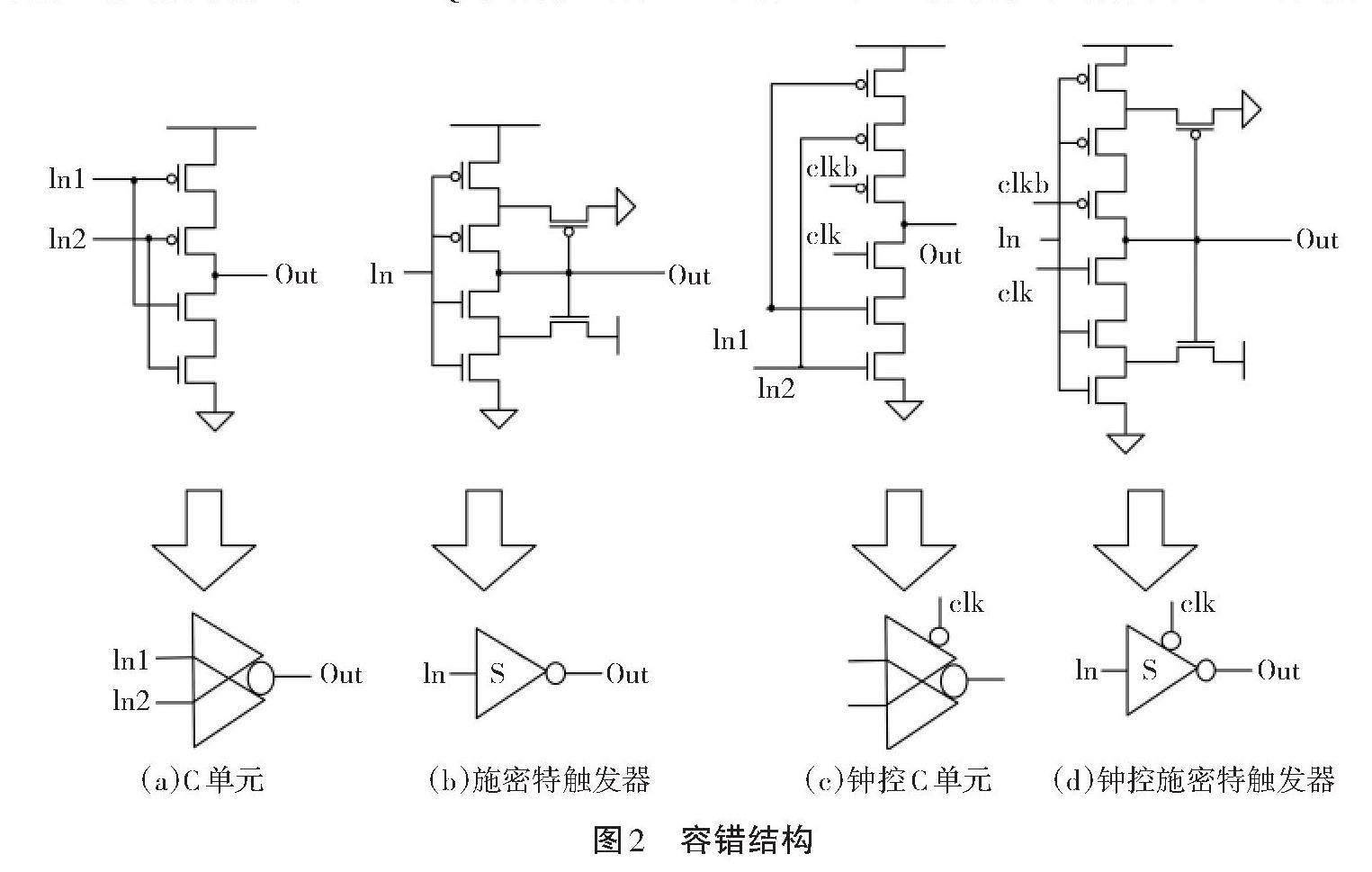

本研究所设计的LTNTL锁存器结构如图1所示。其中D和Q表示输入和输出;CLK和CLKB分别为系统时钟和负系统时钟;TG1-TG3是3个传输门;N1-N6和N6b是内部数据节点;ST1-ST4为施密特触发器,其中ST2和ST4上添加了时钟控制;C1-C3为C单元,其中C3也添加了时钟控制以降低功耗与延迟,并在C2添加了一个反相器以保证内部数据正确。C单元是一种常用的错误过滤元件[4],如图2中(a)(c)所示。它具有两个输入和一个输出,当两个输出相同时,将输出相反的值;若其中一个输入的值发生变化,输出将保持不变。施密特触发器也和C单元一样,具有错误过滤能力[5],如图2中(b)(d)所示。但它只有一个输入,当其输入节点翻转时,会将其延迟传输到输出节点。也就是说,如果能快速将输入节点值恢复,就不会影响输出节点的值。

当CLK=1且NCK=0时,锁存器工作在透明模式,并且传输门中的所有晶体管导通,同时ST2、ST4、C3关闭,输入数据传输到N1、N3、Q节点,虽然施密特触发器可以延迟数据传输,但由于透明期时间长于延迟时间,于是数据可以正确传输到N2、N4节点,从而数据传输到所有内部节点。当CLK=1且NCK=0时,锁存器工作在锁存模式,所有传输门关闭,ST2、ST4、C3打开,N1、N3、Q节点的值也分别由ST2、ST4、C3控制刷新。

2 容错原理和仿真实验

本研究设计的锁存器可以实现任意情况的SUN、DNU、TNU完全容忍。下面将讨论锁存模式下锁存器遭受错误时的容忍原理。

2.1 SNU

SNU:假设电路中只有1个节点发生错误。此时可以分为2种情况。

情况1:错误发生在自恢复模块中。以N1翻转为例,此时ST1和C1将错误拦截,N2和N4的值不会发生改变,同时由于N2数据正常,可以通过ST2将N1恢复。

情况2:错误发生在过滤模块中。以N6b翻转为例,此时C3将错误拦截,由于N6数据正常,可以通过反相器将N6b恢复。综上所述,锁存器可以实现SNU的容忍。

2.2 DNU

DNU:假设电路中有2个节点发生了翻转,此时可以分为以下3种情况。

情况1:2个错误都发生在错误拦截模块中。以N5和N6发生翻转为例,错误逻辑值通过反相器和C3传播,将N6b和Q翻转,此时由于自恢复模块中的N1、N2、N3、N4逻辑值正常,所以N5和N6可以通过C1和C2恢复,之后N6b和Q也将被反相器恢复。

情况2:1个错误发生在自恢复模块中,1个错误发生在错误拦截模块中。以N1、N6为例,此时N6b翻转,然后ST1、C1、C2将错误拦截,由于N2、N4逻辑值正常,所以N1和N6将会分别被ST2和C2恢复,之后N6b也将被反相器恢复。

情况3:2个错误都发生在自恢复模块中。以N1、N2翻转为例,此时错误会被C1和C2拦截,其他节点将不会发生错误,Q节点将保持正确逻辑值,N1和N2将在下个透明期恢复。综上所述,锁存器可以实现DNU的容忍。

2.3 TNU

TNU:假设电路中有3个节点发生了翻转,此时可以分为以下4种情况。

情况1:3个错误都发生在错误拦截模块中。以N5、N6、Q发生翻转为例,这种情况与DNU中的情况1类似,此时N6b会被翻转,由于此时自恢复模块中的N1、N2、N3、N4逻辑值正常,所以N5和N6将可以通过C1和C2恢复,之后N6b和Q也将被反相器恢复。

情况2:1个错误发生在自恢复模块中,2个错误发生在错误拦截模块中。以N1、N5、N6发生翻转为例,此时N6b和Q会被翻转,接下来的过程与DNU中的情况2类似,由于N2、N3、N4正常,N2会通过ST2将N1恢复,然后N1、N2、N3、N4会通过C1和C2将N5和N6恢复,之后N6b和Q也将被反相器恢复。

情况3:2个错误发生在自恢复模块中,1个错误发生在错误拦截模块中。以N1、N3、N6发生翻转为例,此时N1和N3会通过C1将N5翻转,N6将N6b翻转,N5和N6b会将Q翻转。由于N2和N4逻辑值正确,N1和N3将会被ST2和ST4恢复,然后N1、N3、N2、N4会通过C1和C2将N5和N6恢复,之后N6b和Q也都将被反相器恢复。

情况4:3个错误都发生在自恢复模块中。以N1、N2、N3发生翻转为例,这种情况类似DNU中的情况3,N1和N3通过C1将N5翻转,由于N4正常,C2将会拦截错误,N6和N6b也保持正常,于是C3也会拦截错误,不会影响Q的逻辑值。综上所述,锁存器可以实现TNU的完全容忍。

2.4 仿真实验

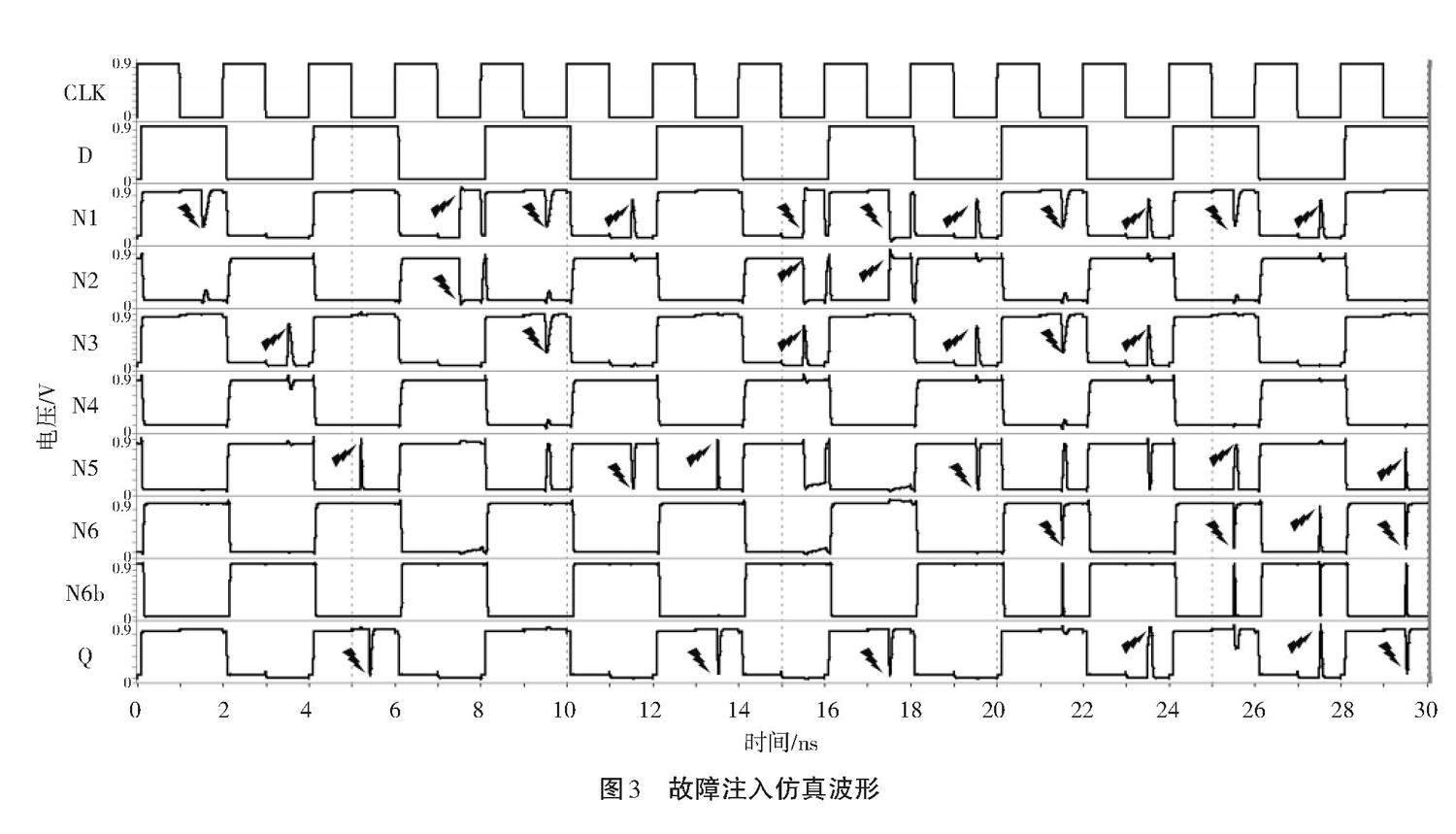

仿真实验使用预测技术模型(PTM)32纳米CMOS技术和Synopsys HSPICE工具进行模拟。电源电压为0.9 V、温度为27 ℃、时钟周期设置为4 000 ps、占空比为50%、PMOS的W/L为2/1、NMOS的W/L为1/1,模拟故障注入的仿真波形如图3所示。

其中,0~6 ns为SNU模拟,分别模拟N1、N3、N5、Q发生错误的情况,从波形图可以看出,它们都可以迅速从错误中恢复,因此锁存器可以容忍SNU。

6~14 ns为DNU模拟,分别模拟(N1,N2)、(N1,N3)、(N1,N5)、(N5,Q)发生错误的情况,从波形图可以看出(N1,N2)发生错误时N1、N2节点不能恢复,但输出节点Q保持正常,所以这种情况不会影响输出。除此之外其他节点组在发生错误后也均能快速恢复,因此锁存器可以容忍DNU。

14~30 ns为TNU模拟,分别模拟(N1,N2,N3)、(N1,N2,Q)、(N1,N3,N5)、(N1,N3,N6)、(N1,N3,Q)、(N1,N5,N6)、(N1,N6,Q)、(N5,N6,Q)发生错误的情况,从波形图可以看出,当(N1,N2,N3)、(N1,N2,Q)发生错误时,N1、N2、N5等节点会无法恢复,但都不会影响最终的输出节点Q,而其他的节点组也都可以在极短的时间内恢复正确的逻辑值。因此锁存器可以容忍TNU。综上所述,本研究设计的锁存器对所有的SNU,DNU,TNU均具有完全的容忍能力。

3 性能与开销对比

将本研究设计的锁存器与其他相关锁存器SHLR[6]、DNCS[7]、DNURL[8]、NTHLTCH[4]、TNUHL[1]、DICE4TNU[9]、LCTNURL[10]进行全面对比,包括容忍能力、功耗、延迟、面积、功耗延迟积。所有锁存器均使用PTM32纳米CMOS工艺,实验条件均与本次试验相同,对比结果见表1。

SHLR为SNU容忍锁存器,DNCS、DNURL、NTHLTCH为DNU容忍锁存器。由表1可知,与其他锁存器相比,本研究设计的LTNTL锁存器由于使用了更多的元件以构建错误过滤结构,所以略微增加了功耗和面积,但提高了容忍能力,同时降低了传输延迟和PDP。LTNTL锁存器的延迟仅略低于DICE4TNU锁存器,并拥有最低的PDP。

与TNUHL、DICE4TNU、LCTNURL这三个TNU容忍锁存器对比结果见表2。本研究设计的锁存器在保持容忍能力的前提下,功耗、延迟、面积、PDP分别降低了37.58%、41.25%、27.77%、75.83%。

4 结语

随着半导体工艺的发展,由高能粒子撞击引起的TNU变得更加严重。许多现有锁存器对TNU没有抗性或者自身开销较大。针对这些问题,本研究设计了一种高性能、低功耗的LTNTL锁存器。该设计结合了施密特触发器、时钟门控技术、高速传输路径,在降低功耗、延迟、面积的同时具有较高的可靠性。HSPICE仿真结果表明了该锁存器的TNU容忍能力,与现有的抗辐射锁存器相比,该锁存器的功耗、延迟、面积、PDP分别降低了37.58%、41.25%、27.77%、75.83%。

参考文献:

[1]WATKINS A,TRAGOUDAS S. Radiation hardened latch designs for double and triple node upsets[J]. IEEE Transactions on Emerging Topics in Computing,2017,8(3):616-626.

[2]EBARA M,YAMADA K,KOJIMA K,et al. Process dependence of soft errors induced by alpha particle,heavy ions,and high energy neutrons on flip flops in FDSOI[J].IEEE Journal of the Electron Devices Society,2019,7:817-824.

[3]BLACK J D,DODD P E,WARREN K M. Physics of multiple-node charge collection and impacts on single-event characterization and soft error rate prediction[J]. IEEE Transactions on Nuclear Science,2013,60(3P2):1836-1851.

[4]LI Y Q,WANG H B,YAO S Y,et al. Double node upsets hardened latch circuits[J]. Journal of Electronic Testing,2015,31(5-6): 537-548.

[5]MOGHADDAM M,MOAIYERI M H,ESHGHI M.Design and evaluation of an efficient schmitt trigger-based hardened latch in CNTFET technology[J]. IEEE Transactions on Device and Materials Reliability,2017,17(1):267-277.

[6]KUMAR S, MUKHERJEE A. A self-healing, high performance and low-cost radiation hardened latch design[C]//2021 IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT).IEEE,2021.

[7]KATSAROU K,TSIATOUHAS Y. Soft error interception latch:double node charge sharing seu tolerant design[J].Electronics Letters,2015,51(4):330-332.

[8]YAN A, HUANG Z F, YI M X,et al. Double-node-upset-resilient latch design for nanoscale coms technology[J].IEEE Transactions on Very Large Scale Integration (VLSI) Systems,2017,25(6):1978-1982.

[9]LIN D P,XU Y R,LI X Y,et al.A novel self-recoverable and triple nodes upset resilience DICE latch[J].IEICE Electronics Express,2018,15(19):20180753-20180753.

[10]NAN H, CHOI K. High performance,low cost,and robust soft error tolerant latch designs for nanoscale cmos technology[J]. Circuits and Systems I:Regular Papers,IEEE Transation on,2012,59(7):1445-1457.

收稿日期:2023-10-27

作者简介:秦学伟(1999—),男,硕士生,研究方向:集成电路可靠性设计。