一种过流与过压保护电路的设计方法

曹洪彬,汪澜,刘红波,马野,王子楠

(1.天津七一二通信广播股份有限公司,天津 300462;2.空军装备部驻北京地区军事代表局驻天津地区第一军事代表室,天津 300202)

引言

随着信息技术的不断发展和电子技术的广泛应用,现在战机不断引入先进的电子设备,超短波电台[1]由于其稳定的信号传输、较高的通信质量,使其在军事领域中广泛应用。电源设计成为机载电台中的重要部分,为防止负载故障导致的短路及过流问题,电源设计需进行相应的保护措施,传统的方案是安装保险丝或空气断路器,这种方法虽然简单,但损坏后无法自动恢复,需维修更换器件,造成硬件成本和时间的浪费。因此对机载电台负载设备供电电流电压实现可恢复保护已成为迫切问题。本文以机载电台电源为硬件平台,提出了一种基于霍尔芯片过流保护[2]和过压保护[3]方案。经试验验证,该方案能够准确地按照设定值进行过流过压保护。同时,该方案具有良好的通用性和可移植性,能够为同类设备的设计提供参考。

1 整体设计

1.1 电路框架设计

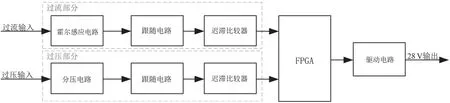

过流过压保护电路框架设计如图1 所示。过流情况为电流信号输入至霍尔感应电路,将电流信号转换为对应的电压信号,电压信号经一级跟随电路进入迟滞比较器[4]电路,前级电流增大,感应出的电压信号对应增大,超出迟滞比较器的基准电压时,迟滞比较器输出端由低变高,输出信号进入FPGA。过压情况为电压信号输入至前级分压电路,将输入电压信号降至有效电压信号,有效电压信号经一级跟随电路进入迟滞比较器电路,前级电压信号增大,超出迟滞比较器的基准电压时,迟滞比较器输出端由低变高,输出信号进入FPGA。FPGA 检测到过流或过压信号,执行控制驱动电路逻辑,实现切断28 V 输出。

图1 过流过压保护电路框架设计框图

2 实现方案

2.1 硬件原理分析

过流电路设计部分,本文核心器件选用某研究所高性能霍尔效应电流传感器。其对应原理如图2 霍尔感应电路部分,能够有效地测量直流或交流电流,并具有精度高、出色的线性度和温度稳定性等特点。此芯片内部集成了一颗高精度、低噪声的线性霍尔电路和一根低阻抗的主流导线,输入电流流经内部的0.6 mΩ 导线,其产生的磁场在霍尔电路上感应出相应的电信号,经过内部处理电路输出电压信号。在无电流的情况下,静态输出为50 %VCC。此芯片提供SOP16 封装,提供更加灵活的应用模式测量范围,10 A,20 A,30 A,40 A,50 A,65 A 多种量程可选。本文以20 A 量程为例,灵敏度0.1 V/A,本设计霍尔供电电压Vcc 为5 V。

图2 霍尔感应电路原理图

1)感应电压计算公式:

式中:

Vout—霍尔感应输出电压,单位为V;

Iin—流经霍尔传感器电流,单位为A。

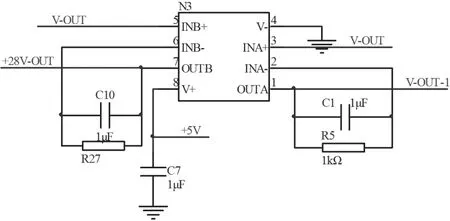

跟随电路设计部分,霍尔感应电路感应电压V-OUT输出至后级跟随电路,其原理如图3 所示,跟随电路增强了输入信号的稳定性,在输出信号摆动时,防止信号漂移,起缓冲作用。

图3 跟随电路原理图

跟随电路输出信号V-OUT-1 至迟滞比较器。

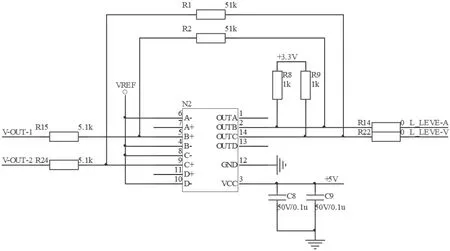

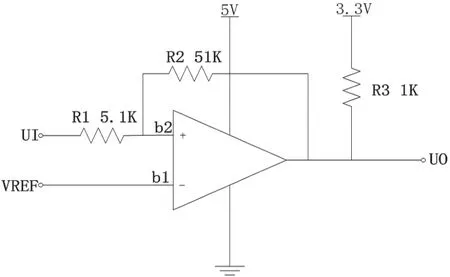

迟滞比较器电路如图4 所示,等效电路如图5 所示,经迟滞比较器进行比较,当Ub2 电压大于Ub1 时,迟滞比较器输出电平由低变高。迟滞比较器计算公式为:

图4 迟滞比较器电路原理

图5 迟滞比较器等效电路

2)当输出为高电平时,UO=3.3 V。

3)当输出为低电平时,UO=0 V。

因为输出上拉电阻,为减小上拉电阻对迟滞比较器的影响,这里选择为1 k,迟滞比较器输出的两种状态位高电平3.3 V,低电平0 V,基准电压选择为3.23 V,与分别为输入过电流经霍尔感应出的电压值,考虑实际情况,机载电台在发射状态下额定电流为6 A,过流设计一般为额定电流的1.2 倍至2 倍,根据实际应用情况而定。本设计过流点选择为10 A,迟滞点选择为7 A,分别对应3.5 V 与3.2 V 两个电压值。一种情况,输出电压为低时,点电位通过电阻拉低,输入的电压需更大,使大于,来驱动输出翻转至高。另一种情况,输出电压为高时,点电位通过电阻拉高,输入的电压需更小,使小于,来驱动输出翻转至低。通过以上分析可知,可选择3.5 V,可选择3.2 V,反之代入方程(2)方程(3),方程无解。

假定为51 k,为1 k,等于基准电压3.23 V,Ui2为3.5 V,代入公式(3),可得出R1 为4.26 k。考虑实际情况,电阻实际应用选择为5.1 k,代入方程(2)方程(3),反推出为3.228 V,反推出为3.553 V,代入公式(1)可推出过流点位10.53 A,滞回点电流为7.28 A。

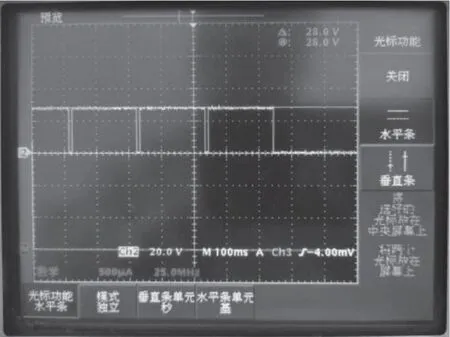

本设计采用迟滞比较器[6],避免了在临界值时直接比较输出抖动问题。输出抖动会导致FPGA 误报,无法判断是否真正过流。实际应用见图6、图7 所示。图6为直接比较输出,可见在临界值时,输出电压出现抖动,不稳定。图7 为迟滞比较器输出,可见当过流时,比较器输出电压稳定为高电平,方便进入FPGA 进行判断。

图6 直接比较器输出结果

图7 迟滞比较器输出结果

过压电路设计部分,原理同过流,过压电路先进行输入电压分压,分压至后级电路允许范围,进入跟随电路,电压跟随后进入迟滞比较器进行比较,比较输出电平进入FPGA。迟滞比较器电路如图4 所示,选择为51 K,R24 选择为5.1 K,分压电路分压电阻选择为100 K,选择为12 K,经反推输入过压点电压为33.16 V,迟滞电压为30.12 V。理论计算值符合设计要求。

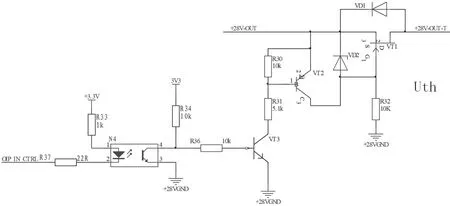

驱动电路设计部分,如图8 所示。当FPGA 检测到过流[5]过压信号时,输出控制OIP_IN_CTRL 信号为高电平,光耦截止,此时由于光耦输出上拉3.3 V,三极管(位号:VT3)导通,三极管(位号:VT2)导通,此时Uth 点电平为28 V,MOS 管(位号:VT1)截止,28 V 无输出。反之,OIP_IN_CTRL 信号为低电平,光耦导通,三极管(位号:VT3)截止,三极管(位号:VT2)截止,由稳压二极管(位号:VD2)将Uth 点电压稳压至15 V,此时MOS 管(位号:VT1)栅极(G)与源级(S)导通,MOS 管(位号:VT1)导通,输出28 V。

图8 驱动电路原理

2.2 软件原理设计

本设计采用FPGA 为主控芯片,实时监测过压过流信号,当过压过流信号由低变高时,执行过流过压程序。过流情况为FPGA 监测过流信号,线路中过流关断,尝试3 次恢复打开,避免线路中误过流导致供电中断,3 次打开后仍过流,则执行关断指令,等待外部触发清除过流计数器,方能再次打开。过流流程图如图9 所示,在第一次过流计数器加1 时,关断并打开判断是否过流,若过流则计数器再加1,否则计数器清零,计数器计满3 次,仍过流则执行关断。本设计中一次过流关断再打开设置为10 ms,过流检测设置为200 ms。

图9 过流保护流程图

图10 过压保护流程图

过压情况为FPGA 监测过压信号,当线路中过压时,延迟200 ms 检测,线路中仍过压,则执行关断指令。等待外部触发清除过流计数器,方能再次打开。过压保护无需进行关断打开恢复操作,因无论关断或打开,前级电路中过压都存在于线路中,则只需检测一定时间,本文设计为200 ms,确认过压直接执行关断执行,防止后端负载因过压而损坏。

3 仿真验证及实物测试

3.1 仿真试验及波形结果

本设计跟随器与迟滞比较器部分采用了PSpice 软件进行仿真,仿真电路如图11 所示,仿真波形如图12 所示。

图11 跟随与迟滞比较仿真电路

图12 跟随与迟滞比较仿真电路

红色波形代表输入信号,绿色波形代表迟滞比较器输出信号,由仿真波形可见,当输入电压达到3.55 V 时,迟滞比较器输出信号由低变高。当输入信号降至3.23 V时,迟滞比较器输出信号由高变低。仿真电压值与2.1硬件原理分析章节理论计算值一致。

3.2 实物测试及波形结果

3.2.1 过流试验

经实际过流试验验证,当实际电流达到10.5 A 时,输出关断。实际关断波形如图13 所示。由图13 可见,当FPGA 检测到过流信号时,输出关断延迟10 ms 并打开,检测200 ms,此动作重复3 次,仍然检测到过流信号时,执行关断指令,不再打开。等待外部触发消除过流计数器,方能再次打开,否则会一直执行关断指令。

图13 过流试验输出电压波形

实际测试过流迟滞区间试验,电子负载调整至过流,然后进行电流回调,当回调至7.23 A 时,迟滞比较器过流信号由高变低。由此验证迟滞区间是(7.23~10.5)A,当线路中电流大于10.5 A 时,执行过流保护动作。迟滞比较器主要作用是进行临界消抖,在实际使用过程中,回滞电压点设置应满足不小于实际额定电流对应的电压,这样在线路中电流恢复至额定电流时,保证FPGA 检测到的过流信号为低电平,执行正常开通动作。实际测试回滞电流值与理论计算有一定差异,具体应由电路容差所致,本文不做详细说明。

3.2.2 过压试验

经实际过压试验验证,当实际电压达到33 V 时,输出关断。实际关断波形如图14 所示。由图14 可见,蓝色波形为28 V 输出电压,紫色波形为迟滞比较器输出电平,当FPGA 检测到过压信号时,输出关断延迟200 ms,执行关断指令,不再打开。等待外部触发消除过压计数器,方能再次打开,否则会一直执行关断指令。

图14 过压试验输出电压波形

实际测试过压迟滞区间试验,将供电电源调整至过压状态,然后进行电压回调,当回调至30 V 时,迟滞比较器过压信号由高变低。由此验证迟滞区间是(30~33) V,当电压大于33 V 时,执行过压保护动作。迟滞比较器主要作用是进行临界消抖,在实际使用过程中,回滞电压点设置应满足不小于实际额定输入电压,这样在电压恢复至额定电压时,保证FPGA 检测到的过压信号为低电平,执行正常开通动作。

4 结束语

本文主要实现了一种过流与过压保护电路的设计方案,替代了传统保护方式,具有自恢复功能,有效地护了因电路中过压过流导致的损坏,提高了电路的可靠性,且该设计采用全国产化器件,并进行了高低温试验验证,满足使用要求,已在机载电台电源设计中应用,具有一定实际应用和参考价值。