JFET 构成的运算放大器输入过压保护电路设计

熊凌霄,王 靖,胡程源,李 威

(电子科技大学集成电路科学与工程学院,成都 611731)

1 引言

随着集成电路产业的快速发展,电路系统结构的复杂性不断增加,对模拟集成电路系统中不可或缺的运算放大器的性能要求也在不断提高[1]。而在运算放大器的应用场景中,难免出现输入端电压过大导致运算放大器遭到损伤的情况。一旦运算放大器的输入电压超过电源电压或者规定的输入共模电压范围,其输入端非常容易产生大电流,从而破坏电路[2]。因此,运算放大器中的输入过压保护电路的作用是当输入电压过大时对产生的过压电流进行限制。传统且最常见的过压保护方法是添加输入端口到正负电源的钳位二极管以及一个限流电阻,以防止输入电流的急剧上升[3]。然而此方法同时也会引入额外的噪声,且降低运放整体的共模抑制比[4]。针对上述问题,设计一种主要由JFET 以及钳位二极管组成的运算放大器输入过压保护电路。

2 传统过压保护电路结构缺陷

传统运放的输入过压保护电路结构如图1 所示。该结构由限流电阻RIN以及两个钳位二极管组成。电路在进行过压保护时,电阻电流与输入电压几乎呈线性关系,并不能很好地限制过压电流的大小。虽然设计者可以通过加大电阻阻值来得到更好的限流效果,但这无疑会引入更大的电阻热噪声,从而影响运放的精度[5]。

图1 传统过压保护电路

此外,由于正常输入时,钳位二极管都会存在一定漏电流,一旦连接到正负电源的钳位二极管漏电流不相等,其差值流过限流电阻产生的压降将表现为失调电压,进一步降低运算放大器的性能。

3 新设计结构及原理

相对于传统过压保护电路存在的缺陷,新设计具有结构简单、限流能力强的特点,能够限制过压电流的大小,使其饱和,且在正负过压情况下饱和过压电流的大小一致。

3.1 电路结构

新设计的运算放大器输入过压保护电路结构如图2 所示,图中只给出同相输入端的过压保护电路。定义VIN为运算放大器AMP 的输入过压保护电路的输入端口IN 的电压,VOUT为被保护运算放大器AMP 的输入端口IO 的电压。保护电路能在VIN超过电源电压范围时限制住端口IO 流入或者流出的电流的大小。

图2 新设计电路同相输入端保护电路

整个电路包括三个P 沟道JFET 以及两个钳位二极管。假设三个P 沟道JFET 的沟道夹断电压都等于VT,且钳位二极管的导通电压都等于VON。

在输入端口电压处于AMP 正常输入范围内时,VIN直接通过J1的漏源极传输到AMP 的输入端口IO。为了减少过压保护电路带来的噪声影响,J1具有极高的宽长比,使得J1导通电阻非常低[6],VIN几乎可以无损地传输到VOUT。相反,J2和J3的宽长比相等且极小,因此J2以及J3的导通电阻极大。

3.2 过压保护机制

当输入端口电压高于正电源电压值与D1正向导通电压值之和时,为正向过压情况,过压保护机制启动。当VIN高于该临界值后,D1导通,形成从IN 端口到正电源的电流通路。

如图3 所示为正向过压情况下的过压电流示意图。此时整个过压电流有两条路径。图中I1表示正向过压下过压电流的正向第一电流组成部分,从IN开始,经过J1的漏源极,再经过D1到正电源。图中I2表示正向过压下过压电流的正向第二电流组成部分,从IN 开始,经过的J2源漏极和J3的源漏极,再经过D1到正电源。

图3 正向过压时过压电流的组成

在正向过压状态下,由于三个P 沟道JFET 的栅极各自相连,且没有其他电流通路,故三个JFET的栅极都不可能产生寄生二极管的导通电流。因此,栅极电压会始终跟随VIN、VOUT两者中的较大者,即:

此时,VOUT在钳位二极管的作用下,电压固定在:

栅极电压与VOUT压差足够大之后,将造成J1以及J3沟道夹断,进而使得整个过压电流达到饱和[7]。此时J1的电流即正向第一电流组成部分的大小为[8]:

而J3夹断之后也会限制J2的电流,故正向第二电流组成部分的大小为:

由于J1与J3宽长比的差距,正向第一电流组成部分的大小远大于正向第二电流组成部分的大小。

当输入端口电压低于负电源电压值与D2正向导通电压值之差时,为负向过压情况,过压保护机制也会启动。由于保护电路的对称性,负向过压情况下的过压保护机制与正向一致。

当VIN低于负向过压保护机制启动临界值后,D2导通,形成从IN 端口到负电源的电流通路。如图4所示为负向过压情况下的过压电流示意图。此时整个过压电流也有两条路径:I3表示负向过压下过压电流的负向第一电流组成部分,从负电源开始,经过D2,再经过J1的源漏极到IN;I4表示负向过压下过压电流的负向第二电流组成部分,从负电源开始,经过D2,再经过的J3漏源极和J2的漏源极到IN。

图4 负向过压时过压电流的组成

在负向过压状态下,三个P 沟道JFET 的栅极也不可能产生电流。栅极电压依然跟随VIN、VOUT两者中的较大者,即:

负向过压时,VOUT在钳位二极管的作用下,电压固定在:

当VIN电压足够低之后,栅极电压与VIN压差过大,将造成J1以及J2沟道夹断,进而使得整个过压电流达到饱和。此时J1的电流亦即负向第一电流组成部分的大小为:

而J2夹断之后也会限制J3的电流,故负向第二电流组成部分的大小为:

由于J1与J2宽长比的差距,负向第一电流组成部分的大小远大于负向第二电流组成部分的大小。

I1和I3都是J1沟道夹断后的饱和电流,且在正负过压的VIN绝对值相等的情况下,正向过压时J1的栅源电压等于负向过压时J1的栅漏电压,亦即I1与I3大小相等:

I2、I4分别为J3、J2沟道夹断后的饱和电流,且在正负过压的输入端口电压绝对值相等的情况下,正向过压时J3的栅漏电压等于负向过压时J2的栅源电压,亦即I2与I4大小相等:

因此在正负过压的输入端口电压绝对值相等的情况下,过压电流大小相等,方向相反,即正负过压情况下的过压电流具有对称性。

4 仿真结果与分析

基于4μm 双极工艺,使用Cadence 软件搭建电路,对所设计运算放大器的输入过压保护电路进行仿真。首先将输入过压保护电路拿出运算放大器,进行单独仿真,读取其白噪声结果并与传统的不同阻值电阻加钳位二极管的输入过压保护电路的噪声结果进行对比。仿真对比结果如表1 所示。

表1 新旧结构噪声对比

结果表明,通过合理选取J1的宽长比,新结构能够得到与传统过压保护结构相当甚至更低的噪声。J1宽长比尺寸也直接关系其导通电阻以及饱和过压电流的值,宽长比越大导通电阻与噪声越小,过压饱和电流的值也将越大。

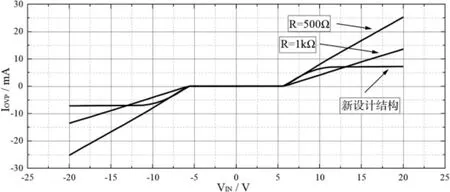

在此基础上对电路的保护能力进行仿真。取电源电压为±5V 双电源,对输入电压在±20V 之间进行扫描,读取IN 端口的过压电流,并以不同阻值电阻加钳位二极管过压保护电路的IN 端口的过压电流为对照。得到仿真结果如图5 所示。

图5 过压电流随VIN 变化曲线

结果显示,新设计电路结构能够有效抑制过压电流并使之饱和,而传统的电阻加钳位二极管过压保护电路的过压电流会一直随输入电压增大而增大,且在高输入电压时过压电流将非常大。

以同样的仿真条件,读取J1的漏端电流以及J2、J3的源端电流,结果如图6、图7、图8 所示。

图6 J1 漏端电流随VIN 变化曲线

图7 J2 源端电流随VIN 变化曲线

图8 J3 源端电流随VIN 变化曲线

仿真结果显示,由于J1极大宽长比与J2、J3极小宽长比之间的差距,无论正过压还是负过压情况下,J1的饱和电流始终远高于J2、J3。而J2、与J3的电流始终保持一致,且正负过压情况下三个JFET 的各自电流具有高度对称性,与理论分析完全相符。

5 结束语

采用JFET 器件设计的运算放大器的输入过压保护电路相较于传统过压保护电路而言,过压电流更低,且所设计电路利用JFET 沟道夹断的原理有效限制了过压保护电流的增长并使之饱和,能够在相等甚至更低的噪声的条件下极大提升电路的过压保护能力。设计时需要在饱和电流值和噪声之间折中,这主要取决于J1管的宽长比大小。通过仿真结果可以得到,该电路功能正确,满足设计要求。