基于ATE测试平台Chroma 3380D的多管脚芯片FT测试系统的设计研究

田 磊

(1.珠海零边界集成电路有限公司 珠海 519070;2.珠海格力电器股份有限公司 珠海 519070)

引言

ATE芯片测试是指自动测试设备(Automatic Test Equipment,ATE)对芯片进行测试的方法。随着集成电路技术的不断发展,芯片的规模和复杂性不断增加,ATE芯片测试技术也得到了广泛的研究和应用。

目前,学者们已经取得了一些关于ATE芯片测试的研究成果。其中,一些重要的研究包括:①测试算法研究:针对不同类型的芯片,研究高效的测试算法是ATE芯片测试的核心问题之一。例如,边界扫描测试、内建自测、测试压缩等算法,这些算法可以提高测试效率、降低测试成本。②测试结构设计:为了能够准确地检测芯片的故障,需要设计合理的测试结构。学者们研究了一些新的测试结构,如扫描链、测试矢量生成器等,以增强ATE芯片测试的可靠性和效率。③故障诊断与识别:故障诊断和识别是ATE芯片测试的重要环节,通过研究故障模式和影响分析(Fault-Propagation Analysis)、故障模拟和仿真等技术,可以有效地识别和定位芯片中的故障。④测试性分析与评估:通过对芯片进行测试性分析和评估,可以确定ATE芯片测试的覆盖率和可靠性。学者们研究了一些新的测试性分析和评估方法,以优化ATE芯片测试的过程。

但这些已有的研究主要是集中在针对某一个测试项目的如何优化,未能从整体上对芯片FT测试的流程方法进行阐述。本文针对一款空调外机芯片,该芯片管脚众多,受限于ATE测试平台Chroma 3380测试通道数量有限,笔者提出一种针对于多管脚芯片在FT测试平台的通道分配的硬件设计方案及测试流程。该测试方案实现了对该芯片的主要功能与性能参数测试,能够作为通用测试方法供相关测试研发人员参考。

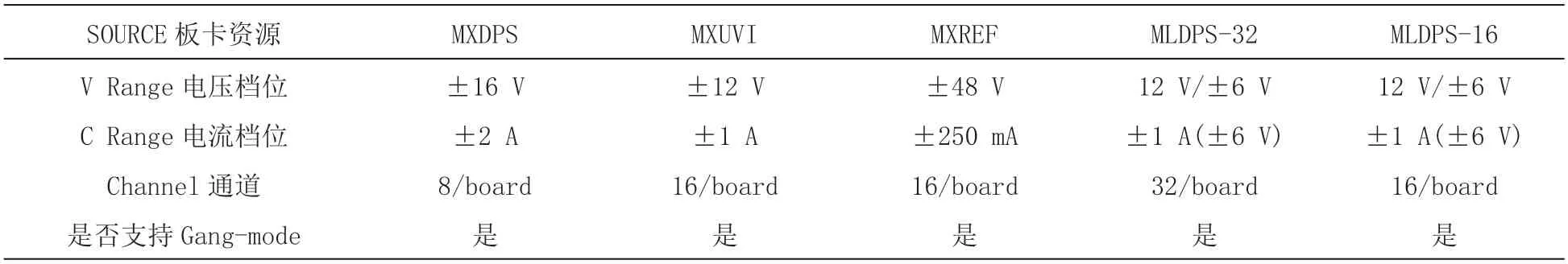

表1 板卡资源能力

1 Chroma 3380D 系统资源配置

1.1 Chroma 3380D 简介

Chroma 3380D 自动化测试系统基于Windows 7操作系统环境,基于CRAFT C/C++ 编程语言。整个测试系统采用弹性化硬件结构,多样弹性VI电源,可根据测试需求选配不同的测试板卡,整个设计小型化、低功耗化,是功能强大、使用经济的自动化测试系统,可满足多种形式的集成电路测试用途。

1.2 Chroma 3380D测试资源

Chroma 3380D测试系统可通过灵活配置测试板卡来满足测试要求。系统可配置 MLDPS、MXREF、MXUVI、MXDPS、MXPMU、PPMU等板卡,支持gang-mode 模式满足更高的测试要求,板卡资源电流电压能力如表 1 示。

2 测试系统配置

2.1 测试系统配置

本次是基于一款32位ARM Cortex-M0内核微处理器的空调外机芯片,针对该空调外机芯片的测试要求给出所需的FT测试项目。整个FT测试系统由3380D(tester)测试机、DIB(Device Interface Board)测试所用的PCB板卡、Load Board(测试负载板)组成,不同package使用不同Load Board测试。FT测试系统基于Chroma的3380D平台开发,测试时采用4sites方式测试,以提高产能、降低测试成本。硬件上配备4片MXLPC BOARD、1片MLDPS-16(或MLDPS-32)、1片MXPG3、1片MXPMU、1片MXBUS,以提供256Channels(64CHBoard)、256PPMU(64PPMUBoard)、16DPS(16DPSBoard)、16PMU(16PMUBoard)。

3 芯片规格

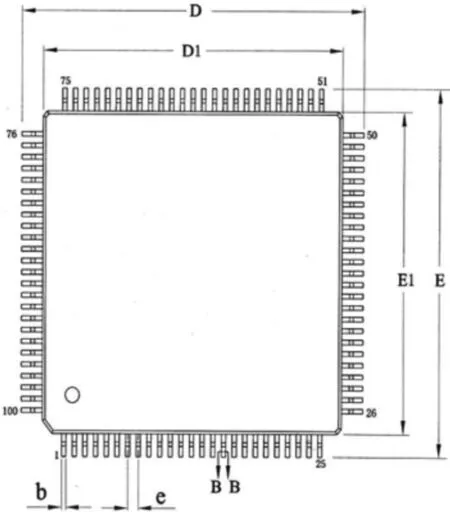

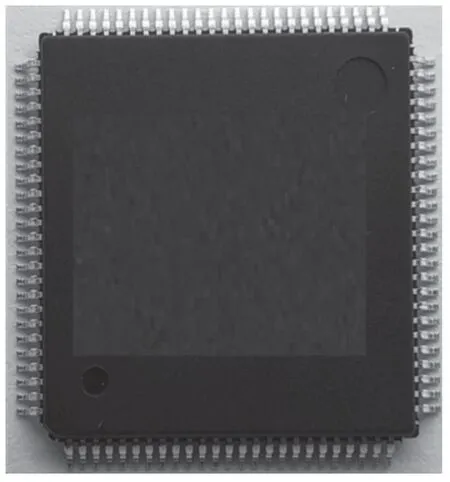

本次基于的外机空调芯片是一款100个管脚的芯片,如图1、2所示。

图1 芯片管脚图

图2 芯片实物照片

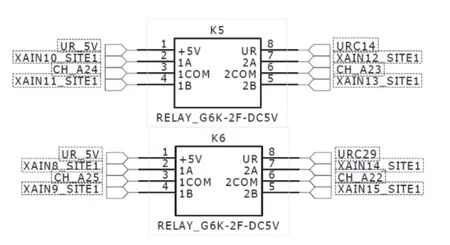

Chroma 3380D的通道仅有64个,每颗芯片只能占用测试机64个通道。为实现4-site并测要求,笔者采用欧姆龙干簧式继电器来进行通道分时切换,如图3所示。当Relay off(继电器关闭)状态下,XAIN10_SITE1引脚与XAIN12_SITE1引脚相连通,当Relay on(继电器闭合)状态下,XAIN11_SITE1引脚与XAIN13_SITE1引脚相连通,通过此方法来做到芯片管脚的分时复用,将芯片100个管脚的测试资源分配到Chroma 3380D测试机的64个通道中。

图3 继电器切换原理图

关于继电器的开关和闭合的指令,可参考Chroma3380D用户手册10,有UR(User Relay)针对用户继电器的开关设置,如表2示[6,7]。

4 芯片测试项目

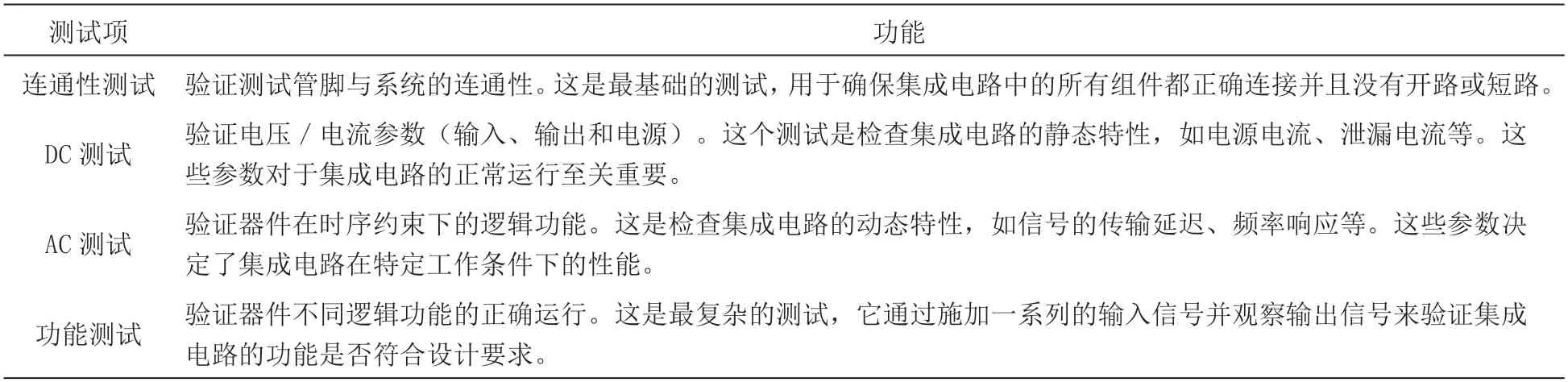

集成电路的测试是非常重要的环节,它确保了器件的性能和可靠性。数字集成电路测试项主要包含连通性测试、直流参数测试、交流参数测试以及功能测试四个部分[2-5],如表3所示。

表3 数字集成电路测试的测试项

通过这些测试,可以确保集成电路的质量和可靠性,从而保证其在最终产品中的应用能够正常工作。

4.1 测试项目

1)开路与短路测试(Open/Short test),也称为连续性测试(Continuity test),其用于测试芯片与ATE测试机资源的连通性是否完好。在真正的芯片测试流程开始之前,我们通常需要确认芯片与测试机的连接是否正常,如果芯片没有放好,做其他测试并无意义。开路与短路测试测试项目,可以用来快速地判断IC芯片是否为良品的一种方法。同时,也可以用来验证测试系统及相关设施是否正常。例如 Probe Card 及 Socket 是否连接正常。连接性测试能快速检测出被测器件(Device Under Test,DUT)是否存在电性物理缺陷,如引脚短路、bond wire缺失、引脚的静电损坏以及制造缺陷等。

2)静态电流测试(IDDQ_Test)。IDDQ是针对晶体管的故障,其主要原理是通过检测CMOS静态漏电流是否有较明显变化来判断电路中是否有短路等故障。IDDQ表示晶体管在静止状态下的漏电流,因为正常的CMOS晶体管静态漏电流IDDQ相比于动态电流很小,故我们可以通过观测静态漏电流变化来完成对芯片的测试筛选。

3)输入脚漏电流(IIL/IIH)测试。输入脚在逻辑 1时的漏电流量称为 Input Leakage in High,简称 IIH。输入脚在逻辑 0 时的漏电流量称为 Input Leakage in Low,简称 IIL。即测试芯片所有IO Pins用作GPI时的漏电流IIL/IIH。测试所有GPI Pins对电源的漏电流IIL、对地的漏电流IIH以及测试相邻PKG相邻管脚间的漏电流。

4)输入脚漏电流(VOH/VOL)测试。VOH(Output Voltage in High),输出脚在逻辑 1 时的最小电压值。IOH(Output Current in High),输出脚在逻辑1时的电流值。测试所有IO Pins用作GPO时的驱动能力。

5)SCAN测试。整个芯片可以看作大量寄存器和寄存器之间的组合逻辑的集合。通过对寄存器插入扫描链(scan chain),根据物理缺陷建立的fault model进行求解,产生结构性测试向量,完成芯片数字逻辑的测试,称为scan测试。

6)Mbist_Test测试。Mbist是memory build-in-self test的缩写,意为存储器内建自测试。“内建”的含义是指针对存储器的测试向量由内建的存储器测试逻辑自动产生,而非外部测试机台(ATE:Auto-Test-Equipment)生成。MBIST 电路将产生测试向量的电路模块以及检测测试结果的比较模块都置于芯片的内部,在测试完成后,将测试的结果通过芯片的测试引脚送出到芯片的外部。MBIST 的核心思想是在芯片内部,存储器外部建立测试电路结构,实现对存储器的读写控制:写入测试向量,读出响应数据。

7)CHECK_CODE_BLANK测试。检测eflash的main page (code) info page(boot rom)区是否已烧写。通过配置待测芯片进入FUNC mode(功能模式),通过SWD读取eflash,检测main page(code区)info page(boot rom区)是否已经烧写。

8)CODE_PROG_VERIFY测试。给eflash的main page info page区烧录code;配置待测芯片进入FUNC mode(功能模式),通过SWD烧写code到EFLASH的mainpage(code区)infopage(bootroom区);

9)GET_TRIM_VALUE测试。检测芯片Trim Value是否已经在CP烧写;获取BandGap_Trim、LDO_Output_Trim、RC1K_Trim、RC8MR_Trim、RC8MC_Trim等信息。

10)CHECK_TRIMMING_RESULT测试。检测执行OPT_BYTES_PROG_VERIFY后的芯片LDO电压及IRC8M输出频率是否满足要求。

11)LVD_Test测试。LVD的功能是检测芯片的低电压比较器功能是否正确。

12)锁相环PLL_6X_Test测试。测试芯片锁相环(PLL_6X)8分频后的输出端频率是否正确。

13)OSC_8M_32K_Test测试。分别测试芯片外挂8 MHz晶振时和的32.768 kHz晶振时的输出端的频率是否正确。

14)ADC_Test模拟数字测试。测试模数的AD转换功能是否正确。

15)DAC_ACMP_Test数字模拟测试。测试DAC模数转换及ACMP电压比较器功能是否正确。

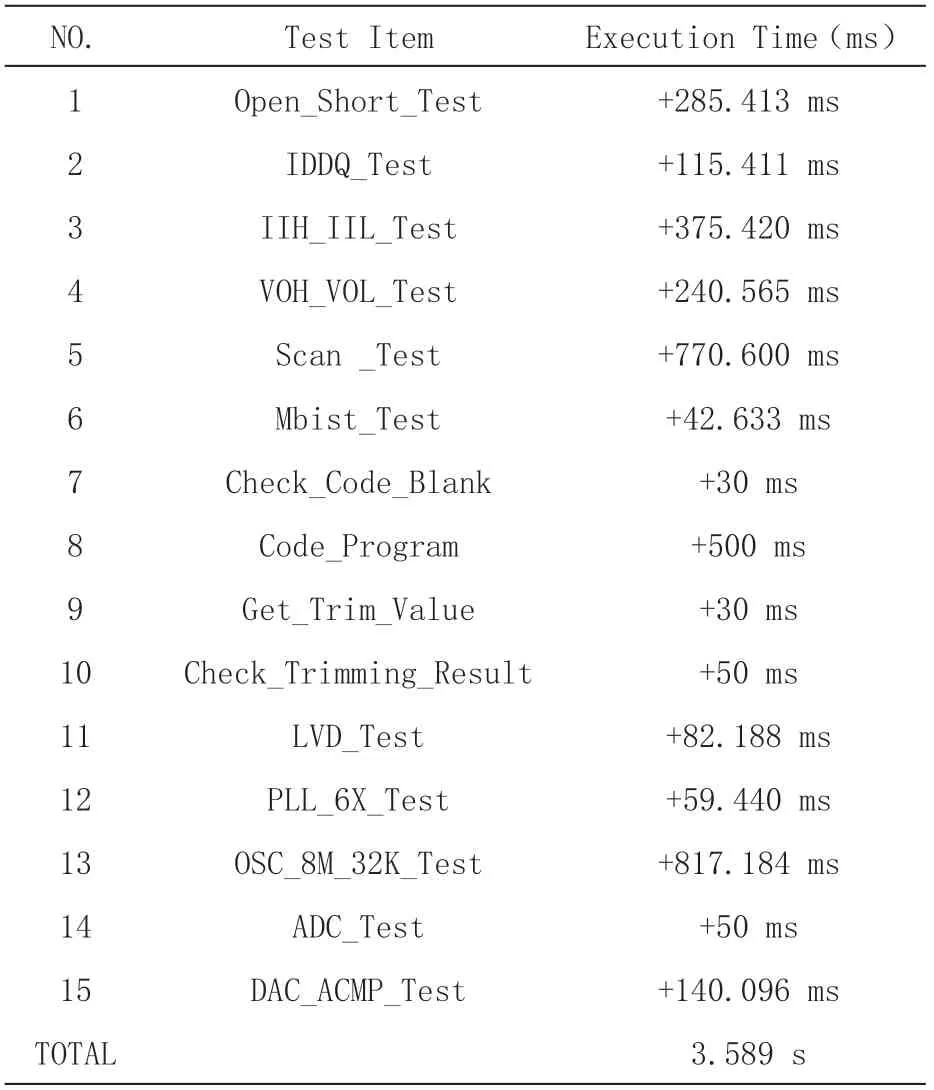

4.2 并测时间

通过调试,芯片测试结果如表4所示。

表4 芯片测试结果

5 结论

为了解决多管脚芯片在FT测试平台中通道数量有限的问题,本文提出了一种硬件设计方案和测试流程。该方案实现了对芯片的主要功能和性能参数的测试,可以作为通用的测试方法供相关测试研发人员参考。

具体而言,该方案包括诸多步骤。分析芯片的管脚数量和功能,确定需要测试的主要功能和性能参数。

根据ATE测试平台的通道数量和芯片的管脚数量,设计合理的通道分配方案。根据通道分配方案,选择适当的测试仪器和测试夹具,搭建测试平台。利用了继电器分时复用的硬件电路设计,构建了一个多通道的测试平台。这一平台可以同时对多个管脚进行测试,大大提高了测试效率。编写测试程序,实现对芯片各个功能的测试,记录测试数据。测试结果会被实时收集并进行分析,以确定芯片是否符合设计要求。

通过这一方案和流程的实施,我们成功地解决了多管脚芯片在FT测试平台中通道数量有限的问题。这不仅提高了测试效率,降低了测试成本,而且为多管脚芯片的可靠性提供了保证。在实际应用中,这一方案和流程已经被广泛应用于各种类型的多管脚芯片测试中,并取得了良好的效果。