RISC-V特权架构配置的硬件实现影响研究

闫 润,黄立波,成元虎,杨 凌,兰孟桥,张 京

(国防科技大学 计算机学院,长沙 410005)

0 引 言

RISC-V指令集架构(Instruction Set Architecture,ISA)[1]是一种新兴的开源精简指令集架构[2].RISC-V采用模块化设计,提供大量自定义编码空间以支持对指令集的扩展,允许开发者根据资源、能耗、权限、实时性等不同需求,基于部分特定的模块和扩展指令集进行精细化的系统设计研发.在内容上包括非特权指令集(Unprivileged ISA)[3]和特权架构(Privileged Architecture)[4]两部分.

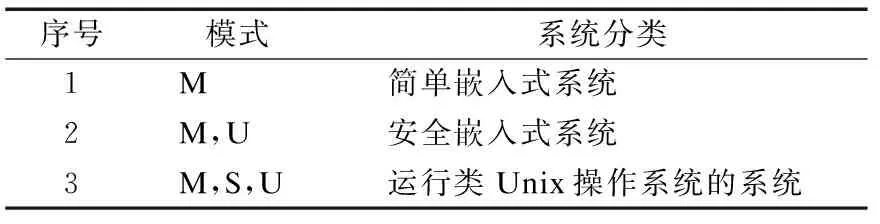

凭借开源和模块化设计的优势,新兴的RISC-V指令集发展迅速.RISC-V指令集架构被定义为一个基础指令集和若干可选扩展指令集的组合,并在一种特权模式下进行工作.根据特权等级和应用场景的不同,RISC-V处理器分为简单嵌入式系统、安全嵌入式系统和运行类Unix操作系统的系统.特权组合和对应系统分类见表1.

表1 特权模式组合Table 1 Supported combinations of privilege modes

简单嵌入式系统对应于特权等级M模式,一般是被设计成用于某一特定功能的处理器,如RV32EC_P2[5]是由IQonIC Work团队研发的一款两级流水线的RISC-V处理器IP,旨在满足运行可信程序的小型低功耗嵌入式应用的需求,采用简单的机器模式特权架构,内存访问方式采用直接物理寻址;国内工程师胡振波开发并开源了蜂鸟E200[6]超低功耗RISC-V处理器核,指令集支持RV32IMAC,两级流水,特权架构采用机器模式,采用直接物理寻址方式.安全嵌入式系统是在简单嵌入式系统的基础上增加了地址保护,用来保证用户应用程序不会对系统造成影响,其中RV32IC_P5[5]是IQonIC Work团队研发的另一款针对中等规模嵌入式系统的RISC-V处理器IP,五级流水线设计,采用机器模式和用户模式特权架构,内存直接物理寻址;Z-scala Core[7]是加州大学伯克利分校研发的一款面向特定嵌入式系统和微控制器应用的32位核,指令集采用RV32IM,三级流水实现,在特权等级上采用机器模式和用户模式.运行类Unix操作系统的处理器支持最多的功能,如伯克利在2016年开发的64位单发射五级流水线顺序处理器Rocket Core[8],具有可配置性,支持多种RISC-V的指令集扩展组合,采用3种特权模式的组合,配备内存管理单元(Memory Management Unit,MMU)以支持类Unix操作系统,在芯片原型上成功运行了Linux操作系统;阿里巴巴公司研发的64位高性能嵌入式RISC-V处理器Xuantie-910[9],指令集支持RV64GCV,采用乱序执行三发射的十二级流水线,特权架构上支持标准的3种模式,采用Sv39的MMU;中国科学院计算技术研究所在RISC-V中国峰会发布的开源高性能RISC-V处理器核“香山”[10],采用十一级流水线6发射的乱序处理设计,配备3种特权等级,支持Sv39的分页机制;SCR7[11]是Syntacore公司推出的64位商用高性能处理器IP,支持3种特权等级,指令集支持RV64GC,可以运行Linux操作系统,对称多处理(Symmetrical Multi-Processing,SMP)每个集群可支持8核.由此可见,在RISC-V处理器设计时,除非特权指令集和体系结构设计的差异,在特权架构上亦有差别,主要体现对物理地址的管理方式上.除此之外,特权架构还包括一些可选实现单元,这些同样会对系统的功能和硬件开销产生一定的影响.

随着近代处理器主频不断提高,能耗开销、系统散热等问题越来越突出,尤其是学术界对多核处理器的关注越来越多[12-14],芯片面积和功耗开销成为设计处理器的一个重要评估因素.Dörflinger等人[15]对开源的应用级RISC-V处理器进行了性能,面积和功耗等方面评估,但缺少对特权架构的详细对比,更多关注于体系结构的差异.国内刘畅等人[16]对RISC-V指令集架构进行了综述.可以看出目前较少研究关注不同RISC-V特权架构配置对硬件实现的影响.此外,广泛的参数化设计体系结构是研究人员孜孜以求的目标,旨在更方便地为特定的应用场景进行设计,通过改变配置,用户可以生成针对不同应用场景的片上系统(System on Chip,SoC).

本文采用开源处理器CVA6[17]进行特权架构配置硬件实现和分析研究,该处理器是由OpenHW团队研发设计的6级流水单发射顺序核,参照RISC-V特权指令集架构规范,在硬件上设计实现了包括RV32和RV64两种位宽的配置,支持3种特权模式和所有的特权指令扩展,设置异常处理委托程序,支持M和S两种模式的异常处理,设置物理内存保护机制对物理地址进行保护,基于页面虚拟内存采用Sv32和Sv39两种方案,实现了较为全面的性能计数器等.CVA6架构框图见图1.本文研究的重点在于读取、存储单元,异常处理单元,性能计数器等.在图1中指令TLB(Translation Lookaside Buffer)、指令存储、数据存储、数据TLB和PTW(Page Table Walker)表示读取、存储单元相关涉及到的硬件资源;异常处理和特权检查表示特权架构中的异常处理;CSR写包括性能计数器和读写其他功能部件等.

图1 CVA6架构示意图Fig.1 Overview architecture of CVA6

本文针对特权架构的可选配置进行硬件实现的探索研究,分为两类共32种可选配置,采用参数化的方式进行配置选择,利用综合工具对各种配置进行硬件资源开销的估算.根据估算结果和处理器功能对各种应用场景提供特权架构的配置推荐.本文的实验结果表明在采用相同指令集和体系结构设计的前提下,不同配置最多可以带来的28.63%面积和40.83%功耗差异.

本文的内容组织如下:第1部分主要描述RISC-V中的32种可选特权架构配置,第2部分是本文的实验结果,包括各类配置的量化结果和应用场景配置推荐,第3部分对全文的内容进行总结.

1 特权架构配置

1.1 RV32与RV64

RV32、RV64是RISC-V中最重要的两种,分别针对32位和64位环境而设计.两种指令集都使用32个通用寄存器(x寄存器)和一个额外的非特权寄存器(pc寄存器),主要的区别在于寄存器的位宽(XLEN),RV32中通用寄存器是32位(XLEN=32),而RV64中通用寄存器是64位(XLEN=64).两种指令集架构位数的选择主要取决于寻址范围的大小和数据运算能力的强弱.

在本文中,分别实现了RV32和RV64两种用来探索不同位宽下特权架构配置的硬件实现影响.

1.2 特权模式

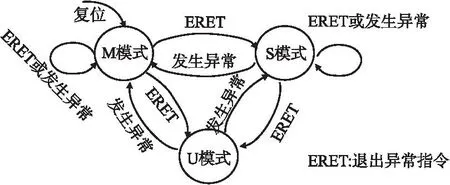

RISC-V特权架构规定,指令集必须工作在一种确定的权限模式下,目前共有以下4种权限模式:机器模式(Machine,M模式)、用户模式(User,U模式)、管理模式(Supervisor,S模式)、监视模式(Hypervisor,H模式).其中H模式是基于S模式的虚拟化扩展,暂处于草案状态,因此在本文中仅关注前3种特权模式.特权模式的设计主要用于在软件栈的不同组件之间提供保护.

M模式是RISC-V指令集架构中最高级别的权限模式,具有执行任何机器操作的权限,也是在系统设计中必须实现的一个工作模式,提供裸机执行环境.U模式是特权架构里最低级别的权限模式,通常用于执行来自用户等外部环境的不可信操作,实现用户和系统之间的隔离.S模式具有比U模式更高的权限,可以设置相应组件来实现操作系统的使用,调度多个应用程序.只有在响应异常或异常返回时才会发生特权级的切换.模式转换图见图2.

图2 不同模式之间转换条件Fig.2 Conversion conditions between different modes

1.3 异常处理机制及扩展

中断和异常机制往往是处理器指令集架构最为复杂和关键的部分.RISC-V定义了一套相对简单的中断和异常机制,同时也允许用户对其进行定制和扩展.在特权架构1.11版本[18]中定义了关于异常处理的N扩展(U模式下的异常处理),在1.12版本中对这部分内容进行了删减.考虑到后续可能对N扩展再次进行调整以及内容的完整性,本文按照1.12草案[19]对N扩展进行实现和硬件实现的评估.

RISC-V使用CSR寄存器来进行记录异常状态以协助异常处理程序进行异常处理.尽管M模式的处理程序可以使用MRET指令将异常重定向到适当的特权级别,但是默认情况下,无论处于何种特权模式下发生异常,控制权都会被移交到M模式的异常处理程序.为了提高性能,RISC-V指令集规范了中断异常委托机制.这个机制可以将异常的处理委托到低级别的特权模式.如果系统支持M/S/U 3种模式,M模式下的medeleg或mideleg寄存器可以将异常委托到S模式或U模式,由S模式下的异常处理程序来处理.如果U模式的异常支持,S模式可以通过sedeleg和sideleg寄存器来将异常委托到U模式,由U模式的异常处理程序来处理.如果系统支持M/U两种模式,并支持U模式的异常处理,设置medeleg或mideleg来将对应的异常委托到U模式,由U模式的异常处理程序处理.

从系统设计来看,以M模式为例,共有8个控制和状态寄存器(CSRs)是M模式异常处理的必要部分,分别为:mtvec(Machine trap-handler base address)、mepc(Machine exception program counter)、mcause(Machine trap Cause)、mie(Machine interrupt-enable register)、mip(Machine interrupt pending)、mtval(Machine bad address or instruction)、mscratch(Machine scratch register)、mstatus(Machine status register)、mstatush(仅RV32),其他两种模式的异常处理对应寄存器与M模式的寄存器设置类似,异常委托机制所需要设置的寄存器为mideleg(Machine interrupt delegation register)和medeleg(Machine exception delegation register).如果仅支持M模式的异常处理则无需设置mideleg和medeleg;当系统中实现M和U两种模式的异常处理时,需要设置对应M模式和U模式两种模式下的异常处理和异常委托所需要的寄存器及其对应的处理逻辑;当系统中同时实现M、S、U 3种模式的异常处理时,需要设置对应3种模式下的3组异常处理寄存器和两组异常委托寄存器以及对应的处理逻辑.

在CVA6中,实现了M模式和S模式的异常处理,支持异常处理委托机制.本文在开发者的基础上,完善了U模式的异常处理和对应的异常委托机制.在系统设计时,架构中规范至少要实现M模式的异常处理,在此基础上可选设置一组或两组异常处理委托机制,这样可以加速系统对异常的处理,减少特权模式之间的切换.

1.4 物理内存保护机制

M模式具有最高的访问权限,可以自由地访问硬件平台,但它无法保证整个代码库都可信.为此,RISC-V提供了保护系统免受不可信代码危害的机制,并且为不受信任的进程提供隔离保护,这种机制叫做物理内存保护(Physical Memory Protection,PMP),其目的是限制每个硬件线程(hart)运行软件可访问的物理地址区域.它能够为每个硬件线程提供M模式控制的寄存器来限制对每一块物理内存区域物理地址访问的特权等级和访问权限(包括读、写和执行).物理内存保护适用于在S模式或U模式的所有访问以及M模式下的部分访问.另外,也适用于基于页面虚拟内存的地址转换.物理内存保护还可以赋予S模式和U模式访问权限,或者更改M模式的访问权限.当访问到被限制的内存区域时,将会引起异常.

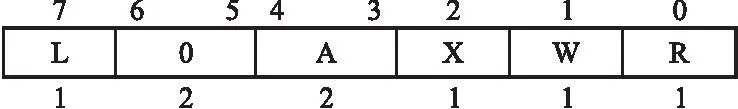

系统中的物理内存保护在硬件逻辑中的实现主要存在于执行和取指单元中.在RISC-V中,PMP的实现主要是通过几个地址寄存器(16或64个)和对应的配置寄存器.配置寄存器可以授予或拒绝读、写和执行权限.当处于U模式的处理器尝试取指或执行读取或存储操作时,将地址和所有的PMP地址寄存器比较.如果地址大于等于PMP地址i,但小于PMP地址i+1,则PMP i+1的配置寄存器决定该访问是否可以继续,如果不能将会引发访问异常.在实现的过程中,如果系统中仅支持M模式,可选择不设置PMP,地址空间均可被处理器访问.图3显示了PMP配置寄存器的构成,主要的控制位包括R、W和X,分别对应于读、写和执行.

图3 PMP配置寄存器构成Fig.3 PMP configuration register format

在本文中,为保证研究的完整性,除仅实现M模式下的情况外,其他配置均实现物理内存保护.当系统中支持M模式和U模式时,将PMP作为唯一的物理内存保护措施.当3种模式同时实现时,PMP与基于页面的虚拟内存同时对物理内存进行保护.

1.5 基于页面的虚拟内存

物理内存保护的方案对嵌入式系统的实现很有吸引力,因为它用相对较低的成本提供了内存保护,但它的一些缺点限制了它在通用计算机中的使用.由于PMP仅支持固定数量的内存区域,因此无法对它进行扩展从而适应更复杂的应用程序.而且这些区域必须在物理存储中连续,因此系统可能产生存储碎片化的问题.另外,PMP无法有效地支持对辅存的分页[20].

S模式提供了一种传统的虚拟内存系统,它将内存划分为固定大小的页来进行地址转换和对内存内容的保护.启用分页的时候,大多数地址(包括读取和存储的有效地址和PC中的地址)都是虚拟地址.要访问物理内存,它们必须被转换为真正的物理地址,这通过遍历页表来实现.页表的叶节点指示虚地址是否已经被映射到了真正的物理页面,如果是,则指示了哪些权限模式和通过哪种类型的访问可以操作这个页.针对RV32和RV64,RISC-V提供了不同的分页方案.RV32的分页方案是Sv32,RV64的分页方案包括Sv39,Sv48和Sv57,其中Sv39是最受欢迎的一种[20].

在CVA6中虚拟内存支持Sv32和Sv39两种方式.从系统设计角度来看,存在支持S模式,不实现基于页面虚拟内存的情况,这种实现可以用于非传统的类Unix操作系统,适用于需要频繁采用系统调用功能的处理器,存储管理采用连续空间分配的方式,这种设计在地址转换时,使用物理地址来代替虚拟地址,在硬件实现中也可以选择不实现PTW和TLB.

1.6 性能计数器

现代处理器中一般都拥有若干被称为硬件性能计数器(Hardware Performance Counter,HPC)的寄存器[21].在RISC-V特权指令规范同样定义了若干CSR寄存器作为计数器和选择器.在进行处理器设计时,可以将这些寄存器作为捕捉特定事件的HPC.这些事件通常包括时钟周期数、已执行指令数、分支预测失败数、各级缓存(cache)的缺失/命中次数、TLB的缺失/命中次数等.这些寄存器通常作为系统寄存器(比如ARM中的System Register,RISC-V中的CSR),从而能够被指令直接访问.利用性能计数器的信息可以更加高效地对系统状态进行监测、对硬件资源进行高效利用[22]、对功耗进行合理管理[23]、对恶意代码进行有针对性的检测[24]、对计算机系统结构[25]进行优化.

在CVA6中,提供了对一级指令缓存(cache)缺失、一级数据缓存(cache)缺失、指令TLB缺失、数据TLB缺失、加载指令数量、存储指令数量、跳转指令数量等性能计数器.在具体处理器设计时,可以考虑对这部分的内容进行调整,针对需求对性能计数进行增减,也可以考虑不设置该模块.

1.7 32种特权配置

根据本节的描述,结合RISC-V特权架构规范,将特权架构配置分成RV32和RV64两大类;在M模式基础上扩展成M,U和M,U,S 3种;异常处理根据特权等级的设置进行异常处理委托程序的扩展分为3类;物理内存保护在仅M模式时不配置;基于页面的虚拟内存在M,U,S的特权模式下可选实现;性能计数器在其他配置中可选实现.如此设计可以实现对特权架构两类32种配置.RV32或RV64对应的16种配置见表2.

表2 16种特权架构配置Table 2 16 privileged architecture configurations

2 实验结果及分析

为了探索RISC-V特权架构配置对硬件实现的影响.本文对32种配置使用综合工具,在28nm工艺库,500MHz的频率下进行综合.在RTL实现上,本文选择将这些配置作为一个参数来进行定义,如Priv_conf=1对应于文章中的配置1,在硬件实现上会设置好对应的模块参数和需要连接的部件.这样设计的意义主要是为了更简便地配置系统的特权架构.在如今IP产商和开源处理器的实现中,大多关注于通用架构的配置,没有对特权架构进行参数化配置的实现.本文针对这一点进行了实现.在功能验证上,均通过了测试基准程序.

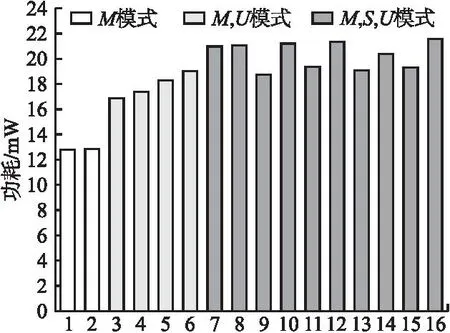

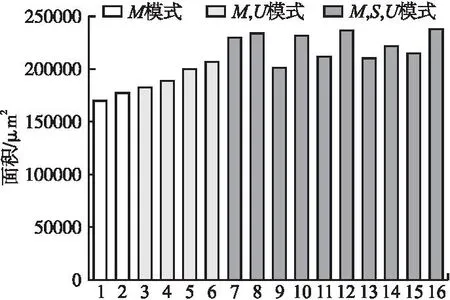

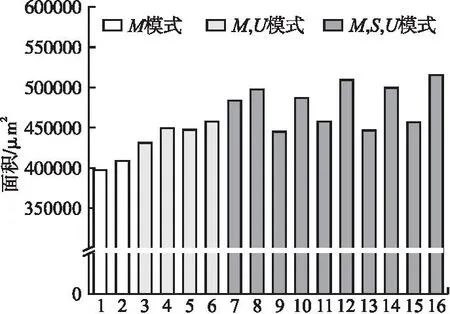

RV32的功耗、面积开销见图4、图6,RV64的功耗、面积开销见图5、图7.由图表中的数据可知,硬件开销随着设计复杂度的增加而增加,当RV32与RV64都采用配置1时,功耗开销从12.76mW增加到了37.64mW,面积开销从169538μm2增加到了397504μm2,当采用功能最全面的配置16时,二者功耗开销增长到21.57mW和47.08mW,面积开销增长到了237554μm2和515353μm2.在配置1的情况下,RV32比RV64功耗减少66.09%,面积减少57.35%,在配置16下,功耗减少54.14%,面积减少53.9%.相同非特权架构下,RV32与RV64采用不同特权配置时功耗最多减少40.83%和20.05%,面积最多减少28.63%和22.89%.在RV32配置下,增加一组异常处理硬件功耗增加约0.25mW,面积增加约1944μm2;在RV64配置下,增加一组异常处理硬件功耗增加约0.63mW,面积增加约8238μm2.在RV32配置下,物理内存保护功耗约占4.54mW,面积约占12838μm2;RV64配置下功耗约占1.52mW,面积约占33813μm2.RV32中基于页面的虚拟内存支持硬件功耗约占1.95mW,面积约占24446μm2;在RV64中功耗4.06mW,面积约占51767μm2.性能技术器在RV32中功耗约占0.083mW,面积约占7676μm2;在RV64中功耗约占0.723mW,面积约占11285μm2.由此可以看出在设计RISC-V处理器时,考虑在特权架构上进行配置,根据需求来选择特权架构有较大的意义.下面主要根据应用场景进行讨论.

图4 RV32不同配置下的功耗开销Fig.4 RV32 power overhead in different configurations

图5 RV64不同配置下的功耗开销Fig.5 RV64 power overhead in different configurations

图6 RV32不同配置下的面积开销Fig.6 RV32 area overhead in different configurations

图7 RV64不同配置下的面积开销Fig.7 RV64 area overhead in different configurations

2.1 基于简单嵌入式系统的配置

仅实现M模式应用场景主要针对简单嵌入式系统.嵌入式系统是由硬件、软件和某些情况下的附件部件组成.一般情况下,这些设备执行专用的功能,共享有限的资源(内存、空间和能耗),具有实时性、多任务处理、高复杂性和资源共享等共同属性[26].

简单嵌入式系统对应于文章中的配置1和配置2.从实验结果来看,这两种配置对应于相同位宽的最复杂特权架构配置会节约20%~40%的硬件资源开销,如果使用32位的位宽,采用配置1和64位的位宽配置16,会有67.10%面积开销和72.89%功耗开销的差距,由此可见,选择较为简单的特权架构配置可以极大地减小简单嵌入式系统设计的硬件资源开销.在实际设计RISC-V处理器时,结合现有开源处理器、IP核产品和本文评估的硬件资源开销,简单嵌入式系统推荐采用RV32,特权架构配置选择本文中的配置1,可以缩减流水线级数来进一步降低硬件资源的开销.在设计之初,可以考虑加入性能计数器来测评系统的性能和体系结构的设计,在真正投入使用时,将性能计数器删减或减少监测的内容.这样的系统设计对应用场景的要求比较苛刻,只适用于某一固定功能的场景应用,拥有所有地址的访问权限有可能会造成系统崩溃,所以要在系统安全和硬件开销之间做权衡.

2.2 基于安全嵌入式系统的配置

当今嵌入式系统处理的数据越来越多,包括我们的个人信息、安全密钥、私人用户习惯等.嵌入式系统的安全性在现代设计中变得越来越重要,但是为嵌入式系统注入强大的安全性并非易事.由于嵌入式系统的特性,不同于传统的计算机(桌面计算机、服务器等),并且对系统所支持的安全性有很大的限制,因为在设计嵌入式系统时需要受到较大的约束,这些约束包括处理能力、存储容量和功耗开销等.所以,在设计安全嵌入式系统时需要尽可能地考虑硬件资源上的开销.RISC-V指令集加入PMP就是为了给系统提供安全保护.以ARM架构的嵌入式系统为例,其设计的ARM Cortex-M4就是采用两种特权分级的系统,这两种分级为特权级和用户级,主要功能是提供了一种存储器访问的保护机制,使得普通的用户程序代码不能意外地,甚至是恶意地执行涉及到要害的操作.处理器支持两个特权级,是一个基本的安全模型[27].

安全嵌入式系统对应于文章中的配置3~配置6.从实验结果来看,安全嵌入式系统增加物理内存保护单元相较于简单嵌入式系统增加5%~20%的硬件资源开销,采用性能计数器会增加大约3%的硬件资源开销,采用异常委托处理机制会增加大约4%~8%的硬件资源开销.综合现有的RISC-V安全嵌入式系统的设计实践和本文的实验结果来看,可以结合设计需求选择RV32或RV64,采用三级~五级流水线,特权架构的配置推荐实现本文中的配置5,性能计数器可在设计之初实现以便于设计人员探索体系结构设计情况,在投入使用时选择将该部分删减或选择较少的监测内容.在系统中加入两种模式的异常处理的设计是有必要的,因为系统在运行用户程序时处于U模式,当异常发生时,如果设置了异常委托处理机制,在U模式下可以处理部分异常,使得系统不必要进入更高级别的特权模式,减少了系统在使用时模式的切换,系统执行更高效.

安全嵌入式系统可以考虑搭载RTOS等轻量级操作系统来实现对系统硬件资源的充分利用.这类型的操作系统主要是用于处理实时应用程序请求,能够处理传入的数据,通常不需要缓冲延迟[28].在实现轻量级操作系统时,可以多个任务共享同一存储空间,此时操作系统可以利用系统中的安全机制来保护独立任务中的任务代码(独立任务的代码是隔离的,不能互相访问).

2.3 基于运行类Unix操作系统的配置

类Unix操作系统是继承UNIX的设计风格演变出来的系统,这些操作系统有许多相似之处,包括FreeBSD及其子类、GNU/Linux、NetBSD及其子类等[29].这类操作系统能够成为计算机系统的调度、控制中心.一方面,此类操作系统可以为裸机改造成为功能强大、各部件高效运行、使用方便灵活、安全可靠的使用环境;另一方面,此类操作系统采用合理有效的方法组织多个用户任务共享计算机的各种资源,最大限度地提高资源的利用率.

运行类Unix操作系统对应于文章中的配置7~配置16.从实验结果来看,运行类Unix操作系统主要增加了基于页面的虚拟内存,相比于安全嵌入式系统而言,系统的硬件资源约增加20%,由此可见,从特权配置角度考虑,这种类型的系统占用资源最多,设计的系统应用场景更丰富.除此之外,性能计数器模块约占系统硬件资源开销的1%,S模式的异常处理机制约占系统资源开销的1%,U模式的异常处理机制约占系统资源开销的1%.由此可见,在设计RISC-V运行类Unix操作系统时,考虑该场景下应用最丰富,占用资源最多,推荐配置16.在这种配置下,系统可以利用性能计数器对整体性能进行监测,可以使用多种异常处理机制来避免特权模式的频繁切换.

从配置的分类来看,还存在不支持基于页面的虚拟内存,但是支持3种特权模式的配置可能,主要包括配置9,11,13,15.这4种配置相对于支持虚拟内存的系统可以节省约15%的硬件资源.但是无法支持类Unix操作系统,此类配置可以考虑采用物理地址寻址,内存管理上采用连续空间分配的方式,如多道连续可变分区法[30]技术,这种技术具有便于实现、访问效率高、空间利用率低等特点.但是这类配置可以提供操作系统使用时的系统调用功能.通过系统调用,不论异常是由什么特权级来处理,都将为系统提供更丰富的扩展.此外,在现代CPU设计中,可以保留TLB,使用软件PTW的方式来配合内存管理单元完成地址转换.这样既可以减少硬件开销,也可以实现基于页面的虚拟内存,但相对于硬件PTW而言,速度会较慢.

3 总 结

RISC-V特权架构的模块化特性满足了各种系统的需求.十分精简的机器模式以低成本的特征支持裸机嵌入式应用,附加的用户模式和物理内存保护功能共同支持了更复杂的嵌入式系统中的多任务处理,管理模式和基于页面的虚拟内存提供了运行现代操作系统所必需的灵活性.在本文中,基于RISC-V的特权架构,在开源CVA6上进行了针对不同应用场景的特权架构设计,分成两类,共32种配置.实现了从简单嵌入式系统到支持类Unix操作系统的系统特权架构配置,采用参数化定义每种配置类型,在实际设计中,可以参照文章中给出的硬件开销差异,选择合适的特权架构配置,更加平滑地进行微处理器设计.