高频变压器导通电流高速采集系统的研究与设计

王南,杨晨,田相鹏

(恩施州红岩寺微波站,湖北恩施,445000)

0 引言

高频变压器作为开关电源中关键的器件之一,对电源的安全、稳定运行具有重要作用,其中高频变压器的导通电流数据作为表征高频变压器安全运行的主要参数,对高频变压器的导通电流数据采集和分析具有重要作用。目前对高频变压器运行情况(主要是否饱和情况)进行测量与判断的方法主要是用示波器观测电流波形[1~2],或者给高频变压器添加偏置电流再测量电感[3~4],根据电感量来判断是否饱和,这种定性的观测方法准确度较低。文献[5]采用了自动测量方法来评估高频变压器的电参数,但主要用来评估温升直流损耗,对是否饱和无法评估。因此,有必要对电流数据进行采集,以便精确地分析高频变压器的关键电参数,比如饱和电流、伏秒容量、饱和电感等。由于高频变压器的导通电流上升速度非常快,需要采用高速数据采集系统配合精确的H 桥控制逻辑,才能实现对电流数据的采集。因此,本文在已有基础上[6],运用FPGA、高速ADC和SOPC 技术,进一步提高采样率,实现了最高20MSPS的采样速率,而且对电路及结构进行了优化,比如在FPGA中增加了死区时间产生器,更改了用74 芯片设计的逻辑保护电路等,为后续对高频变压器电参数的分析与测试具有重要的作用。

1 总体设计方案

如图1 所示为本文提出的基于SOPC[7~8]的高频变压器导通电流采集系统结构图。整个系统结构分为两个部分:一是FPGA 内部逻辑电路,主要模块电路有:NIOSII 处理器电路、自定义IP 核电路和对外接口电路,这部分电路是运用Verilog 开发的数字控制逻辑电路。二是FPGA 外部电路,该部分电路主要有3 个部分构成:H 桥驱动电路、ADC 隔离采样电路和电源电路。

图1 系统整体架构示意图

FPGA 内部电路主要是数字逻辑电路。NIOSII 处理器电路是一个能让NIOSII 运行的最小系统电路。对外接口逻辑电路主要是基于Uart 通信的串口屏显示和上位机软件,通过外接显示屏可以实时显示采样到的电流波形,也可以连接上位机软件将电流数据发送到上位机。自定义IP 核是本文的核心控制逻辑电路,该电路实现H 桥控制逻辑与ADC 数据采样的同步精确控制,即当H 桥打开给高频变压器施加激励时,ADC 驱动电路要同步进行数据存储;当H 桥关闭时,ADC 驱动电路要同步进行关闭;当采样完成后还需要给NIOSII 处理器发送采样完成信号。

FPGA 外部电路中,H 桥驱动电路运用光耦隔离,实现低压的逻辑电路与大电流的H 桥电路隔离,保障低压控制电路的安全、稳定运行。ADC 采样电路主要包含一个隔离运放和ADC 采样电路,隔离运放的作用和光耦类似,也是实现大电流的H 桥电路与低压的弱电电路隔离,同时隔离运放还起到一个滤波和放大的作用,由于隔离运放[9]对高频信号具有很好的滤波效应,在本系统的应用中将极大地减小了导通电流的高频干扰。电源电路分为两部分,一个是给H 桥供电的24VDC/20A 的大电流电源,一个是给低压控制电路供电的辅助电源,辅助电源部分均采用隔离电源,从而实现低压控制电路与大电流的H 桥测量电路电气隔离。

2 硬件电路设计

硬件电路主要包含三个部分:H 桥驱动电路、高速ADC 采样电路和FPGA 内部逻辑控制电路。H 桥电路实现对待测的高频变压器施加激励信号;高速ADC 电路实现电流信号的高速采样,通常开关电源PWM 的时钟都在几十或者几百kHz,有的甚至达到MHz 级别,即电感充放电的时间在几十或者几百μs,因此需要用到高速ADC 来实现信号采集;由于传统的单片机无法实现高速ADC 接口设计,因此本系统需要运用FPGA来实现高速ADC的控制与信号采集。

2.1 H 桥驱动电路

控制信号从FPGA 的引脚发出,经过光耦隔离后,到达MOS 驱动芯片。光耦选择高速光耦芯片TLP2362。MOS 驱动H 桥电路如图2 所示,驱动芯片选择IR2110S 芯片,该芯片为双路驱动芯片,可同时驱动高压侧和低压侧的MOS 管。当驱动端口HL+和HR-为高电平,HL-和HR+为低电平时,MOS 管Q1 和Q4 导通,Q2 和Q3 截止,待测高频变压器导通,导通电流从零开始逐渐增加,采样电阻R24 和R25 上电压从零开始上升;当驱动端口HL+和HR-为低电平,HL-和HR+为高电平时,MOS 管Q1 和Q4 截止,Q2 和Q3 导通,待测高频变压器被施加反向电压,导通电流逐渐减小,采样电阻R24 和R25 上电压逐渐减小。电阻R37 和R38 是在MOS 管处于打开与关断的死区电压时间段,为高频变压器提供一个能量释放通道。通过ADC 检测采样电阻R24和R25 上的电压值就可以计算得到高频变压器的导通电流值。

图2 H 桥驱动电路

2.2 电流采样电路

电流采样电路如图3 所示,该电路为ADC 采样电路的信号处理部分,主要功能是对高频变压器的电流信号进行滤波与放大处理。本系统中考虑了低压弱电部分与大电流的H 桥部分的电气隔离,因此ADC 采样电路部分采用了隔离运算放大器电路。隔离运算放大器采用芯片AMC1200,该芯片具有独特的线性、高输入共模抑制、低直流误差低温漂,另外该芯片具有很好地滤除高频噪声的能力,而且自带放大8 倍的效果,非常适合电流采样中的小信号高噪声信号处理。本系统中AMC1200 的输入方式为单端输入,由于AMC1200 的输出是差分信号,因此,需要用运放UD1A 将差分信号转换为单端信号,该信号再通过一个简易的RC 滤波器后得到信号ADC_LI,然后将该信号接到高速ADC 的模拟输入引脚。

图3 电流采样电路

高速ADC 芯片选择恩瑞浦公司生产的3PA1030,是一款恩瑞浦推出的单电压芯片,10 位,50MSPS(Million Samples Per Second,每秒采样百万次)模数转换器,本系统中由于需要考虑到FPGA 内部电路状态切换,目前采样率只设计为20MSPS。

2.3 FPGA 内部电路

如图4 所示为FPGA 内部电路设计。主要包含NIOSII处理器、采样控制自定义IP 核电路、Uart 通讯模块、SDRAM 控制器和EPCS flash 控制器等。其中自定义IP 核电路包含ADC 模块驱动电路、采样控制逻辑、H 桥控制电路和双端口RAM 存储电路,其中采样控制包含总线接口、采样控制状态机和H 桥驱动状态机。Uart1 连接串口屏,实现人机交互;Uart0 连接电脑的串口助手,用于将采样数据发送到上位机;自定义IP 核电路负责协调ADC 驱动控制、H 桥控制和双端口RAM 对ADC 高速采样数据的存储,同时,也负责把采集到的数据通过Avalon-MM 总线发送给NIOSII处理器。

图4 FPGA 内部电路结构图

本系统中应用双端口RAM 实现数据缓存,因为高速ADC 采样速率很高(20MSPS),高速率的数据无法实时传输给NIOSII 处理器。因此,在数据采样过程中,将数据临时存储在双端口RAM 中,当数据采集完成后,NIOSII 处理器再从双端口RAM 中读取数据即可。

FPGA 内部的各个IP 核电路,运用quartusII 内的Platform Designer 工具来进行连接集成。其中Nios II 处理器是Qsys 系统中最为核心的一个IP 核,它是系统的调控中心,负责中断分配、地址管理、内存调度等控制任务。Nios II 和各个外设控制器之间通过Avalon 总线通信。

3 软件设计

软件设计分为两个部分,一个是自定义IP 核的运行流程,需要说明的是,该运行流程不是严格意义的“软件”,该部分执行机构是用Verilog 设计的数字电路。另一个部分是在NIOSII 处理器中运行的C 语言代码设计。

3.1 自定义IP 核运行流程

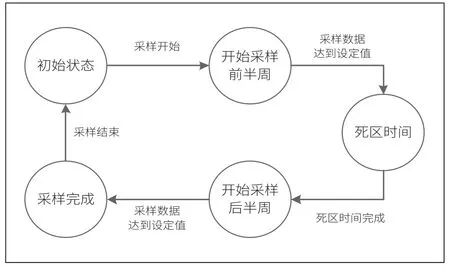

如图5 所示为自定义IP 核状态机的状态转换图,在上电后默认情况处于初始状态;当状态机收到NiosII 处理器发出的开始采样命令后,状态机转到开始采样前半周状态;在采样前半周状态,H 桥开始动作,高频变压器充电,ADC采样有效,开始数据采样;当采样数据达到设定值时,转到死区时间生成状态;在死区时间生成状态,H 桥处于关闭状态,防止H 桥的上下半桥同时导通,造成MOS 开关管烧毁,死区时间完成后进入开始采样后半周状态;在采样后半周状态,H 桥切换,高频开关电源放电,当采样数据达到设定值时,采样结束,状态机转入采样完成状态。在采样完成状态,samper_ok 信号输出高电平,指示采样完成,NiosII 采样到该信号为高电平时,开始在双端口RAM 中读取数据,当数据读取完成后,NiosII 处理器给寄存器sp_start_reg 写入0x00,状态机转入初始状态,以备下一次测量。

图5 自定义IP 核运行状态机状态转换图

H 桥的输出是根据控制逻辑的状态变量来实现的,即在初始状态和采样完成状态H 桥的HL+、HR-、HL-和HR+均为低电平,此时待测电感处于关闭状态;在开始采样前半周状态时,HL+和HR-为高电平,HL-和HR+为低电平;在采样后半段状态时,端口HL+和HR-为低电平,HL-和HR+为高电平。另外由于驱动芯片IR2110S 无死区电压保护机制,需要用FPGA 逻辑来产生一个死区时间,因此在开始采样前半周完成后,需要进入死区时间生成状态,在该状态下,H 桥的HL+、HR-、HL-和HR+均为低电平。

3.2 NIOSII 软件设计

本系统中采样与算法计算需要的时间相对较长,辅助功能中的LED 指示灯需要较长时间的延时,而与串口屏的通信的实时性要求较高。可以看到每个功能模块对时间的延时不相同,为了简化应用程序的编程,本系统采用ucOS 操作系统来实现。设计了3 个任务,分别是电流采样、串口屏通信和辅助功能。

如图6 所示为电流采样的软件流程图。上电后,进行系统初始化。然后系统就一直监测Uart屏上的开始测量按钮是否被按下,当开始测量按钮被按下时,系统开始测量,首先会给自定义IP 核发送参数(采样间隔时间和采样数据量),然后再给自定义IP 核发送开始测量命令0xaa,此时自定义IP 核会输出开关管的开启与关闭逻辑,同时进行高频变压器电感电流数据的采样,并存储在自定义IP 核内的双端口RAM 中。然后软件会一直查询自定义IP 核是否采样完成,当采样完成后,读取双端口RAM 中的采样到的电流数据,当数据读取完成后,软件给自定义IP 核发送结束采样命令0x00。最后进行电流数据处理。

图6 NIOSII 处理器内电流采样流程图

4 实验效果

本系统的FPGA 最小系统模块和高速ADC 模块选择正点原子的EP4CE10 最小系统板和双路高速AD 模块。搭建的硬件测试平台如图7 所示。在测量电流时,采样间隔固定的设置为0.1μs(最高可实现0.05μs),根据设定采样数据量,即可控制给高频变压器施加激励的时间,通常来说,随着施加激励的时间逐渐增加,高频变压器会出现饱和现象,此时电流曲线斜率会快速增加,形成突变波形。

图7 系统硬件实物图

如图8 所示为在上位机上收到的电流数据,可以看到,当给高频变压器施加激励的时间为50μs 时,电流曲线的斜率总体是线性的(也有微小的波动);当激励时间加到65μs时,可以看到曲线在末尾段,明显出现斜率突增的情况,可以根据这个特性来判断高频变压器是否饱和,也可以根据施加激励的电压和时间来精确计算高频变压器的容量、饱和电流等参数,为高频变压器的电参数评估起到重要作用。

图8 上位机采样到的电流数据

5 结论

本文设计的基于SOPC 的针对高频变压器导通电流高速测量系统,实现了对导通电流的精确测量。通过对导通电流的测量,可以精确评估和计算高频变压器的饱和电流、伏秒容量等参数,对开关电源设计和安全运行评估具有重要的指导意义。本系统目前可实现最低0.05μs 的采样间隔,最大实现20A 的导通电流测量,满足小功率开关电源的设计验证需求。后续还将进一步升级优化,实现更快速更大电流容量的测量系统。