基于FPGA 的多通道数据监测存储系统∗

耿 坤 张会新

(中北大学微纳器件与系统教育部重点实验室 太原 030051)

1 引言

导弹、火箭等武器装备在研发环节需要进行大量测试任务,通过使用多种高精度传感器采集导弹试射实验中产生的各项数据如:冲击参数、振动参数、压力参数、温度参数等。随着武器装备的发展,试射试验中需要获取的传感器数据量也日益增加,对数据处理系统的多通道突发数据处理能力、实时监测能力、存储可靠性的要求也越来越高[1]。国内对于数据监测、存储装置的研究在诸多方面取得了进展,如文丰等[2]对FLASH 编程、ECC 纠错等关键技术进行了分析;王子懿等[3]对FlASH 的流水线存储模式及千兆以太网传输技术进行深入研究;刘胜等[4]研究了多路信号并行混合采集存储的问题;韩子舟等[5]设计了具有1553B 接口的高速数据采编器。

为进一步拓展数据通道数,对复杂度更高的数据进行处理,并对挂载在1553B 总线上设备工作状态进行监测,实现突发故障的实时上报。设计了一种多通道数据存储监测系统,该系统支持并行采集55 路模拟量、2 路PCM 码流、2 路LVDS 数据且具有1553B 总线监测功能,实现了以零误码率对高速率差数据进行编帧、存储,其中数据速度低至0.32kbit/s(40Hz 模拟量数据),高达200Mbit/s(LVDS2 数据),满足了对导弹试射实验中多通道、高复杂度数据的采集、存储、监测、回读分析的需求。

2 系统方案设计

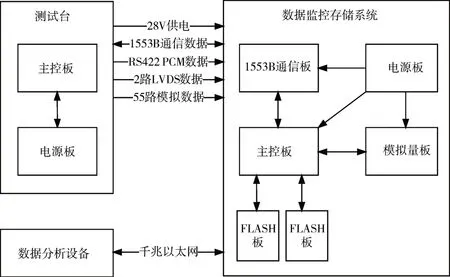

为提高系统处理多通道数据的可靠性,在功能上采用模块化设计,根据实际功能划分为主控板、1553B 通信板、55 路模拟量采集板、双FLASH 存储板和电源板,在提高模块功能内聚性的同时降低了模块间的干扰,系统框架如图1所示。

图1 系统整体框架

1553B 通信板既作为远程终端RT 接收总线控制器(飞控计算机)发送过来的指令和计算机遥测字,同时作为总线监视器MT,监测1553B 总线传输的所有数据[6],及时将故障设备信息反馈至飞控计算机并对通信关键参数信息进行记录。模拟量板设计两级模拟信号通道选择拓扑结构,通过循环切换模拟开关,实现55 路模拟信号的隔离采集,通过主控板控制信号实现模拟信号采样率的控制。电源板通过使用高可靠性器件HSFC28-461 以及DC/DC 转换模块HSDF28S5 对外部输入的28V 电压进行滤波后转换为系统所需要的5V 电压,有效保障了系统供电的稳定性。双FLASH 存储板存储容量分别为8G 和32G,用于并行存储混合编帧数据以及LVDS 高速图像数据[7],两者单独放置于抗高过载冲击的保护仓内,有效保障试射试验中落地时存储芯片的安全。

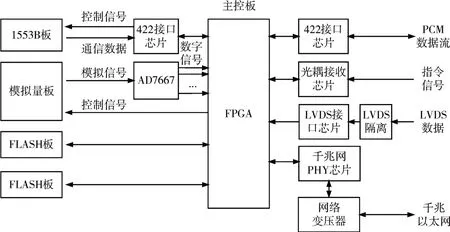

主控板为系统的核心,与其他板卡相连,接收多通道模拟量、PCM 码流、LVDS 和1553B 总线数据,实现了数据综合功能及千兆以太网设备回读监测功能,主控板框架如图2所示。

图2 主控板框架

3 接口电路设计

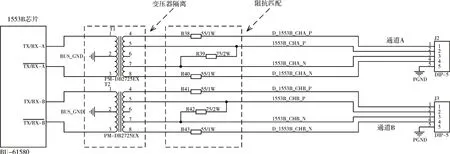

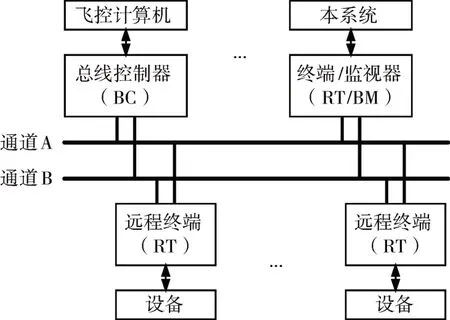

3.1 1553B通信热备份

1553B 总线是一种高实时性、可靠性的通信方式,1553B 通信板采用双通道(总线A 和总线B)冗余设计,1553B 总线通过在两个通道间自动切换来获得冗余容错能力和故障隔离,有效保障了在恶劣环境下数据传输的可靠性[8]。

为满足电缆长度需求,两个通道均采用变压器耦合方式与总线电缆进行连接,选用BT2726A且匝数比为1:1.79,通过阻值等于总线电缆特征阻抗的电阻与耦合变压器相连,以确保传输线不匹配造成的反射最小,同时避免变压器出现短路故障损坏总线系统。变压器耦合与直接耦合相比,具有更好的电气隔离、阻抗匹配和较高的噪声抑制性能,电气隔离避免了1553B 板因自身故障或者短截线阻抗失配对主总线的影响,1553B 热备份硬件设计如图3所示。

图3 1553B热备份硬件电路原理

设备上电以后默认采用A 通道传输数据,B 通道作为备用组成1553B 总线通信板的热备份结构,当A 总线出现故障时由1553B 总线控制芯片切换至B 总线且不影响总线通信,选用B61580S3 作为1553B 控制芯片,该芯片内部集成半双工编码解码器,包含完整的1553B 总线控制协议,可实现远程终端和监控终端模式。

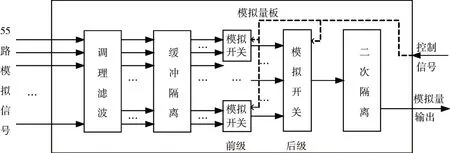

3.2 模拟信号采集

针对8路20kHz、9路5.12kHz、38路40Hz,共55路模拟信号采集的需求,使用模拟开关设计了两级模拟信号通道选择拓扑结构[9]。

模拟开关型号选用ADG706,该芯片单片具有16 通道,开关时间为40ns、导通阻抗仅为5Ω,完全满足对模拟信号质量、通道数以及采样频率的要求。分别选用5 个、1 个16 路模拟开关作为前、后级模拟开关,通过对ADG706 芯片4 位地址信号A0~A3 及1 位使能信号的配置可实现模拟型号16路到1 路的选通,最大可实现16×5=80 路模拟通道的选择切换。模拟信号经调理滤波、两级模拟开关、运放隔离后传递至位于主控板的ADC 转换芯片,模拟量板框架如图4所示。

图4 模拟量板框架

AD 芯片选型为AD7667,是一个16 位的逐次逼近型模数转换器,最高速率1MSPS,具有低功耗、速度高等优点。由于该芯片模拟电压采集范围为0~2.5V,而模拟信号输入电压范围为0~5V,故在调理滤波部分采用两个1MΩ电阻进行1/2 分压处理。同时,大阻值输出电阻提高了模拟量板的电压采集能力。此外,利用RC低通滤波电路,过滤信号中的高频分量;在缓冲隔离部分,利用电压跟随器输入阻抗无限大的特点,为采样信号提供缓冲,避免了后级电路因输入阻抗较小产生的信号损耗,同时隔离采样电路对前级电路的影响;二次隔离部分仍然使用电压跟随器隔离AD7667 模数转换芯片对前级电路的影响,进而提升采样电路的稳定性。

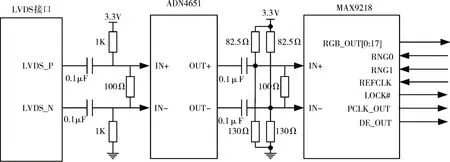

3.3 LVDS隔离接收

LVDS 信号隔离采集电路原理如图5 所示,为防止恶劣环境中的外部接口因静电放电、浪涌等外部因素所带来的影响,在LVDS 接口处设置隔离缓冲器ADN4651,当传输空闲时AND4651 的故障安全机制可拉高输出,确保DE_OUT=0,从而无法建立连接,增强了LVDS 接收电路安全性、抗扰能力。差分输入前端并联100Ω的电阻可在不影响信号完整性的基础上有效降低干扰,进而避免对后续电路的影响。

图5 LVDS信号隔离采集电路原理

采用MAX9218解串芯片设计LVDS接收电路,该芯片通过时钟恢复技术,将差分串行数据恢复为18 位并行的RGB_OUT 信号,最大支持700Mb/s 传输速率,满足LVDS所需最大200Mb/s的传输速率。

4 系统软件设计

4.1 1553B双通道监测逻辑设计

1553B 总线采用指令/响应型通信协议,具有3种类型的终端分别是总线控制器(BC)、远程终端(RT)、总线监控器(BM),其网络拓扑结构为总线型网络,采用双余度方式具有A、B 两个数据通道,如图6所示。

图6 1553B网络拓扑图

BC负责网络上信息的控制与调度,RT响应BC的命令并进行数据传输,BM 监听总线上所有的数据且不参与数据传输,总线默认使用通道A传输数据,当BC发现消息错误时会发起通道切换命令,并在备份通道上再次发送该消息。

1553B 模块不仅要作为总线监视器MT 实时监测A、B两条总线上所有数据,同时还作为远程终端RT 接收总线指令并进行消息应答、上报故障信息,因此将1553B 协议控制芯片B61580S3 配置为RT/MT 工作模式[10]。该模式下,RT 地址设置为18,实现RT 功能,同时作为MT 监测A、B 通道上所有BC与RT间的交互信息,监测到故障后,对故障信息进行解析与记录,待BC发起上报命令后,将解析数据上报到BC,监测流程如图7所示。

图7 1553B监测流程

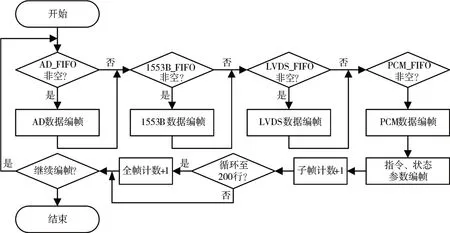

4.2 并行分时编帧逻辑设计

编帧时,若仅考虑低速数据则会使高速数据溢出,导致数据的丢失与错乱;若仅考虑高速数据,则会造成严重的带宽浪费,导致帧结构中填充大量无效数。为了同时存储高至200Mbps 及低至0.32kbps 的大速率差数据,兼顾速度与资源利用率,设计分时并行相结合的编帧策略。

将高速LVDS2 数据与低速数据分离并行编帧,对多通道低速数据设计异步FIFO 进行缓存并按照帧结构表分时编帧。通过此方法,在保障高速数据完整编帧的情况下,有效提高了低速数据帧中有效数据的占比,下面着重介绍分时编帧的方法。

为实现多通道、高复杂度数据综合功能,设计子帧、副帧逻辑,全帧数据矩阵由125 个子帧(行)及200 个副帧(列)组成,全帧速率为50 帧/s,数据点位宽为8 位,编码速率可达:50*125*200*8=10Mbps。子帧以1 个字节的行计数及固定占2 个字节的EB 90 标志结尾,全帧则以最后一行的后3字节帧计数及固定占2字节的14 6F 标志结尾。帧内以EE 作为数据段无效数,在数据空缺或不足时自动填充;以CC作为填充数,充当两种数据间的分隔,每种数据在最后一行均有结束标志如ADAD、AAAA、3A3A 等用以区分数据种类;最后,在特定位置对指令参数、工作状态参数进行记录,帧结构表如表1所示。

表1 帧结构表

编帧开始前,将多通道数据缓存在异步FIFO内等待读取,根据帧结构中要求的数据量设置相应FIFO 逻辑空的阈值,异步FIFO 的引入不仅解决了数据缓存问题,同时解决了多通道数据的跨时钟域问题。

编帧开始后按照帧结构表顺序轮询各FIFO 内数据[11],若非空则读FIFO 进行编帧,若数据不足则在该子帧区段全部填充无效数EE,直到对应FIFO内数据准备充分,混合编帧流程如图8所示。

图8 混合编帧流程

4.3 FLASH存储/监测逻辑设计

在试验的不同环节,地面监控台会下发数据监测、数据回读指令,系统则需要根据指令的不同切换数据通道及功能,进而实现多通道数据的实时监测与零误码率存储功能的无缝切换。

本设计使用三级异步FIFO缓冲结构[12],如图9所示,单个FIFO 容量为16K 字节,在解决跨时钟域问题的同时又防止了数据溢出。

图9 FLASH存储/监测框图

第1 级为FIFO_1~FIFO_4,跨时钟域缓存LVDS2 回波数据及多通道编帧数据并根据监测指令将数据送入FIFO_3和FIFO_2,直接由FIFO 选择模块实时上传至上位机,或根据记录指令将数据送入FIFO_1 和FIFO_4,编码后分别存入8G、32G FLASH 存储芯片。待监控台下发数据回读指令后,读FLASH 数据至第2 级缓冲FIFO_5 和FIFO_6进行数据纠错,完成后进入第3 级缓冲FIFO_7 和FIFO_8,最后经由FIFO选择模块回读至上位机。

由于NAND FLASH 工艺结构局限性,数据在存储过程中存在小概率的位翻转问题,采用基于汉明码的ECC 纠错方案[13]可解决此问题。

每组Hamming 校验码能够实现1bit 纠错和2bit 检错,具有便于硬件实现,计算速度快,实时性高等优点。

编码模块单次将256bit 数据作为8 列*64 行数据矩阵进行处理,采用2 log264 =12bit 行编码及2 log28 = 6bit 列编码对该矩阵进行处理,实现对256bit数据的1 bit纠错和2 bit检错,故对于FLASH每页8192bit 数据,可提供128bit 纠错能力以及256bit 检错能力,有效保障了数据可靠性。汉明码编码[14]数学表达形式如下:

cp0~cp5为列校验码,由64bit的所有对应位通过异或运算产生,rp0~rp11为行校验码,

数据写入FLASH 时进行第一次编码,读出时根据读出的数据进行第二次编码得到rp'、cp',解码模块分别将前两次编码值rp 和rp'、cp 和cp'进行异或运算得到rp_xor、cp_xor,根据运算结果进行如下判断:

若rp_xor=0 且cp_xor=0,则FLASH 存储无位翻转错误。

若rp_xor 或cp_xor 不为0,则分别统计rp_xor和cp_xor 中1 的个数是否和0 的个数相等:相等则表明发生1 位误码,则根据rp_xor(11)&rp_xor(9)& rp_xor(7)& rp_xor(5)& rp_xor(3)& rp_xor(1)得到误码所在数据矩阵的列偏移量,根据cp_xor(5)&cp_xor(3)&cp_xor(1)得到误码所在数据矩阵的行偏移量,最后通过纠错模块将错误位修正;不等则说明发生多位误码且无法纠正。

4.4 可重传千兆以太网通信逻辑设计

千兆网通信模块采用美满(Marvell)公司生产的88E1111 系列芯片,负责接收并解析上位机下发的指令及向上位机传输数据,采用便于硬件实现的UDP 协议,但UDP 协议是无连接、不可靠的协议,为保障传输数据完整性,可在UDP 传输中引入握手、超时重传机制[15]如图10所示。

图10 UDP握手、超时重传机制

在上位机发送回读命令前,首先发送ARP 请求,设备回应该请求,发送自身MAC 地址到上位机,之后进行数据上传,连续发送4MB 数据后等待上位机命令,此时上位机若收到4MB 数据则发送握手命令进行下一次4MB 数据上传,若超时未收到4MB 数据则发送重传命令,设备重新传输上一次4MB 数据。经验证,通过UDP 握手、重传机制可成功解决常规UDP 传输过程中的丢包问题,实现可靠的数据回读。

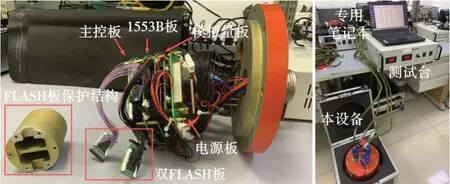

5 测试结果与分析

数据监测存储系统实物及测试台如图11 所示,为测试该系统工作可靠性,测试台通过测试电缆与设备相连,模拟多路LVDS、PCM、1553B、模拟量信号源;通过千兆以太网接口与设备相连,用于数据回读、监测;通过编写专用测试上位机,对该系统进行数据及控制信号的下发、数据监测、回读测试。

图11 实物及测试台

数据回读后,使用上位机数据分析功能,首先根据帧结构数据类型结束标志对数据进行拆分,将原始数据1553BM、1553RT、AD采集、LVDS1、PCM1和PCM2 等5 个数据文件,接着分别对各类型数据进行数字量分析,根据测试数据中帧计数及自加数的连续性判断是否存在误码、数据丢失等问题,分析结果显示数据解析成功、无错,上位机数据分析结果如图12所示。

图12 上位机数据分析

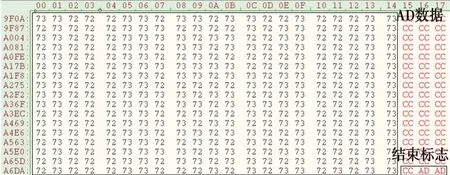

查看原始数据,部分AD 数据采集结果如图13所示,采样点量化精度为8 位,当进行数据分析时,根据波道表对每一路模拟量进行提取。

图13 原始数据中部分AD数据

LVDS、PCM、1553B测试数据均为带有帧计数、帧尾的自加数。如图14所示,以部分LVDS数据为例,有效数据由512字节的自加数、2字节帧尾、4字节帧计数组成,EE EE 为填充的无效数,当进行数据分析时,上位机对其进行剔除。不同数据间以CCCC 作为分隔,在副帧最后一行设有LVDS 数据结束标志3B3B。

图14 原始数据中部分LVDS数据

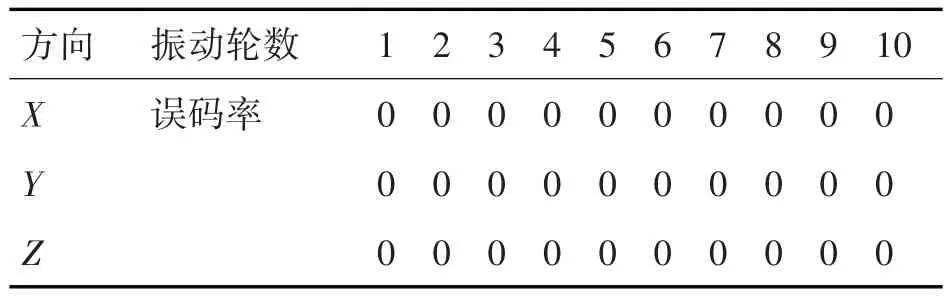

为测试本设备在极端温度环境下可靠性,进行多轮-40℃~60℃温循实验测试其误码率,单次温度保持时间为30min,测试结果如表2 所示。为测试在极端振动环境下的可靠性,进行X、Y、Z三个方向振动实验测试其误码率,每个方向的振幅为0.15mm,振动频率为50Hz,振动加速度为0.75G,测试结果如表3所示。

表2 温循实验测试结果

表3 振动实验测试结果

通过多次高低温循环测试、振动实验、数据监测、存储测试,使用上位机对回读数据进行分析,结果表明本设备在-40℃~60℃温度环境下数据存储无误码,具有良好温度适应性。

6 结语

本文针对传统数据记录设备通道数少、缺少实时通信、总线监控能力的问题,设计了基于FPGA的高可靠性飞行器数据监测存储系统,实现了对多通道、高复杂度数据、的监测、存储功能及1553B 总线通信功能,通过硬、软件设计提高了系统可靠性。经验证,该系统能够适应复杂恶劣的飞行器数据监测、存储应用场景,具有较大工程应用价值。