基于FPGA 的高分辨率电容检测系统设计

刘铭洋,焦继业,吕昱青

(1.西安邮电大学专用集成电路设计工程技术中心,陕西西安 710121;2.西安邮电大学电子工程学院,陕西 西安 710121)

电容式湿度传感器的主要工作原理是将环境湿度的变化转化为电容变化,利用此特性将非电量转化为电容量。通常电容式湿度传感器的电容变化范围较小,为皮法量级,属于微小电容变化。

国内外学者进行了多种电容检测电路的研究,文献[1]利用谐振法设计电容测量电路,但容易受到寄生电容、杂散电容的影响。因此该类方法很少使用于测量电容式传感器这种微小的电容方面。文献[2]利用交流电桥法设计电容测量电路,此电路虽然能够测量差动电容值,但是不能测量单个电容的容值,具有较大的非线性。文献[3]利用电容充放电法设计电容测量电路,该电路使用的模拟开关可能会引入电荷注入效应和时钟馈通效应的问题。文献[4]利用电容-频率法设计电容测量电路,该电路虽然抗干扰能力强,便于长距离传输,可移植性高,便于与其他数字电路进行组合,但也易受电路寄生电容影响,并且需要设计电路读取频率的变化。

针对以上问题,设计了一种基于FPGA 的高分辨率电容检测电路,根据得到的实验数据分析误差来源,针对寄生电容对测量结果的影响进行了一定程度的抑制。

1 系统的设计与实现

基于现场可编程门阵列(FPGA)的高分辨率电容检测电路整体如图1 所示,它主要由电容-频率电路和时间间隔测量电路组成。其中电容转频率电路主要利用电容充放电特性将容值的变化转为频率的变化。时间间隔测量电路以Xilinx 公司的Artix-7 系列FPGA 芯片为载体,可以精确地测量由电容-频率电路输出的脉冲信号的持续时间。

图1 基于FPGA的高分辨电容检测系统结构

2 电容-频率电路设计

电容转换电路主要有电容-电压和电容-频率这两种基本理念[5],电容转电压电路利用开关电容电路原理,通过时分复用模拟开关,利用电荷累计和电容反馈,得到与待测电容值有关的输出电压[6]。

但是开关电容电路只能在CMOS 工艺中实现。并且随着模拟开关的打开或关断,少量电荷可从数字控制线上通过电容耦合至模拟信号通路,即可能发生电荷注入效应,这会导致输出的电压值有一个不可估计的误差[7]。输出的电压还需要模数转换器(ADC)进行采集,将电压信号转换为数字信号。若C1与C2的比值差别不明显,则Vout的变化也不明显,这就需要有效位数更高的ADC,从而导致整个电容检测电路的难度上升。

因此,利用对待测电容的充放电特性设计电容-频率电路,其结构和原理如图2 和图3 所示。

图2 电容-频率电路

图3 电容充放电原理

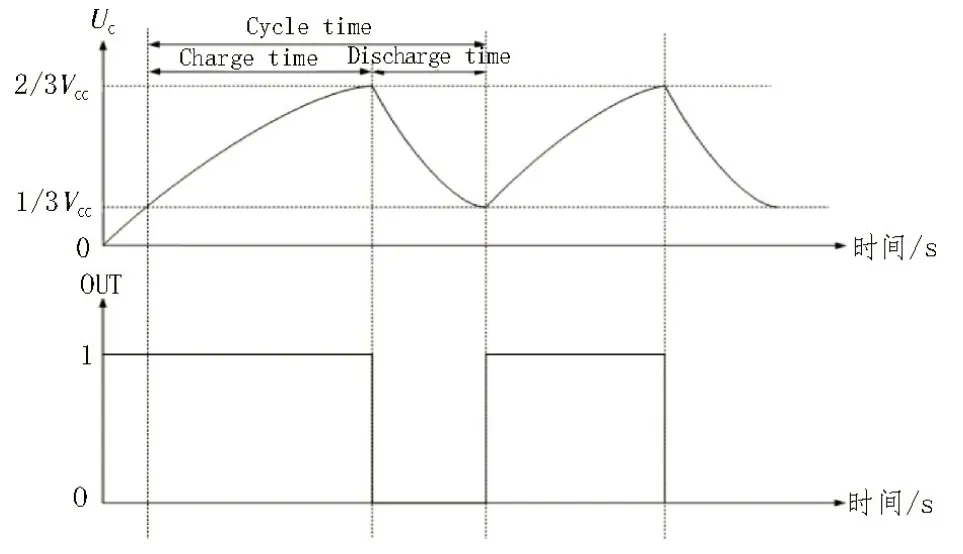

其工作分为两个阶段:充电阶段(Charge time)和放电阶段(Discharge time)[7]。

在充电阶段时,系统开始时VCC通过R1、R2给Cx充电,OUT 输出1,则UC从1/3VCC上升到2/3VCC所需时间为:

当UC上升到2/3VCC时,触发RST 引脚置0,芯片内部的放电管导通,Cx通过R2放电,UC下降,OUT 输出0,则UC从2/3Vcc下降到1/3Vcc所需时间为:

当UC点电压下降到1/3VCC时,继续重复给待测电容Cx充电和放电。因此整个系统工作一个周期的时间应该为:

利用电容转频率电路对芯片充电,通过测出电路输出高电平的持续时间来反解出待测电容Cx,因此待测电容Cx为:

这种电容-频率电路容易实现,而且可以结合基于FPGA 设计的时间间隔测量电路进行电容容值检测,该方案具有易移植性和可集成性。因此只要精准测量电容-频率电路输出的脉冲信号持续时间就可以得到待测电容的容值,因此需要设计一个高分辨率的时间间隔测量电路。

3 时间间隔测量电路设计

在前期的工作中,电容-频率电路已经将待测电容值转化为一个持续时间待测的脉冲信号,其电路输出的脉冲信号持续时间为微秒级。因此需要利用FPGA 设计一个时间间隔测量电路,用于将这段脉冲信号的高电平转化为数字信号。其中最常用的方法是采用直接计数法,其电路原理是当脉冲信号上升沿到来时,由系统时钟控制的计数器开始计数;当脉冲信号的下降沿到来时,计数器停止计数[8]。实际直接计数法原理如图4所示。

图4 实际直接计数法原理

理想中脉冲信号的持续时间为:

在实际的应用电路中,脉冲信号不可能恰好在一个系统时钟的上升沿到来,如图4 所示,因此无论使用多快的时钟都难免存在一定的误差,所以实际脉冲信号的高电平时间为:

虽然在FPGA 里可以用PLL 来实现时钟的倍频,从而通过提高时钟频率来提升脉冲信号的测量精度,进而提升整个测量系统的分辨率[9]。若是分辨率想要达到纳秒级甚至更高,则至少需要频率量级为千兆赫兹的时钟。高频率的时钟在翻转的过程中,若不满足建立时间的约束,则触发器会产生“亚稳态”状态,导致无法得到正确的锁存结果[10],所以仅仅使用直接计数法的测量技术很难用于对分辨率要求高的领域。

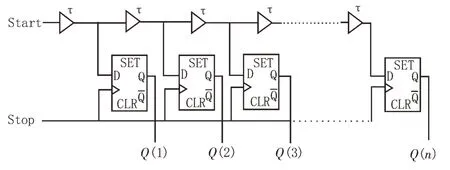

抽头延迟链法(Tapped Delay Line,TDL)利用器件延迟来检测待测脉宽,从而实现测量分辨率的提高[11]。随着CMOS 工艺水平的提高与半导体ASIC 技术的发展,门级单元延迟时间大大缩短,集成度越来越高。延迟链是由多个具有固定延时的门级单元级联构成的,将延迟链的输出通过D 触发器实现信号锁存,这种方式称为抽头延迟链法[12]。其原理如图5所示。

图5 抽头延迟链法结构

图5 中使用若干个理论上延迟大小均为τ的延迟单元串联为线性结构,在每个延迟单元后面引出一个输入到D 触发器中锁存。Start 信号触发后脉冲信号在延迟链中开始传播,经过n级延迟单元并在Stop 信号边沿触发后,D 触发器阵列对延迟链中多个数据值进行锁存。根据抽头延迟链法的测量原理,测量的时间间隔可以表示为:

其中,K为时间间隔测量期间Start 信号在延迟链中锁存的延迟单元数量。

随着半导体工艺的不断进步,采用延迟单元构造延迟链设计的TDC 电路具有皮秒级的测量分辨率,并且易于封装到集成度高的芯片里,配合其他功能电路焊接较小面积电路板实现测量[12]。此外,基于延迟链设计的TDC 的动态测量范围受到延迟单元个数的约束,需要结合其他TDC 方案增加其动态测量范围。

文中结合直接计数法和延迟链法,设计了一种基于延迟链内插法的时间间隔测量电路。基于延迟链内插法时间间隔测量主要有三方面,其结构如图6所示。一是采用直接计数法设计粗测量模块,保证所设计时间间隔测量电路的测量精度满足应用场景需求;二是结合细测量模块,设计启停信号提取模块;三是采用延迟链设计细测量模块,提高所设计时间间隔测量的测量精度。

图6 时间间隔测量电路结构

3.1 粗测量模块设计

粗测量模块是基于直接计数法设计的TDC 模块,其作用是在最大脉冲信号的测量范围之内,对外部输入的待测信号Pulse 进行分辨率为一个时钟周期的粗略测量。其模块本质是以计数时钟为时基的时序电路,也就是同步计数器。

待测信号Pulse 的高电平持续时间的粗略值可用Count×TCLK来表示,其中Count 表示同步计数器输出的值,TCLK表示计数时钟的时钟周期,在这里使用外部晶振频率为100 MHz 作为系统时钟和计数时钟。

文中设计的粗测量模块可以测量的脉冲持续时间为0~2 s,测量分辨率为一个时钟周期,即10 ns。

3.2 信号提取模块

信号提取模块的作用是提取出用来在延迟单元组成的延迟链进行传播的信号Start。信号提取电路结构如图7 所示。

图7 信号提取电路结构

3.3 细测量模块设计

可配置逻辑块(CLB)是每个FPGA 芯片逻辑单元的基本单元,也是实现时序电路和组合电路的主要组成逻辑资源。并且每个CLB 都包含一对Slice,每个Slice 是FPGA 芯片内部最小的逻辑单元,每个Slice 由四个查找表(LUT)、八个触发器(FF)和其他一些逻辑所组成。其他逻辑中包含着一个CARRY4逻辑,称为四位超前进位逻辑[13]。

使用Vivado 原语实例化CARRY4 进位逻辑[14]。将Start 信号作为第一级CARRY4 进位逻辑的进位初始端口CYINIT 的输入,将每一级的进位输出的最高位CO[3]作为下一级CARRY4 进位逻辑的进位端口CI 的输入,因此就可以实例化出一个以CARRY4 进位逻辑为延迟单元组成的延迟链,并且该延迟链的级数可根据测量范围的大小进行调整。

在细测量模块布局布线后,对其进行时序仿真,仿真数据显示,经过一个CARRY4 进位逻辑构成的延迟单元所需的时间为114 ps。FPGA 采用的是外部晶振,频率为100 MHz 的时钟。因此整个基于FPGA 的高分辨率电容检测电路的测量分辨率为114 ps,可将10 ns 之内脉冲信号的高电平持续时间精准测出。

4 系统仿真与误差分析

4.1 测试分辨率

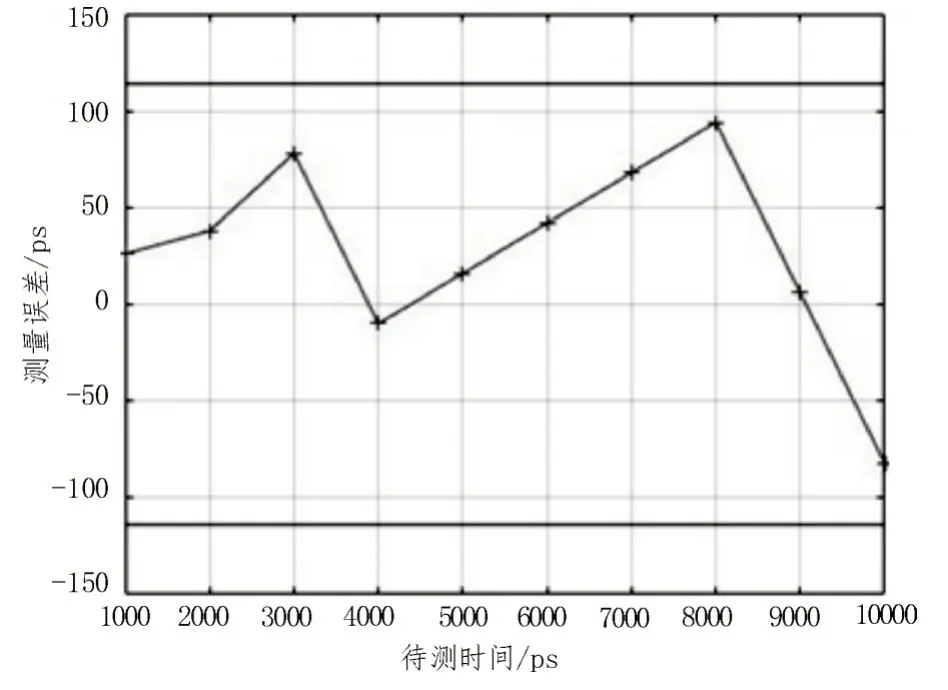

在前文对CARRY4 进位逻辑作为延迟单元进行时序仿真时,得到信号经过一个CARRY4 所需时间为114 ps,但是仍需对延迟链进行仿真测试。在进行时序仿真时,使用小于10 ns 的脉冲信号在延迟链中进行传播。得到小于10 ns 的脉冲信号通过延迟单元的个数,以此验证信号经过一个CARRY4 所需时间是否可以作为LSB。

从表1 以及图8 数据中可以直观看出,待测脉冲持续时间与对应的测量结果之间的误差绝对值均小于114 ps,由此可以确定文中所设计的基于延迟链内插法TDC 的分辨率为114 ps。对此,若应用场景在系统设计测量分辨率的范围内,文中所设计的基于延迟链内插法TDC 能够达到所需的性能指标和功能需求。

表1 时序仿真测量结果

图8 时序仿真测量误差图

4.2 误差分析

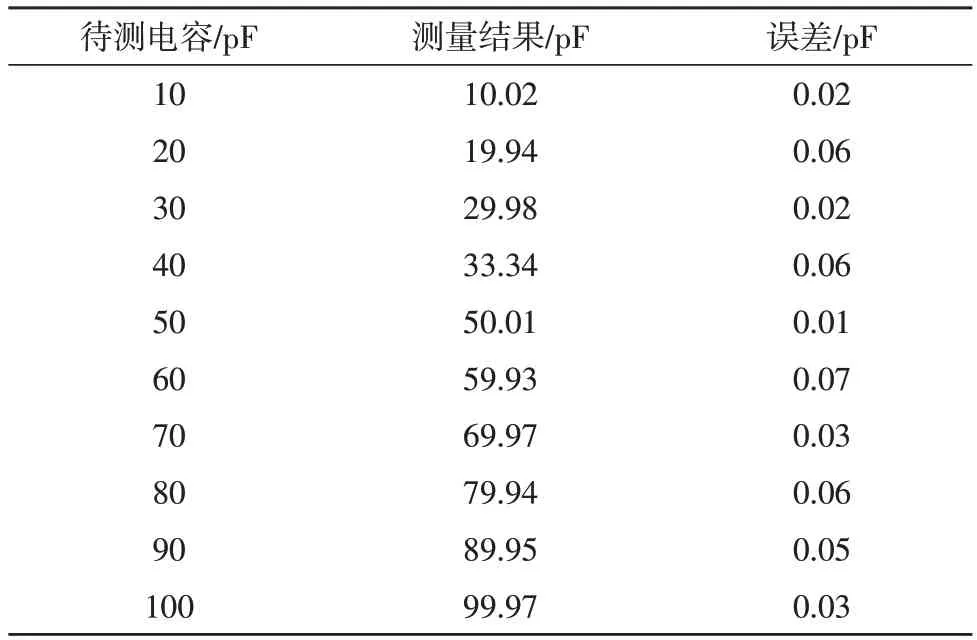

分别用容值不同的贴片电容作为电容读出电路结构中的待测电容。以10 pF 容值的贴片电容开始,每次以10 pF 递增,分别记录基于FPGA 频率转数字电路在测量10~100 pF 的贴片电容输出数据,如表2所示。

表2 电容测量结果与误差

从表2 中不难看出,文中所设计的基于FPGA 的高分辨率电容检测系统测量误差均在0.1 pF 以下,并且平均误差约为0.04 pF,满足大部分微小电容的测量场景需求。

4.3 性能对比

通过FPGA 的工程开发流程方式,选用XC7A35TICSG324 型号的FPGA 芯片进行综合与布局布线。资源消耗与分辨率对比如表3 所示。其中,文献[15]是基于游标卡尺法设计的TDC,因此文中设计相比于文献[15],在资源消耗上有所增加,但是文中对于脉冲信号持续时间的检测分辨率比文献[16]高,而且文中所设计的TDC 未用到PLL 资源。文献[16]对于信号高电平持续时间的检测分辨率要比文中设计高,但是其资源消耗较高。

表3 资源消耗与分辨率对比

文献[15-16]均未说明脉冲宽度检测量程的大小,在不能保证量程的情况下对输入的脉冲宽度进行检测会导致数据读出错误。文中所设计的基于延迟链内插法TDC 可检测2 s 之内的信号高电平持续时间,并且在保持测量范围的同时,将测量电路的分辨率从10 ns 提高到114 ps,并且占用资源适中,适用于测量电路的集成化开发。

5 结论

文中面向微小电容的检测提出一种基于FPGA的高分辨率电容检测系统方案,测量误差均在0.1 pF 以下,并且平均误差约为0.04 pF。针对现有电路的脉冲信号时间间隔测量分辨率低的问题,提出了一种基于延迟链内插法的时间转数字电路,在保证系统测量量程的同时提高了测量分辨率。对整个FPGA 系统进行了时序仿真,仿真结果显示分辨率在114 ps 之内,并且测量范围为2 s 之内,后续可以作为芯片原型,启动ASIC 设计。