基于高密度计算的多核处理器电力芯片低功耗设计系统

匡晓云,黄开天,杨祎巍

(南方电网科学研究院,广东 广州 510663)

电子系统结构不断向复杂化、一体化发展,电子系统设计技术的困难程度不断提升。在多核处理系统应用前,数据高速计算与复杂性功能操作无法有效结合,多核处理技术为此提供了相应的解决方案,并成为构建高性能处理器的重要手段。

不少研究学者针对多核处理器电力芯片低功耗特征进行系统设计,文献[1]综合叙述多核处理器芯片的功能及特点,应用不同的芯片处理技术调整芯片的安装参数,加强整体系统处理,构建多核架构,根据芯片的动态功率峰值分析芯片能耗,在研究处理器与芯片相关性的基础上记录能耗信息,有效获取系统设计数据,但获取的参数可靠性较低。文献[2]分析了多核处理器连接口处的芯片系统设计特征,通过数据直传端口解析芯片存储器结构,提出具有自主共享功能的系统设计操作。在阐述系统接口的不同协议层功能后构建芯片能耗模拟平台,有效获取芯片低能耗数据,验证整体系统设计的正确性,实现系统设计测验,但该方法在系统设计的过程中对芯片的结构处理不到位,无法加强系统内部芯片间的联系,影响系统设计的精准度。

为此,针对以上问题,该文设计了一种基于高密度计算的多核处理器电力芯片低功耗系统。

1 多核处理器电力芯片低功耗结构设计

1.1 存储器层次结构设计

多核处理器系统程序操作很大程度上依赖内部存储系统的数据传输性能,为此在进行多核处理器电力芯片低能耗结构设计的初始阶段,需要分析系统内部存储器层次结构设计操作,引入高密度分析,设置存储公式为:

式中,L表示存储参数;y表示系统存储空间数据;P表示存储准则;x表示存储数据数量;Pμ表示涉及本地信息的存储数据;xμ表示经过初始处理的存储数据[3-4]。

根据获取的存储参数调整系统内部存储层次结构,当存储系统收到相应数据信息指令时,将自动发射请求接收指令,同时生成一个请求字段数据块,该数据块内部存储指令会延迟信号。当请求指令无法传输至中心管理系统时,字段数据块将自动发射延迟信号,避免数据输送错误[5]。

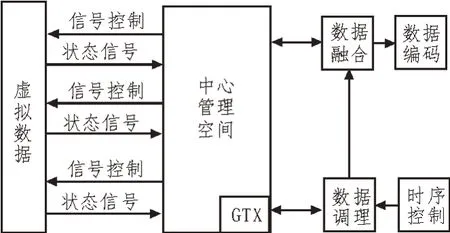

存储器层次结构如图1 所示。

图1 存储器层次结构

观察图1 可知,由于不同传输速度的处理器将影响内部存储系统的数据输送效果,该文设置存储墙阻隔与数据传输信息特征不相符的数据信息,避免因内存性能差异造成的信息存储位置偏差[6-7]。匹配系统中心存储结构与层次结构装置,不断调整主存储器与CPU 寄存器之间的关系参数,改善数据缓存速率,执行外部数据接收传输指令,降低数据冗余程度[8]。若存储空间内部的数据被重复使用,根据多核处理器的数据工作平台调整计算模型,加速信息之间的传递,实现存储器结构层次设计。

1.2 系统控制协处理器单元设计

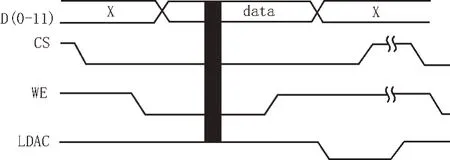

系统控制协处理器单元主控中心为处理器提供所需的指令执行环境,在进行数据传输与控制的过程中调整控制位置,及时转化数据编码,将无关数据隔离在主系统外,避免无关数据对处理器单元设计的影响。处理器结构如图2 所示。

图2 处理器结构

观察图2 可知,处理器在将虚拟数据地址转换为实际数据控制地址后访问中心管理空间,向主线单元发射系统控制信号,访问内部数据传输轨迹[9]。

当处理器同时选用频率固定的警报系统时,通常选取程序执行性能衡量公式检验处理器的控制性能,其公式如下:

式中,K表示处理器控制性能数据;CPI表示指令警报装置的响应周期;f表示装置响应频率;d表示系统控制总时长[10-11]。

在系统控制协处理器中流水线装置负责控制信号收发操作,系统内寄存器将收集的信号输出为物理地址并转存至处理器内部,在输入额定电力芯片数值后分析信号来源,追踪来源通道的信号发射位置,完成处理器设计[12]。

1.3 AHB 总线与时序

AHB 总线系统主要由主从模块和控制选择模块构成,不同的模块对应多核处理器内部的不同子处理系统[13-14]。主模块通过系统内部总线发出读写控制信号,从模块接收控制信号并响应数据信息。由于相同时刻只能存在一种总线模块,为此在进行数据传输的过程中需加强对模块数据传输的调整力度,加强主模块对设备的总体控制权,构建模块控制公式:

控制选择模块主要由译码器和仲裁器构成,仲裁器根据指定的仲裁标准判断不同设备发出的总线控制请求,主系统对设备具有优先控制权。译码器对收集的数据地址进行翻译,同时根据传输的数据线路复刻数据编码,通过高密度处理得到的时序图如图3 所示。

图3 时序图

在接收到仲裁器发出的请求信号后,AHB 总线将自动访问设备状态,并从系统主模块中分配响应请求,AHB 能够一次性完整传输两个不同阶段的相应指令,在数据地址控制区域,主模块根据数据地址的信息进行数据采样,同时在数据段拓展信号发射模式,有效解决长周期数据处理问题,形成AHB 总线处理模式,为系统数据周转提供充足的时间响应[15]。

2 多核处理器电力芯片低功耗模型

利用高密度计算技术将多核处理器电力芯片低功耗结构设计数据整合为编码信息,进一步构建芯片低功耗模型。假设多核处理器执行任务的时间为tk,通过高密度计算得到处理器执行完全部任务所需的时间:

由此构建处理器任务执行公式为:

式中,St(m)表示处理器任务执行标准。为了确保处理器电力芯片低功耗模型的处理效率,增加处理器数量,假定需进行处理的任务为单位1,将所有数据分成等待处理的任务指令信息和已经过处理的任务指令信息两部分,改造处理器内部电力芯片功耗模式,建立新的处理器加速公式:

式中,St(m)2表示新的加速参数,a表示电力芯片功耗模式参数[16]。

当多核处理器的数量增加时,系统收集的数据数量也随之增加,将加大系统的任务承载负担,影响整体芯片运行能耗。根据得到的低功耗模型收集加速参数,完成对电力芯片低功耗模型的构建操作。

3 实验研究

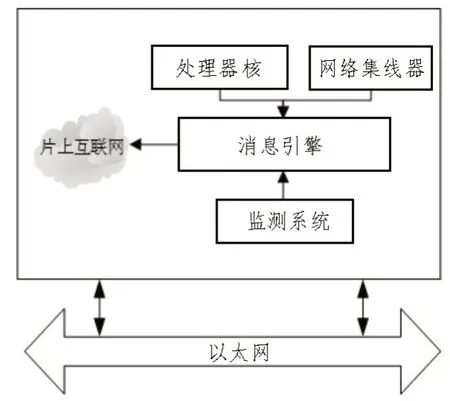

为了验证该文提出的基于高密度计算的多核处理器电力芯片低功耗系统的实际应用效果,设计实验。通过消息引擎、处理器核和片上互联网共同构成电力芯片测试实验环境,具体如图4 所示。

图4 电力芯片测试实验环境

根据图4 可知,消息引起配合监测系统连接互联网,同时连接处理器核和网络集线器。

功耗计算公式如式(7)所示:

式中,P表示得到的功耗;C表示常数;V表示电力芯片工作过程产生的电压;f表示工作过程产生的频率。将给定的任务数据分割为多个不同的子任务区间,调整高密度计算参数,设置相应的持续时间段。在理想状态下将系统发出的信号任务等分成m个子任务区间,在每一个子任务区间内部设置任务执行指令。

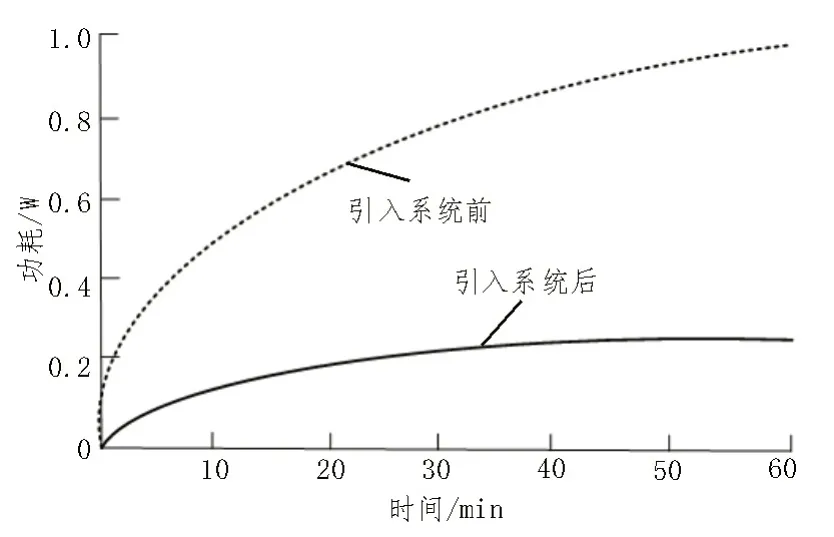

根据上述实验环境,分析不同字节下,对比引入该文设计系统前后多核处理器芯片的功耗,实验结果如图5 所示。

图5 功耗对比实验结果

观察图5 可知,随着时间的增加,芯片产生的功耗越来越高,尤其是到了后期阶段,芯片功耗的上升速率越来越快,当时间为60 min时,产生的功率为0.99 W,芯片很容易产生过热现象,影响整个CPU 的正常运行。引入该文提出的低功耗系统后,多核处理器芯片的功耗大大降低,虽然功耗也会随之升高,但是升高速率极小,当时间为60 min时,产生的功率基本稳定在0.2 W,满足电力芯片正常运行要求,与未引入之前相比,电力芯片功耗减少了60%。由此可见,该文提出的电力芯片低功耗系统具有很强的工作能力,可以有效降低电力芯片运行功耗。

在满载状态和待机状态在平台下的功耗,引入该文系统芯片功耗实验结果如图6 所示。

图6 引入该文系统芯片功耗

观察图6 可以发现,该文提出的系统具有极高的降低功耗能力,对于待机状态和满载状态都有很高的消除功耗能力,在7 种模式下,待机状态的功耗始终低于11 W,满载状态的功耗始终低于50 W。

根据满载状态和待机状态的运行情况,同时对比三种方法的加速比,得到的实验结果如表1 所示。

表1 加速比实验结果

根据表1 可知,该文提出的系统加速比最高,可以达到3.992,系统运行状态最好。

综上所述,该文设计系统可以有效考虑内部芯片结构,进一步提升系统数据来源的可靠性,能够在不同的电子系统环境下执行任务指令,解决系统能耗过大的问题,减少不必要的能源消耗,为后续研究提供数据基础。

4 结束语

文中针对多核处理器电力芯片低功耗特征,基于高密度计算技术进行系统设计,充分考虑多核处理器的电力芯片结构,获取有效的系统设计数据。该文设计的系统在数据传递过程中存在一定的计算偏差,在后续处理中需加强对消息引擎的处理以及对系统负载数据的整合力度,提升系统的应用性能。系统计算模式具有一定的局限性,需进一步扩展计算范围,增强整体系统计算的可靠性,减少数据堆叠现象。