BCD 工艺中大电流下纵向双极晶体管的电流集边效应研究

彭洪,王蕾,谢儒彬,顾祥,李燕妃,洪根深

(中国电子科技集团公司第五十八研究所,江苏无锡 214035)

0 引言

BCD(Bipolar、CMOS、DMOS)工艺是一种同时结合了双极器件、CMOS 器件和DMOS 器件的单片IC制造工艺,其优势是可以将高精度模拟的双极、高集成度的CMOS 和高功率级别的DMOS 自由选择并集成到单片IC 上[1-2]。MOS 器件具有温度稳定性较好、噪声系数小等优点,目前商用BCD 工艺一般将DMOS作为输出管。而双极晶体管是一种电流控制器件,通过控制基区电流来控制输出电流,因此双极晶体管的输出电阻要优于MOS 器件,在一些功率输出电路中得到应用[3-4]。

与其他使用双极型的电路不同的是,集成了双极型功率器件的电路需要在较大输出功率条件下工作同时具有承受较高电流的能力[5-6]。此外,双极型功率晶体管与MOS 器件最大的区别是双极器件既有多子导电,又有少子导电,因此其工作行为较MOS 器件来说更为复杂,随着电流的增大、功率的提高,在低压、低电流工作下未显现出的矛盾将会被放大显现。常规商用BCD 工艺中的双极晶体管一般用于电流开关,所需要的电流为μA 级别,这与大电流下工作的功率三极管所需要的电流相差较大,器件设计也未在大电流下进行优化。而针对功率三极管输出的电路,需要研制可集成的功率双极晶体管。本文基于本单位的BCD工艺平台进行流片,基于BCD 工艺平台开发纵向功率NPN 晶体管,并研究纵向NPN 晶体管在大电流下的发射区结电流集边效应。

1 可集成功率双极晶体管及发射极电流集边效应

1.1 可集成功率双极晶体管

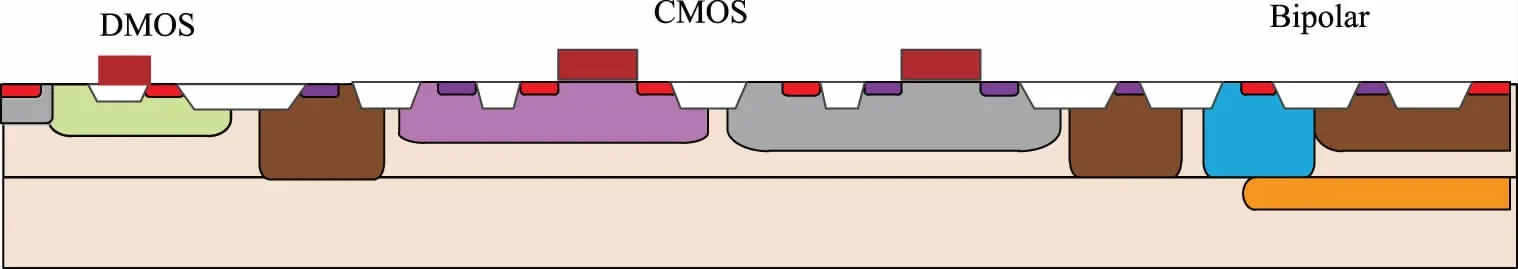

BCD 工艺已广泛地应用在电源电路、LED 驱动等高压电路中,该工艺主要包含了Bipolar、CMOS 和DMOS 器件,BCD 工艺结构剖面如图1 所示。双极晶体管由基极、发射极和集电极组成,其中发射极的掺杂浓度最高,基区的掺杂浓度次之。以NPN 晶体管为例,当集电极电压高于基极电压,且基极电压高于发射极电压时,晶体管将处于放大状态,发射极与基极的PN 结注射过来的空穴可在反偏的集电极与基极的PN 结造成大电流[2,5-7]。

图1 BCD 工艺结构剖面

在集成的功率双极晶体管中,电极都要通过大电流,因此需要降低整个器件电流传输的电阻。在工艺上,集电极部分会采用埋层工艺,先将N 型埋层注入指定的位置,形成集电极的收集区,外延后再通过高浓度注入与埋层连接,形成N 型引出。而在器件设计上,基极、发射极、集电极的设计及引出方式也都会影响最后器件的放大能力,其中在大电流下,发射极的设计较为关键。

1.2 双极晶体管的发射极电流集边效应

发射极电流集边效应是双极晶体管工作时产生的基本物理现象之一[8],其现象总体可概括为,在双极晶体管中存在一定的基极电阻,正偏下的发射结产生的电流在流动中产生了电压降,导致基区各个位置的电位不同[9]。而在大电流输入的情况下,这种现象将会被放大,使得基极电流基本上都集中到了发射结的周围,造成收集效率下降,器件功耗增大[10-12]。

早在1971 年,J.Olemstead 等人建立了描述双极晶体管发射极电流集边效应的微分方程,一直以来不断有研究者对该效应下的微分解进行研究。林鸿生等人提出,在大电流工作条件下,若发射区边缘的电位与发射区中心的电位差低于热电势VT时,此时电流能力主要由发射区的面积决定,有效发射极面积也与版图基本一致[13]。当发射区边缘的基区电位与发射区中心的电势差高于3.31VT时,此时边缘处的电流密度为有效发射宽度处的10 倍,器件的最大电流能力将由发射区面积与发射区有效周长的比值决定,若再进一步加偏压,注入电流将几乎全被边缘极窄的区域吸收,器件的电流能力也将只由发射区周长决定[13-15]。因此,在设计和使用器件的过程中,不能一味地增大基区偏压来提升器件的输出电流,要优化器件结构设计,从而达到最优效果。

2 双极晶体管设计

2.1 大电流下双极晶体管的器件结构及版图设计

商用工艺的双极晶体管一般用图2 所示的环形结构,发射极(E)位于器件的中心,集电极(C)位于最外圈,基极(B)在中间。这种结构的好处在于集电极能够很好地收集载流子,但当需要通过大电流时,发射极面积增大会使得整个器件的面积显著增大,因此环形结构不适合功率双极晶体管。本设计使用条形的发射极和基极叉指交替排列在基区上,在基区外设计一圈集电极用于载流子的收集。

图2 环形双极晶体管

双极晶体管由于存在大电流下的电流集边效应,为了适应电路中双极晶体管大电流的应用,如果只一味地增大发射结面积,输出电流可能并不会显著地增大,并且会占用很大的版图面积。理论研究结果表明,发射极的周长与发射极面积的关系对大电流下的增益有一定影响,即需要增大发射极版图周长与发射极版图面积的比值。在相同发射极面积的情况下,应尽可能地设计细长的结构来降低发射极电流集边效应的影响。

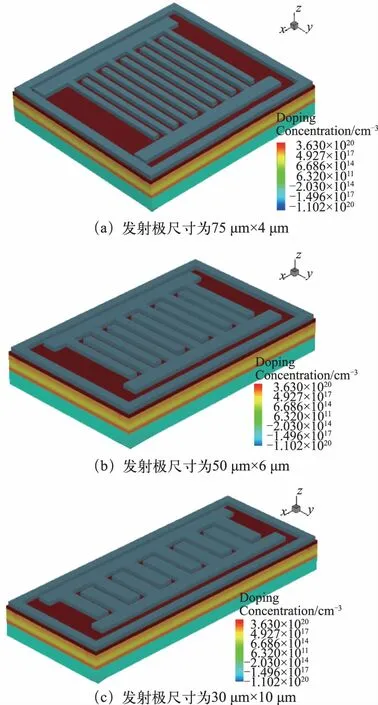

本次流片使用P 型衬底N 型外延材料片,根据工艺能力,设计了75 μm×4 μm、50 μm×6 μm、30 μm×10 μm 三种不同尺寸的发射极,三种版图的周长与面积的数值比分别为0.527∶1、0.373∶1、0.267∶1。

2.2 大电流下双极晶体管的TCAD 仿真研究

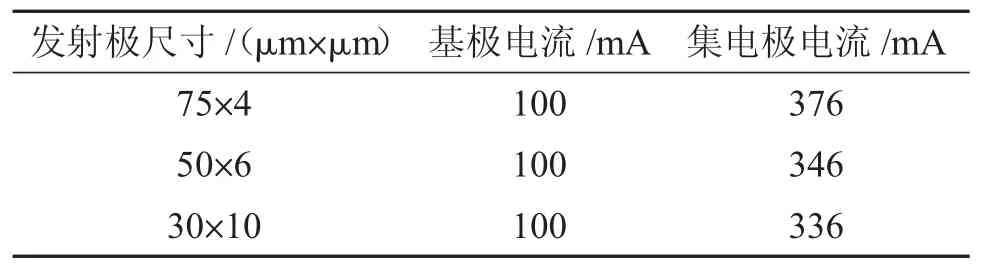

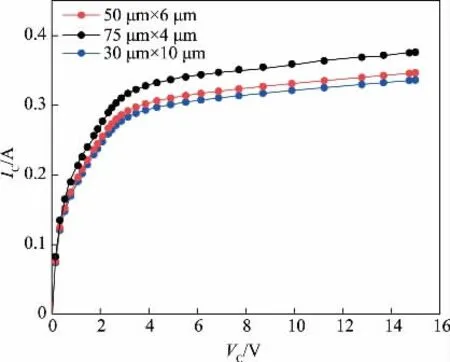

本文使用Sentaurus TCAD 仿真软件对三种不同结构进行SDE 三维器件结构仿真。器件设计目标为工作电压是15 V 的NPN,根据前期器件设计结果,发射极与基极之间的距离为4 μm,集电极距离基区10 μm可满足工作电压为15 V 的需求。SDE 器件建模首先定义P 衬底和N 型外延的厚度与掺杂,再依次对集电极、基区、发射极、基极的位置进行掺杂定义,最后淀积金属并对电极进行定义。NPN 双极晶体管SDE 仿真结构如图3 所示,器件最外围一圈是集电极,用于载流子的收集与引出,中间部分为基区,发射极与基极叉指排列。Sentaurus Device 为高级多维仿真器,能够对器件的电学、热力学以及光学等性能进行仿真。使用Sentaurus Device 对SDE 仿真结构进行电学仿真,设计的三个器件发射极面积一致,在器件的基极加上100 mA 的恒定电流,在集电极上加15 V 的扫描电压,不同发射极尺寸下NPN 双极晶体管放大系数仿真曲线如图4 所示,其中VC为集电极电压,IC为集电极电流,NPN 双极晶体管SDE 仿真结果如表1 所示。

表1 NPN 双极晶体管SDE 仿真结果

图3 NPN 双极晶体管SDE 仿真结构

图4 不同发射极尺寸下NPN 双极晶体管放大系数仿真曲线

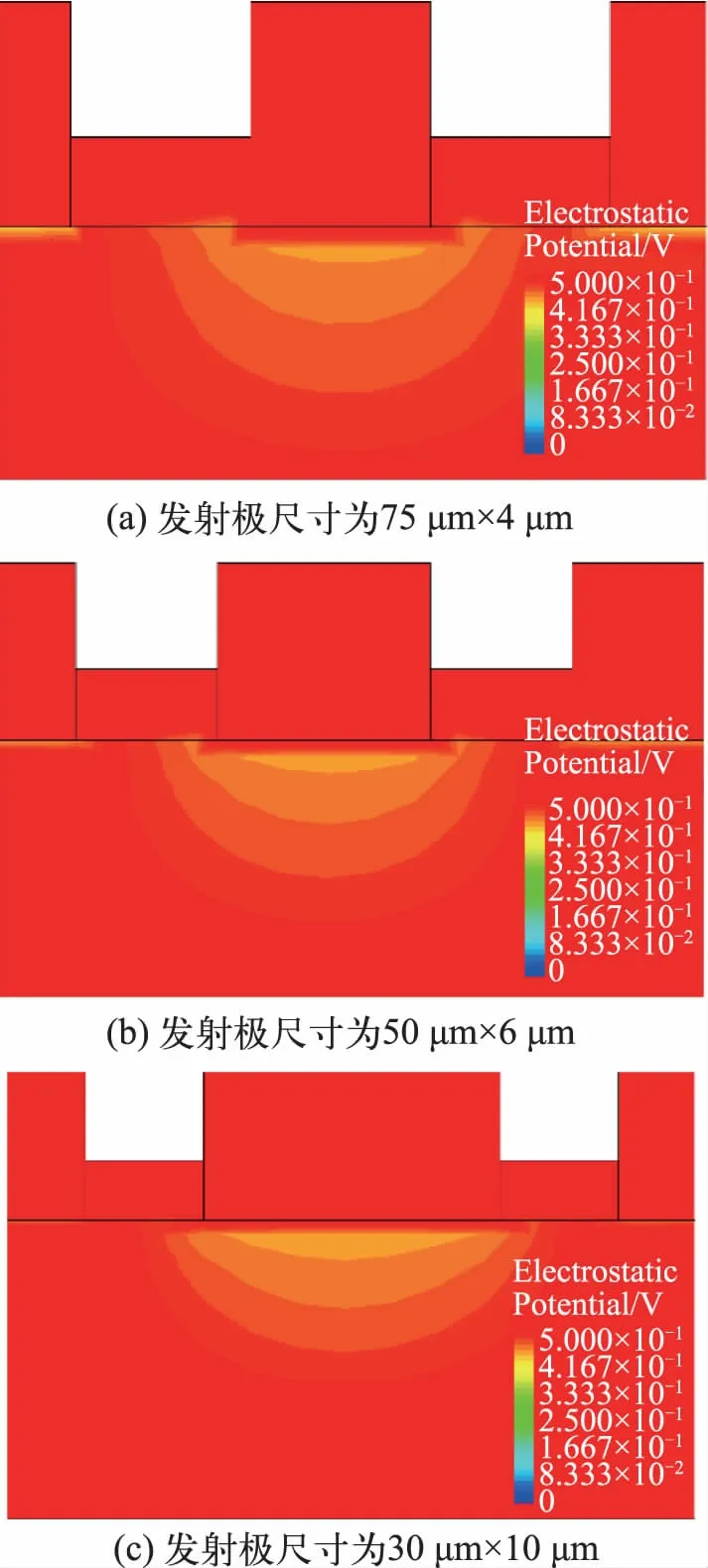

图5 为NPN 双极晶体管仿真电势分布图。Sentaurus Device 的仿真结果显示,在大电流的注入下,发射结下的电势呈现向中间减弱的趋势,当发射极的宽度较小时,电势的分布相对均匀,在发射极下方因基区电阻形成的低场强面积较小。发射极的宽度进一步增大,电势在发射结下方的分布呈现向中心减弱的趋势。当发射极宽度为10 μm 时,发射结中心的电势并没有减少至零,因此在该尺寸状态下的器件发射极有效面积与实际版图面积会有一定程度的减小,但还没有降低太多,进一步增大发射极宽度可能会使得发射极外围的电势进一步降低,参与工作的发射极的有效面积比例进一步降低。

图5 NPN 双极晶体管仿真电势分布

2.3 流片结果讨论

基于TCAD 的仿真结果,双极晶体管在同样的发射极面积下,发射极尺寸为75 μm×4 μm 的结构要优于发射极尺寸为50 μm×6 μm 和30 μm×10 μm 的结构。因此,在实际流片中,将TCAD 仿真建模使用的版图1∶1 放入工具版中进行流片验证。从集成工艺的角度来说,只需要为双极晶体管加一块基区注入专用的光刻版即可,其余光刻版均可与CMOS 和DMOS共用。

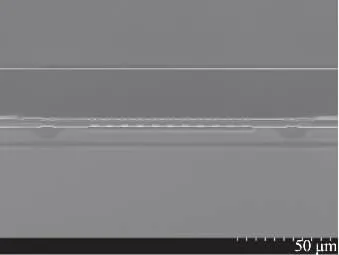

本文基于本单位的BCD 工艺平台流片,并对流片的器件进行测试和解剖分析。图6 为发射极尺寸为75 μm×4 μm 的双极晶体管器件解剖染色图,从图中可以看出集电极的引出、集电极的埋层、基区等注入位置与设计一致,发射极和基极均匀地交叉排列在基区上方,基区下方注入了N 型埋层,器件的集电极N型引出通过与该埋层连接可在基区下方直接收集载流子,降低导通路径上的电阻。

图6 发射极尺寸为75 μm×4 μm 的双极晶体管器件解剖染色图

采用Keysight B1505 半导体参数测试仪并配合半自动探针台对双极晶体管进行电学性能测试。测试条件为发射极使用源/测量单元(SMU)接0 V,基极通过SMU 给予恒定电流,集电极通过SMU 给予0~15 V的扫描电压。NPN 双极晶体管在基极电流为100 mA下的五点测试结果如表2 所示,不同发射极尺寸NPN晶体管放大系数实测曲线如图7 所示。

表2 NPN 双极晶体管实测结果

图7 不同发射极尺寸NPN 晶体管放大系数实测曲线

流片结果显示,圆片内NPN 器件五点分布均匀,性能正常,具有可对比性。在发射极尺寸为75 μm×4 μm 的情况下,器件的性能最优,在100 mA 基极电流下能够得到平均480 mA 的输出电流。随着发射极周长与面积比值的降低,器件的放大能力进一步减弱,在30 μm×10 μm 的发射极尺寸下平均输出电流为425 mA,放大能力降低了约11.4%,降低的原因是发射极宽度的增大导致有效面积减小,该趋势与仿真趋势一致。

3 结论

本文基于本单位的BCD 工艺平台流片,在集成CMOS 与DMOS 的工艺基础上集成了功率输出NPN双极晶体管,与常规商用工艺双极晶体管的环形设计不同的是使用叉指结构的发射极和基极,设计了发射极尺寸分别为75 μm×4 μm、50 μm×6 μm、30 μm×10 μm 的三种不同发射极周长与面积比的版图器件。同时进行TCAD 仿真研究及流片验证,实验结果显示,发射极周长与面积比小会导致发射极电流集边效应的发生,在发射结下方的电势减弱,器件在大电流下的放大能力会降低,三个器件结构在100 mA 下的实测放大倍数分别为4.80、4.61、4.25。在本文设计的器件尺寸仿真中,发射结下方还未出现电势为零的情况,这是由于该工艺下基区浓度较高或者发射极宽度设计还未达到设计的极限。在版图设计中应尽可能地设计周长与面积比大的细长条发射极,从而提升器件在大电流下的放大能力。