晶圆级树脂基低成本W波段封装天线微系统

齐晓琳,崔晶宇,李 霄,张先乐,彭轶瑶,戴 扬,杨 凝

(中国电子科技集团公司信息科学研究院,北京 100049)

0 引 言

W 波段电磁波具有带宽大、波长短、大气损耗低以及能够在多尘和多雾条件下工作等优势,在防撞雷达、成像探测、回程通信等方面具有巨大应用潜力[1-5]。工作在W波段的探测成像和无线通信系统具有更高的分辨率和更高数据传输速率,因此W 波段相控阵封装天线微系统的研究日益增多。封装天线(Antenna-in-Package,AiP)技术将辐射天线与射频收发芯片高密度集成在一个封装体中,可以实现高性能、高集成度的射频前端电子系统。由于毫米波频段电磁波波长短,物理上较短的天线间距使得多层封装互连损耗和阻抗匹配变成挑战,尤其在94 GHz及以上,封装天线对集成工艺、集成度和集成架构要求更为苛刻。此外,为了获得毫米波频段高质量数据传输和远距离成像能力,需要的相控阵单元数量急剧增加,高昂的价格制约了毫米波相控阵微系统在先进雷达系统和通信系统中的发展。近年来,国内外对W 波段射频微系统作了大量研究。2018 年,IBM 公司团队发表了一篇用于雷达成像和通信应用的94 GHz相控阵封装天线,封装天线包括64 个双极化天线单元和4 颗16 通道SiGe 芯片,尺寸为18 mm×18 mm×0.97 mm[6]。2021 年,上海交通大学团队设计了一种94 GHz 高性能、高度紧凑的调频连续波雷达传感器,采用其研发的硅基微机电系统(Micro-Electro-Mechanical System, MEMS)光敏复合膜制造工艺,传感器整体尺寸为60 mm×40 mm×8 mm,重量为78 g[7]。2022年,曹佳等人设计了一款W波段封装天线相控阵微系统模块,该模块采用硅基三维集成的方式将16 个四通道多功能SiGe 芯片与64个天线单元集成在一个微系统中,工作频率为79~81 GHz,EIRP为27 dBm[8]。

硅基芯片在成本、量产能力和集成度方面远优于Ⅲ-Ⅴ族半导体芯片[9],为了满足系统苛刻的尺寸和低成本需求,本文选用硅基互补金属氧化物半导体(Complementary Metal Oxide Semiconductor,CMOS)幅相多功能收发芯片,基于晶圆级树脂基低成本封装工艺开展了W 波段封装天线微系统设计。晶圆级封装通过芯片表面的聚酰亚胺(Polyimide, PI)再布线层(Redistribution Layer,RDL)实现W 波段信号传输,其中工艺限制与传输阻抗之间的不匹配、芯片与封装之间的电磁兼容是设计中的难点。本文通过架构布局设计,采用三维异构集成解决W 波段传输线互连损耗问题以及磁电偶极子天线单元间互耦等问题,并且提高系统电磁兼容性,使封装天线实现了低成本、可扩展、小型化、高集成度、大扫描角等性能。本文在第1 节描述了W 波段AiP 微系统晶圆级三维集成架构与封装工艺流程,第2节对设计的封装天线微系统进行了电磁仿真与性能分析,最后在第3节进行了总结论述。

1 AiP微系统晶圆级扇出封装设计

1.1 三维异构集成架构

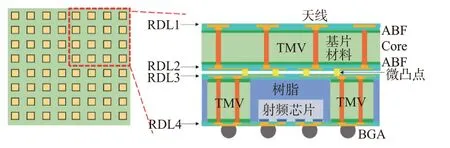

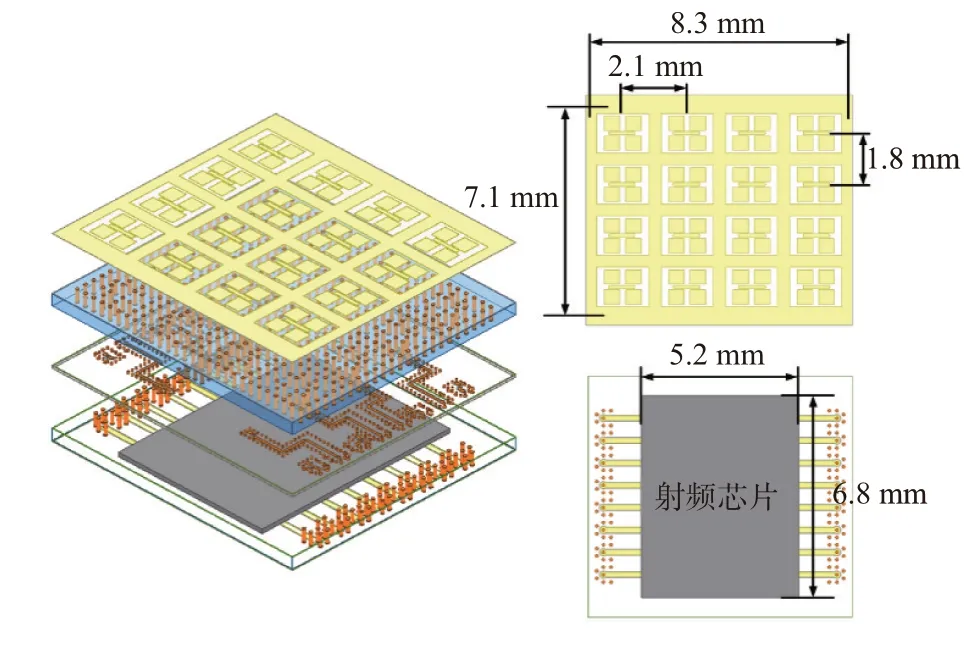

三维异构集成W 波段封装天线微系统整体架构如图1 所示,采用晶圆级树脂基扇出工艺将16通道幅相多功能射频芯片和4×4 磁电偶极子阵列天线集成封装在一个微系统中,形成一个16 单元封装天线子阵。射频芯片选用16 通道CMOS 幅相多功能芯片,单芯片集成上下变频、移相、衰减、放大、电源管理、数字控制等功能,每个通道幅相独立可控。多功能射频芯片的W 波段信号在垂直方向通过树脂金属通孔转接板(Through Molding Via,TMV)和微凸点传输,在水平方向通过再布线层互连传输,实现到天线馈电端口的连接。整个16 单元封装天线子阵的尺寸为7.1 mm×8.3 mm×1.2 mm。

图1 W波段封装天线三维异构集成架构

具体地,W 波段封装天线分为上下两层封装体,即天线层封装体与芯片层封装体。天线层封装体采用的基片材料与TMV 的基片材料相同,基片材料由芯板(Core)介质材料和芳香族苯并环丁烷薄膜(Aromatic Benzocyclobutene Film,ABF)介质材料构成,通过在天线层基片材料表面形成RDL1制作磁电偶极子天线,由TMV与RDL2实现天线单元馈电。其中,采用的Core 介质材料的介电常数为4.2,介质损耗角为0.01,ABF 介质材料的介电常数为3.2,介质损耗角为0.006。芯片层封装体通过树脂材料将多功能射频芯片与TMV 芯片进行晶圆重构,采用晶圆级扇出工艺将芯片的W 波段信号通过RDL4与两端的TMV互连,并向上传输到晶圆背面RDL3,再经微凸点与天线层封装体馈电口(即RDL2)连接。W 波段信号传输过程中不经过多功能射频芯片表面,从而避免对芯片内部产生电磁干扰。芯片层封装体中TMV采用的Core介质材料的有效介电常数接近于塑封树脂材料,不易激励高次模。

1.2 晶圆级扇出工艺流程

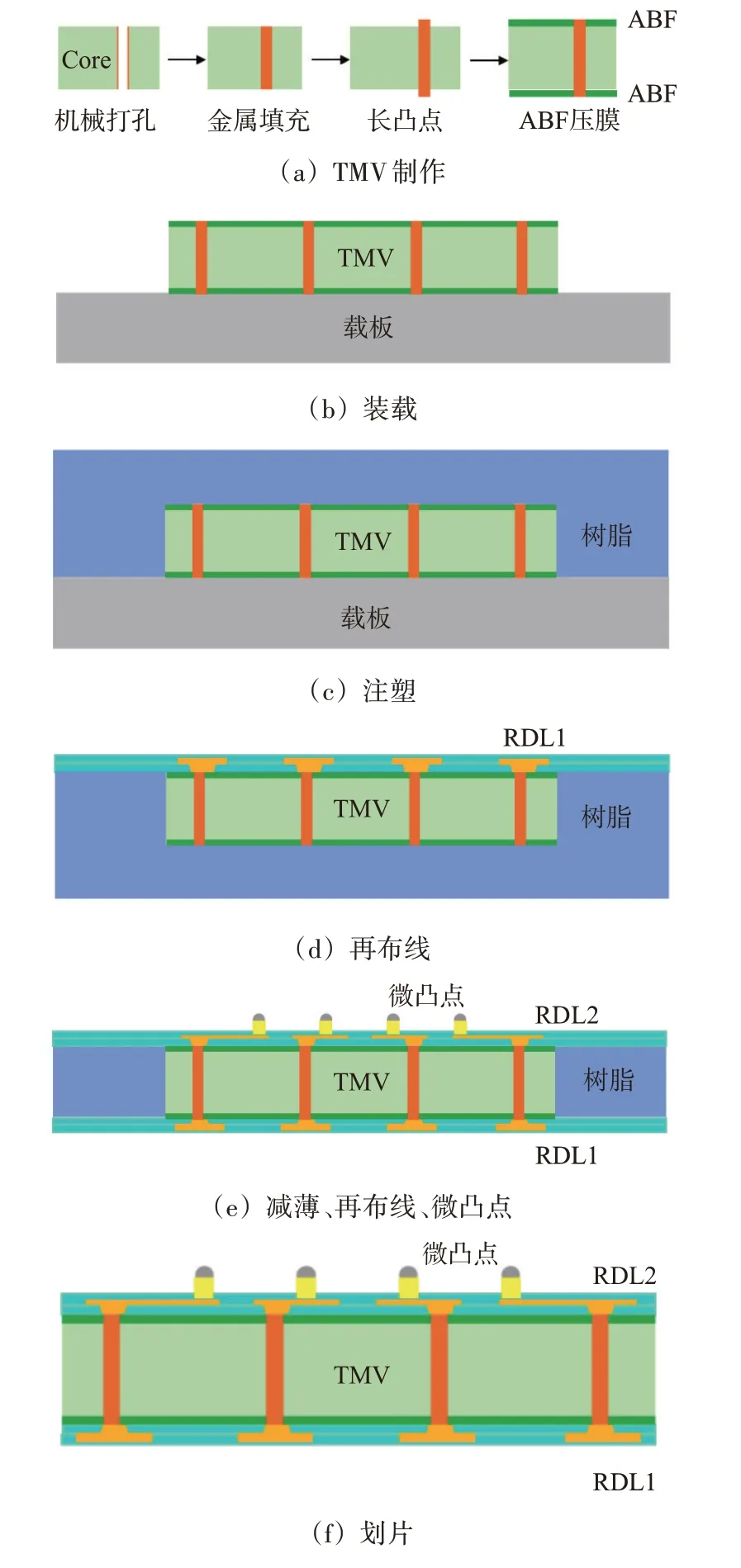

本文设计的W 波段封装天线是在圆片后道封装工艺平台上进行制造和加工,涉及再布线、凸点制备、重构圆片、高精度堆叠等工艺。天线层封装体的工艺流程如图2所示,采用晶圆级再布线工艺实现。(a)首先,进行TMV 制作。在机械强度较高的420 μm 厚的树脂晶圆Core 介质材料上通过机械打孔的方式,形成TMV 通孔。再使用电镀铜工艺,实现小孔金属填充。在晶圆的正反表面长好Cu凸点,使用ABF压膜工艺,在晶圆的正反表面压膜,并固化成型,再减薄晶圆的正反面,露出凸点,减薄后的ABF膜厚度约为20 μm。(b)将晶圆划片,把切好的TMV 芯片放置在载板上。(c)采用环氧塑封材料树脂将TMV 芯片注塑封装形成12 英寸的重构晶圆。(d)将重构晶圆从载板上释放,使用RDL 再布线工艺,在树脂晶圆的正表面形成RDL1制造磁电偶极天线。(e)将晶圆减薄至440 μm,以暴露TMV 金属,翻转晶圆在晶圆背面形成RDL2,在RDL2 的外引出端处长好Cu 柱Sn 帽凸点,即微凸点。(f)最后,对晶圆进行划片形成4×4 的天线阵列,即天线层封装体。

图2 天线层封装体工艺流程

芯片层封装体的工艺流程如图3所示,采用埋置通孔转接板晶圆级扇出型封装方案。首先通过上述工艺方案形成TMV,划成单颗转接芯片备用。(a)使用高精度装片机将TMV 转接芯片和多功能射频芯片装至载板上。(b)采用12英寸晶圆级注塑机重构形成树脂晶圆。(c)将重构晶圆从载板上释放,反转晶圆并在晶圆表面形成多层RDL4 和保护层。(d)反转晶圆并减薄树脂晶圆背面,露出TMV转接板的Cu凸点,再次使用再布线工艺,在树脂晶圆背面形成多层RDL3。(e)反转树脂晶圆去除保护层并露出Cu凸点,划片完成芯片层封装体封装。

图3 芯片层封装体工艺流程

最后,使用高精度堆叠工艺和热压焊工艺将天线层封装体与芯片层封装体进行堆叠键合,并使用单芯片植球工艺,在芯片层封装体RDL4 的外引出端处植上BGA 焊球,完成W 波段封装天线子阵集成封装,工艺流程如图4 所示。综上,整个工艺方案采用晶圆级树脂基封装流片方式,三维集成密度高、尺寸小、制造周期快并且适用于批量生产。采用埋置TMV 转接板的扇出集成相比基于硅通孔(Through Silicon Via,TSV)转接板的硅基三维集成具有成本优势。采用小模块化集成方式,易于与其他封装模块进行二次集成,可拓展性更高。

图4 封装天线装配工艺流程

2 仿真与分析

2.1 射频互连传输结构仿真

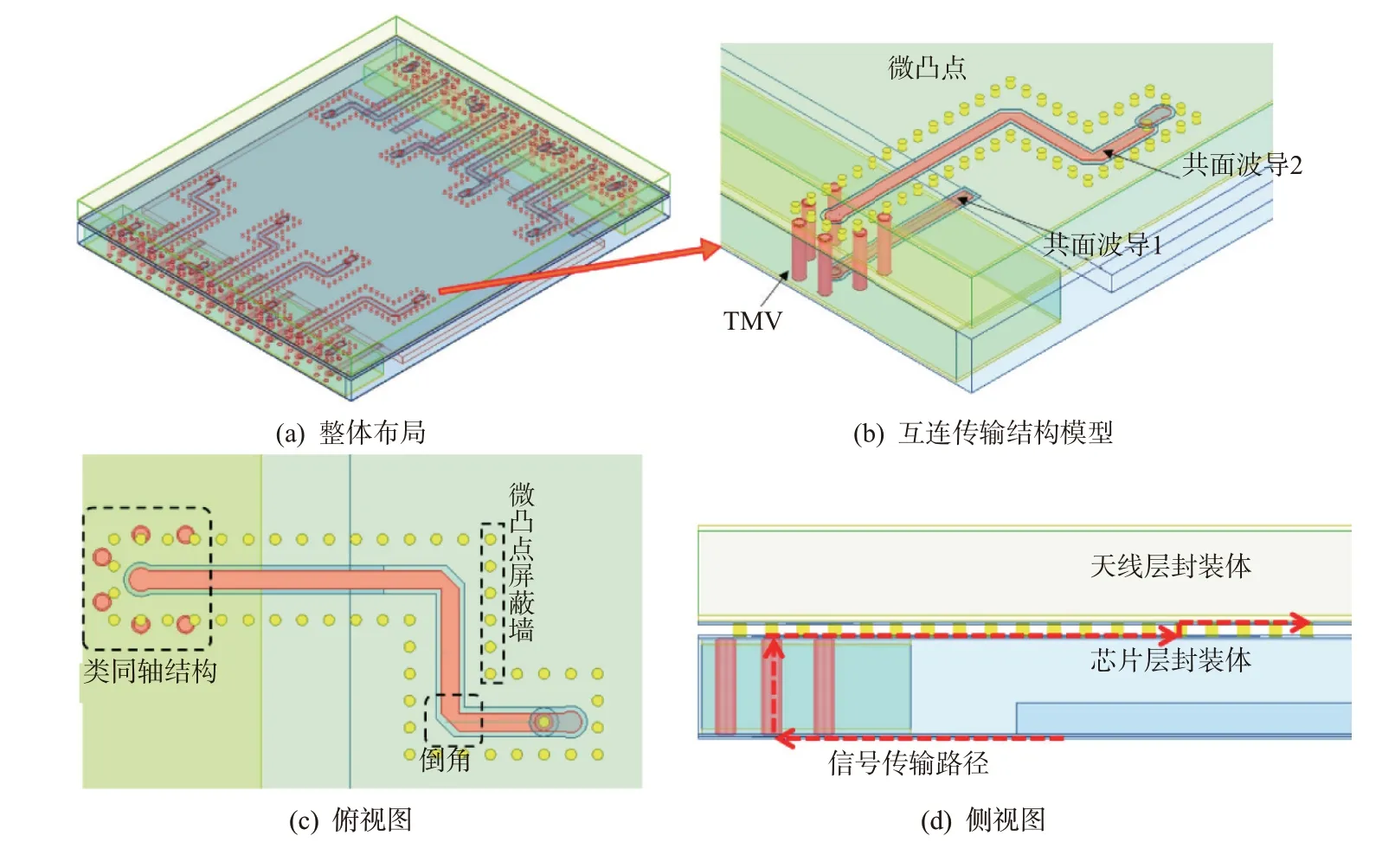

天线与芯片之间的高频低损耗互连是封装天线技术的一大挑战,因此在封装架构设计中,需要综合考虑W 波段信号的传输。考虑实际晶圆级封装工艺能力以及多功能射频芯片电磁性能,本文利用TMV 构成类同轴传输结构实现射频信号的垂直传输,通过共面波导传输线实现射频信号的横向传输。整个封装体从芯片引出端口到天线馈电端口所涉及的W波段互连传输结构示意图如图5所示。

图5 W波段互连传输结构示意图

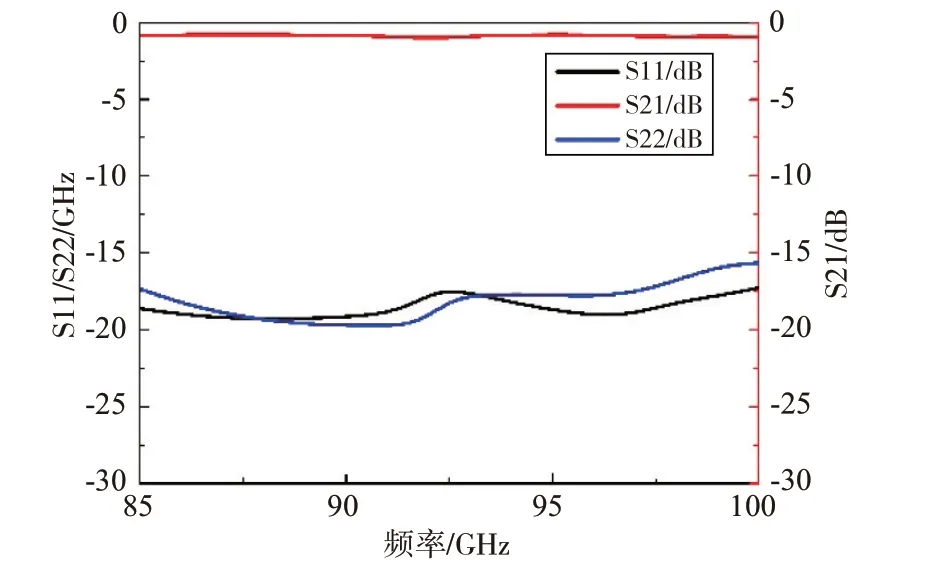

多功能射频芯片W 波段端口信号通过共面波导1 传输线扇出,经过TMV 类同轴传输到芯片背面共面波导2传输线,再通过微凸点传输到天线层封装体馈电口。选其中一条互连传输结构进行分析,在传输过程中需要考虑阻抗匹配,因此TMV 采用类同轴结构,过孔直径为60 μm,中心TMV 与外围TMV 间距为250 μm。芯片层封装体上层共面波导传输线两侧通过微凸点建立屏蔽墙,以减小互连传输结构间的相互串扰问题。共面波导直角过弯处采用45°倒角,避免产生额外的寄生电容和寄生电感。通过优化共面波导传输线和类同轴结构,最终S参数仿真结果如图6所示,可以得到在85~100 GHz范围内,两个端口反射系数均满足<-15 dB,最大传输过渡损耗<1.28 dB。除射频信号外的控制信号、电源信号和地信号通过RDL4 互连扇入,通过接BGA球引出到母板。

图6 W波段互连传输结构仿真结果

2.2 相控阵封装天线仿真

相控阵封装天线结构示意图如图7所示,天线单元采用磁电偶极天线来实现线极化,天线阵面采用矩形栅格排布形式。天线单元与单元之间加入金属通孔抑制单元间耦合,以实现较好的扫描性能。幅相多功能射频芯片尺寸为5.2 mm×6.8 mm,天线单元的尺寸为1.25 mm×1.25 mm,相邻天线单元横向和纵向间距分别为2.1 mm和1.8 mm。

图7 相控阵封装天线结构示意图

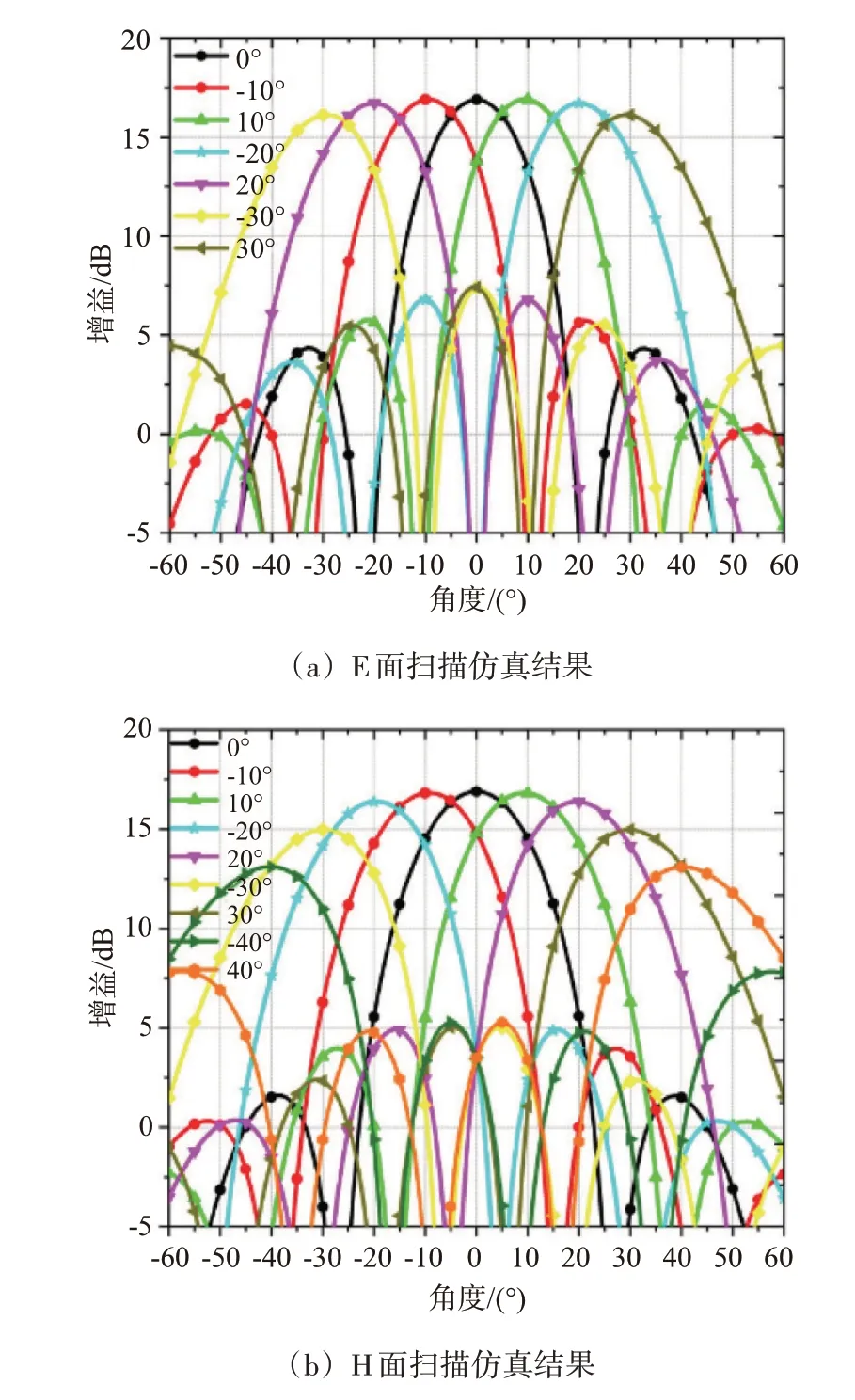

在94 GHz 频率下,相控阵封装天线E 面和H面波束扫描仿真结果如图8所示,随着馈电相位差增加,主瓣增益下降,栅副瓣明显,阵列天线可以实现E面的扫描范围≥±30°,H面扫描范围≥±40°。

图8 相控阵封装天线E面和H面波束扫描方向图仿真结果

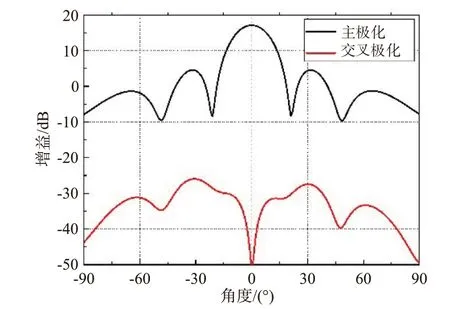

图9 所示,通过HFSS 仿真可以得到4×4 磁电偶极子阵列天线增益为17.1 dBi,其中已包含传输路径损耗。封装天线所采用16通道幅相变频一体多功能芯片的工作频率为91~95 GHz,单通道饱和输出功率为10 dBm,发射转换增益≥30 dB,接收转换增益≥25 dB。根据等效全向辐射功率的计算公式:

图9 相控阵封装天线增益仿真结果

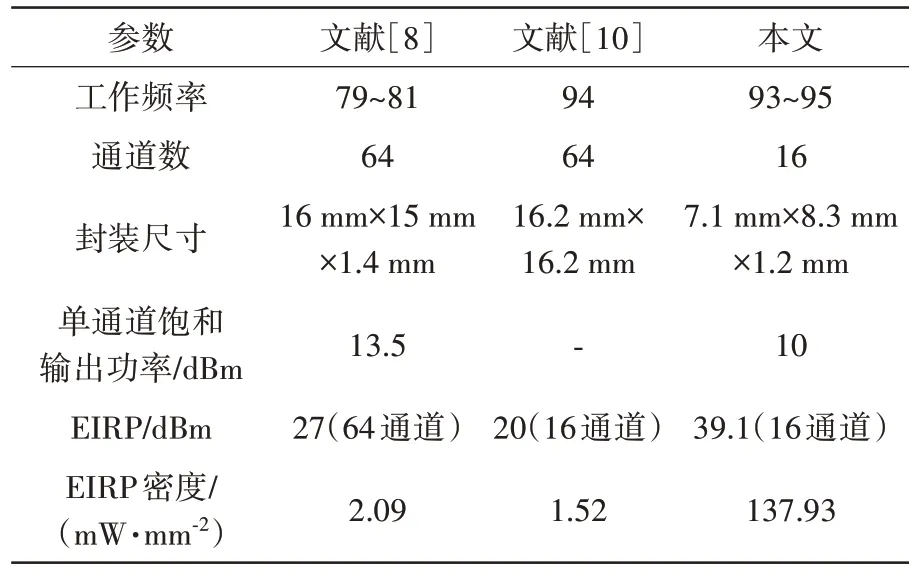

可以得出4×4磁电偶极子封装天线EIRP为39.1 dBm。其中,Pt为发射机输出功率,Gt为天线增益,Lc为传输路径损耗。W 波段封装天线微系统对整机系统能力贡献主要体现在等效辐射功率以及扫描范围(受限于封装尺寸),因此本文以单位面积(1 mm2)内的EIRP 密度为衡量指标,本文设计的封装天线微系统的等效辐射功率密度达到137.93 mW∕mm2,相较于文献[8]提升约60倍,相较于文献[10]提升约90倍,封装天线性能对比如表1所示。

表1 W波段封装天线微系统对比

3 结束语

本文介绍了W 波段封装天线微系统的集成架构、互连传输结构和磁电偶极子天线阵列的设计与仿真,该微系统具有高集成度、高性能、低成本和可扩展的技术优势。多单元天线与多通道芯片的一体化封装可以很好地满足射频前端密布阵设计要求,可广泛适用于孔径受限和载荷重量受限的小型无人平台,满足其对高分辨率成像、微小尺寸障碍物感知以及高速率隐蔽通信的应用需求。