Chiplet技术推动半导体产业可持续发展的研究

张志伟,冯明宪,田 果,王世权

(1.日月新(苏州)半导体有限公司,江苏 苏州 215000;2.厦门大学,福建 厦门 361005;3.亚太芯谷科技研究院(香港)有限公司,香港 999077)

0 引言

随着科技的进步,半导体产业在全球数位化中扮演重要角色,然而莫尔定律的发展面临瓶颈。在此情况下,本文将研究焦点投向Chiplet技术。此技术组合不同功能的半导体晶片,形成整体高效能、低功耗系统。相比传统单晶片设计,Chiplet可提升整体效能,降低成本与能源消耗。该技术利用模组化设计,具有灵活性,为半导体设计领域创造了新视角。

1 Chiplet技术的概述

1.1 Chiplet技术的起源和发展

Chiplet技术的起源可以追溯到20世纪90年代的多晶片模块和系统封装技术。当时的技术限制了这些尝试的可行性,而现代的Chiplet技术则利用了先进的封装技术和自动化设计工具,如3D堆叠和互连技术,以及新型的内部互联网。Chiplet技术自2010年以来得到了快速的发展,并且已经被AMD的Zen和Zen 2微架构以及Intel的Foveros 3D堆叠技术所采用[1]。

1.2 Chiplet技术的工作原理

Chiplet技术将多个Chiplet在共享基础上组合和互联,包含CPU、GPU记忆体、硬体加速器等。每个Chiplet可选用合适的制程技术和设计,实现单一系统中多样制程和设计。这些Chiplet可分别用于不同制程技术,经高速互连物理连接,构成功能完整的大型集成系统,以下为Chiplet技术关键特征。

(1)模块化设计:在Chiplet架构中,整个芯片系统被划分为多个独立但协同工作的模块,每个模块被称为一个Chiplet。这些Chiplet可以是处理器核心、缓存、内存、I/O接口等不同功能的模块。

(2)独立生产:每个Chiplet可以根据其功能和性能要求,在最适合的制程技术上进行独立生产。这意味着不需要将整个大型芯片在单一的制程上生产,从而降低了生产复杂性和成本。

(3)灵活组合:根据需要,设计人员可以灵活地组合不同种类和数量的Chiplet,以实现特定的系统性能和功能要求。

(4)优化生产良率:由于Chiplet较小且可以在不同的制程上生产,它们的生产良率通常较高,且单个Chiplet的生产成本较低。如果一个Chiplet出现缺陷,只需替换这个有缺陷的Chiplet,而不是整个大型芯片。

(5)高速互连技术:Chiplet之间通过高速、低延迟的互连技术(如AMD的Infinity Fabric、Intel的EMIB等)连接在一起。这些互连技术允许Chiplets之间高效、紧密地通信。

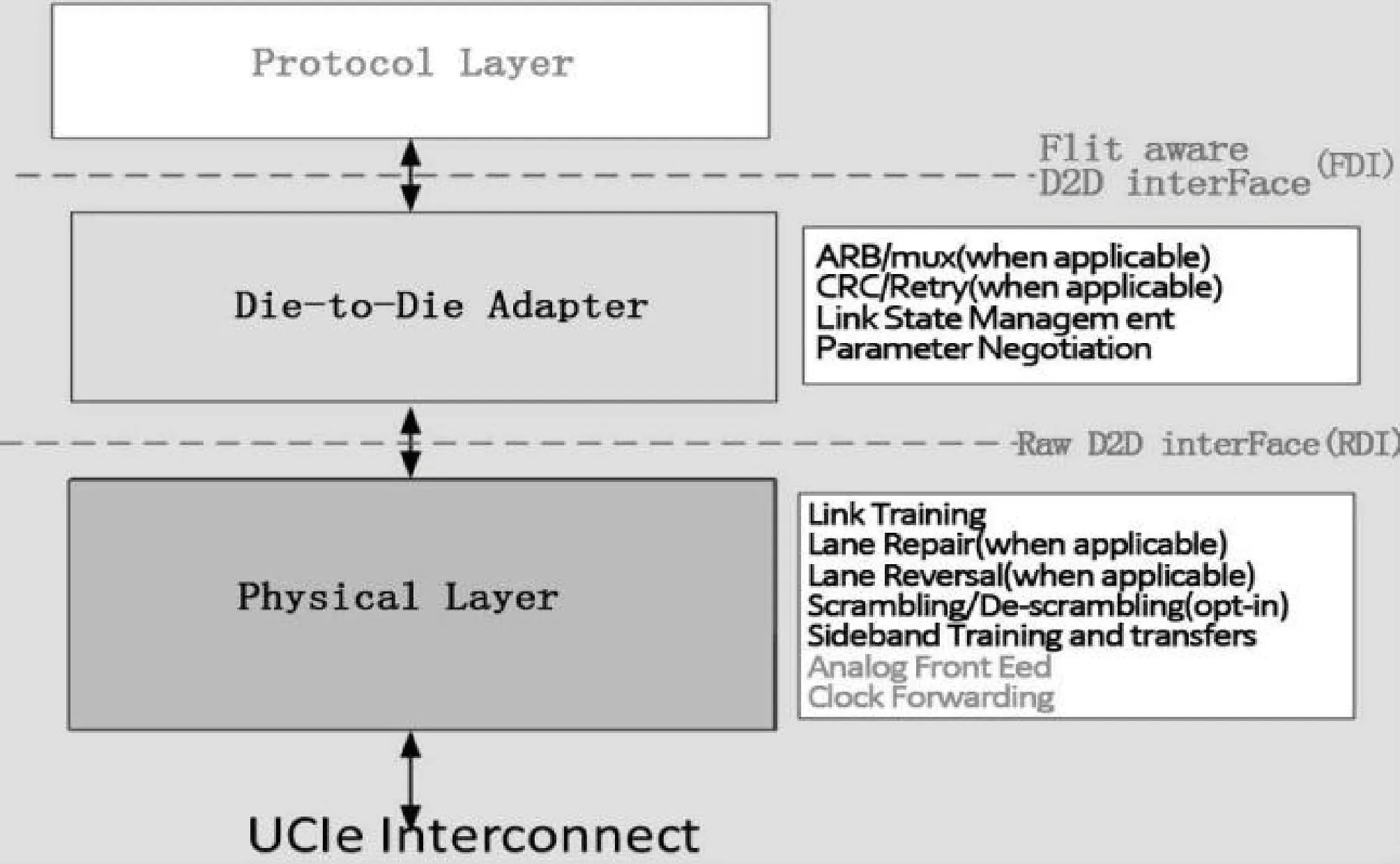

其中,UCIe是一个分层协议,如图1所示。物理层负责电信号、时钟、链路等,Die-to-Die适配器管理芯粒链路状态和参数。

图1 UCIe分层方法和不同的封装选择

(6)快速迭代和升级:Chiplet架构使设计更易迭代和升级。例如,通过替换或添加新的Chiplet,无需重新设计整个芯片系统。Chiplet技术令芯片设计更模块化和更高灵活性,同时降低了生产成本、复杂性,促使更有效地利用不同的制程技术。在摩尔定律减缓和半导体制程进展更难应对的环境下,这一点显得尤为重要[2]。

1.3 Chiplet技术与传统单晶片设计的比较

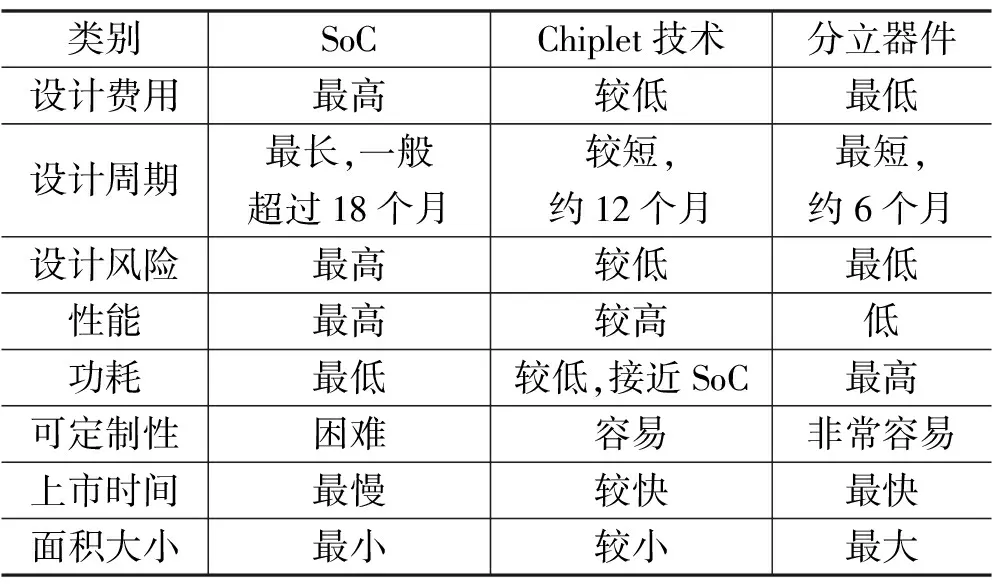

Chiplet技术与传统单晶片设计有关键差异。首先,Chiplet设计赋予高制程和灵活性设计,一个封装可组合多种制程和设计。其次,单独制造、测试Chiplet,可能提供更高产量和低成本。最后,充分晶片区域利用,可能带来更高性能及能效[3]。Chilet技术、SoC和分立器件的优缺点比较如表1所示。

表1 Chiplet技术、SoC和分立器件的优缺点对比

2 半导体产业的现状与挑战

2.1 全球半导体产业现状

半导体产业是全球科技的核心,对经济和社会影响显著。但技术进步和市场演变带来新挑战。首先,摩尔定律极限显现。传统提升晶体管密度、降低功耗的难度递增,尺寸接近原子水平,制程复杂。其次,多样化的市场需求增加了设计难度。用户关注性能、功耗、安全、成本,需定制解决方案,增加了设计难度。据数据统计,2023年全球半导体市场规模约6 000亿美元,以记忆体和逻辑芯片居首。亚洲(中国、韩国)是重要制造中心,美欧在关键领域保持领先(先进制程、设计工具)。

2.2 半导体产业面临的挑战

半导体产业面临的主要挑战包括技术和市场2个方面:技术挑战主要来自摩尔定律的减缓(如图2所示)。摩尔定律(Moore’s Law)于1965年首次提出,一直是半导体产业不断进步的驱动力。它曾预测:集成电路上的晶体管数量大约每2年翻倍。然而,随着工艺技术逐渐接近物理极限,继续遵循摩尔定律变得越来越具有挑战性。晶体管尺寸的持续缩小带来了能耗、散热和制程复杂性等问题。新的技术和应用(如AI和5G)也对半导体设计和制程提出了新的要求。市场挑战则来自全球供应链的不稳定性以及竞争和规模经济的压力。

2.3 Chiplet技术对半导体产业的可能影响

Chiplet(小芯片)是搭积木式的芯片构建,由满足特定功能的模块芯片(Die)组成。采用Die-to-Die互联技术,与底层基础芯片封装,形成多功能异构SiPs芯片。它可集成第三方芯片(如I/O、存储、NPU),周期短、成本低。Chiplet技术应对摩尔定律减速,采用一封装多技术设计。改变供应链,带来模块化设计、定制化市场。待解决的问题:(1)器件缩减难题,摩尔定律限制。(2)先进制程高设计成本。(3)多样化高性能芯片市场需求。

3 Chiplet技术推动半导体产业的可持续发展

近年来,Chiplet技术提供了一种新的方法来制造和组装高效能和高复杂度的微处理器,并且可以解决诸多传统微处理器设计所面临的问题。

3.1 Chiplet提高制程效率和能源效率

Chiplet可以将大微处理器分割为小部分以提高制程效率。首先,制造小Chiplet比大微处理器更容易,且能降低缺陷率。其次,不同的Chiplet可以更灵活地使用先进技术。最后,Chiplet技术,如硅通孔(Through Silicon Via,TSV)与重布线层(Repistribution Layer,RDL),还可以减少连接路径、降低能耗、提高能源利用效率[4],硅通孔立体集成如图3所示。

图3 硅通孔立体集成

3.2 Chiplet推动产业创新

Chiplet可提供高灵活性和扩展性,能推动产业创新和经济增长。一方面,加速产品开发,降低成本;另一方面,创造新的商业模式和市场,如模块设计和定制解决方案。

3.3 Chiplet“小芯片”设计将是延续摩尔定律的关键

Chiplet是硅片级别的重用概念。从系统出发,分解复杂功能,开发单一特定功能的裸芯片,如数据存储、计算、信号处理,模块化组装构建Chiplet网络。可提供延续电晶体数量方法,如TSMC的5 μm工艺,1 Wafer制约数十亿电晶体。NVIDIA的Ampere架构,7 μm制程,约5 400亿电晶体。AMD的RDNA 2架构,7 μm制程,约264亿电晶体。Apple的M1芯片,5 μm制程,约163亿电晶体。Chiplet能延续摩尔定律。

4 实例研究

这一部分将探讨如何在真实世界中应用Chiplet技术,通过对AMD和Intel2家公司实施Chiplet技术的案例进行深入研究,并分析该技术对企业和半导体产业的影响。

4.1 企业案例

AMD是Chiplet技术的早期领先者之一。自2017年以来,AMD开始在其Zen架构中使用Chiplet设计。例如,在AMD的Ryzen 3000系列中,通过使用Chiplet设计,AMD成功地在一个微处理器中整合了多个处理器核心和一个I/O芯片。这使得AMD能够灵活地混合和匹配不同的芯片,提高了设计效率和性能。Intel在2019年提出了Foveros 3D封装技术,它可以将多个Chiplet叠加在一起,从而在更小的空间内实现更大的计算能力。例如,Intel的Lakefield处理器就使用了Foveros技术,将多个Chiplet封装在一起,包括一个高性能核心和4个高效能核心。

4.2 Chiplet技术对半导体产业的影响分析

Chiplet技术已经对AMD和Intel等企业产生了显著的影响。首先,该技术提高了设计和制造的效率,使得这些企业能够更快地开发出新产品,并且降低了制造成本。其次,提供了更高的性能和能效,使得这些企业的产品更具竞争力。最后,创造了新的市场机会,例如模块化的硬件设计和客户定制的解决方案。

5 前景展望

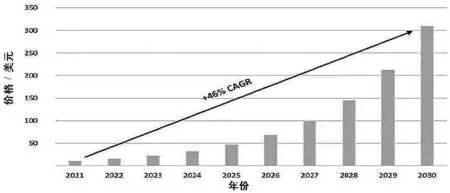

随着技术的发展,Chiplet技术将在未来的半导体产业中扮演越来越重要的角色。Chiplet技术将会得到更广泛应用,并进一步推动半导体产业的发展。以AI产业为例,AI芯片到2030年预计年复合增长率为46%(见图4)。

图4 人工智能芯片市场

新一代GPT-5模型预计需要1万~5万个英伟达H100芯片。早期AI模型用A100芯片:GPT-4约需1万~2.5万个H100芯片。目前对生成式AI的需求大增,估计各大公司需约43万个H100芯片,约为前一代需求量的10倍。

6 结语

Chiplet技术与传统H100芯片单晶片设计相比,具有更高的制程和设计灵活性,可提供更高的产量和成本效益。它允许在同一封装中组合多种不同的制程和设计,从而能够更有效地利用晶片区域,达到更高的性能和能效。

全球半导体产业面临技术和市场挑战:摩尔定律减缓,晶体管尺寸难以缩小;市场多样性和供应链不稳定。在此背景下,Chiplet技术将深刻影响产业发展。它能有效应对摩尔定律,提供灵活的模块设计,满足多样化市场需求。Chiplet技术能够推动半导体产业可持续发展、提高制程和能效、促进创新和经济增长、缩短产品开发周期、降低成本、创新商业模式、加速产业更新。

AMD和Intel是该技术的先驱者,已成功将Chiplet技术应用于产品设计并取得了良好效果,这进一步证实了Chiplet技术的潜力和优势。随着半导体产业的发展,Chiplet技术必将会提供更高的制程效率、灵活设计和竞争力。