面向时隙光交换网络的纳秒级时间同步技术

丁 蕊,党导航,郭元之,薛旭伟,郭秉礼,黄善国(北京邮电大学,北京 100876)

1 概述

随着互联网的普及和通信服务的快速发展,流媒体、云计算等相关应用业务对数据流量的需求增加,数据中心组网的规模不断扩大,高密度服务器之间的通信对带宽提出更高的要求,而传统的电交换架构受限于带宽和能耗,逐渐难以满足通信网络对传输容量及速率的要求。由于对光交换技术的研究和需求逐渐增加,目前已有研究将光交换引入数据中心架构,与全电交换相比,全光交换在带宽、时延等方面有更好的性能。为解决大规模数据中心的问题,满足它对高带宽、高效数据传输的需求,同时兼顾通信系统的扩展成本,通常采用光电混合架构,兼顾光交换和电交换的优势,可以灵活地选择传输方式。在数据中心组网中引入光交换技术,利用时分复用(Time Division Multiplexing,TDM)或波分复用(Wavelength Division Multiplexing,WDM)技术提升带宽、降低时延。时隙交换的前提是精确的时间同步,确保各个机架的时隙对齐,同步的精度越高,划分的时隙越短,控制器在分配带宽时越灵活,可根据实际流量的需求实现动态分配,提升资源利用率。

在已有的光网络架构中,通常使用基于网络传输时间戳的同步协议,其精度在毫秒级或微秒级,或者采用精度能达到纳秒级甚至亚纳秒级的高精度同步方案,但是该方案依赖于特定硬件对相关协议的支持。目前能长时间保持稳定的时间同步模块的最高精度为10 ns。微软提出一种快速光交换架构Sirius,并根据自身的调度特点设计了一种新的同步协议,能达到百皮秒级的时间同步,但是需要在每个时隙进行同步,挑选质量最佳的时钟作为主时钟。

TDM 技术在时域上复用多路信号,可在同一个信道上传输多路数据。为了保证分割时隙的准确性,需要提前对各端点进行时间同步。本文提出一种面向时隙光交换网络的纳秒级时间同步技术,基于FPGA(Field Programmable Gate Array)用硬件描述语言实现IEEE 1588v2 协议。由于机架的主从端都通过FPGA实现该协议的同步逻辑,所以不需要额外的硬件支持就可以实现高精度的时间同步,只需要在数据链路层将时间同步报文插入数据包并通过以太网封装传输即可。同时,与需要考虑网络抖动而在每个时隙挑选最佳时钟的方案相比,硬件开发板的晶振时钟源质量较好,能长时间保持稳定,不需要频繁启动同步进程。

对交换模型进行了实验测试,实验结果证明了基于FPGA 开发的时间同步模块可以实现纳秒级同步,单个同步周期的主从时钟偏移量不超过2.56 ns,即一个时钟周期,且能保持长时间的稳定,同步后的时钟抖动不超过20 ps。

2 架构实现思路

2.1 系统结构

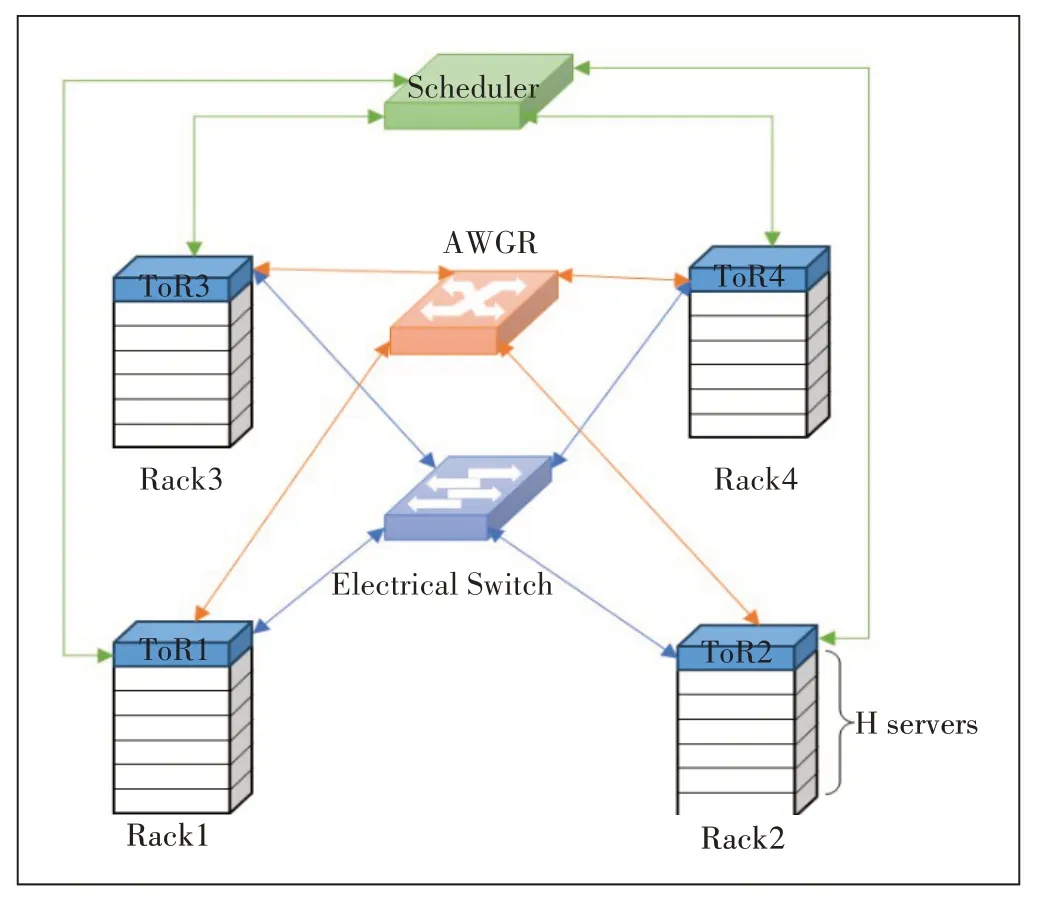

AWGR(Arrayed Waveguide Grating Router)作为一种无源光波导元件,可以实现多波长的路由和分配。为解决数据中心规模扩大带来的带宽、时延、能耗等问题,引入光交换器件AWGR 和可调谐激光器来增加带宽并降低能耗,基于FPGA 的同步与调度可以满足高速数据处理和不同规模网络处理的需求。通过AWGR 的多波长输入输出和周期性路由特性,提升带宽利用率。各机架完成同步是基于FPGA 的调度模块负责集中调度的前提,因此采用IEEE 1588v2 协议实现纳秒级硬件同步。每个机架包含架顶(Top of Rack,ToR)交换机,负责机架内服务器之间的通信。光交换具有高带宽、低时延的特点,而电交换具有更好的控制性能,为了更好地分配和利用带宽,通过分流模块将大象流和老鼠流分别转发到光路和电路,减少网络堵塞,降低延迟和丢包率,提升资源利用率。整体系统架构如图1所示。

图1 系统架构

2.2 时间同步模块

在光网络架构中,每个ToR都包含时间同步模块,在系统初始化完成后,调度器作为整体控制器和时间同步的主端,并以其时钟为基准同步各从端ToR 的时钟。

基于FPGA 实现的控制器负责同步、流控等功能,配置并调用Xilinx 官方IP 核10G/25G High Speed Ethernet Subsystem。使用AXI4_Lite 协议控制FPGA 计数器的初始化和修改,时间同步的主从端分别通过FPGA 实现,用户端同步模块的数据通过AXI4_Stream发送到IP 核,IP 核封装数据并通过光口发送。IP 核的以太网接口包括PCS/PMA 和MAC 2个部分,用户数据通过axi 协议传入10G MAC 核并进行以太网协议的封装,MAC 核和PHY 核之间通过xgmii 接口相连,最后10G PHY 将数据进行编/译码并转换为串行通过GTY输出,SFP 经过光电转换将数据通过光纤发送到其他设备。

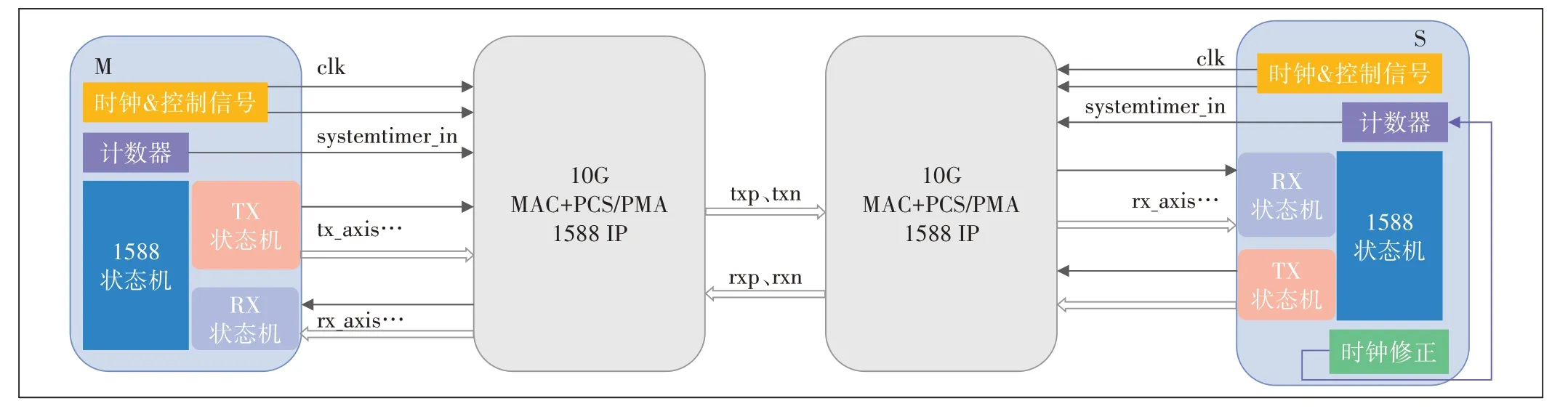

具体的1588v2 协议通过硬件编程语言实现,采用双跳模式,即将事件报文和时间戳分开发送。先由主端向从端发送Sync 报文并记录时间戳t1,表明同步开始,从端接收并记录时间戳t2,t1将跟随Follow_Up 报文发送到从端记录。从端发送Delay_Req 报文并记录时间戳t3,主端接收报文后,将接收时刻的时间戳t4随Delay_Resp 报文发送到从端。由此,t1与t2的差值就是链路延迟与时钟偏移之和,t3与t4的差值为链路延迟与时钟偏移之差,通过差值相加减并除以倍数即可分别计算出链路的延迟与时钟偏移。由FPGA 实现的同步模块结构如图2所示。

图2 1588v2同步模块结构

选定控制器做Master,以该时钟为标准,向从端发送同步信号并交互时间戳,在一个同步周期结束后,从端根据接收的时间戳计算时延和偏移,修改本地计数器,同步Slaver时钟。

3 实验设置

用实验测试平台搭建4×4 的交换模型,使用4 个FPGA 模拟ToR1~4,另1个FPGA 作为集中控制器负责整体的调度。每个ToR 都有4 个25 Gbit/s 的传输通道,其中2个连接到电交换机,一个端口通过可调谐光模块走光纤链路与AWGR 相连,SFP28 收发器提供25 Gbit/s 的传输带宽。选定控制器为主端,ToR1~4 为从端,以控制器上的时钟为主时钟,通过时间戳的交互计算时钟偏移量,同步其他4 个ToR 的时钟。在正式传输数据前,同步各架顶交换机的时钟,并通过示波器测量主从时钟的偏差。同步完成后进行数据传输,使用以太网测试仪发包并监测流量状态。

4 实验结果

主从端FPGA 内部均有一个基于390.625 MHz 时钟的计数器,导出一个在计数值变化时会翻转的电平信号,累加输出一个1 ms 翻转的方波,通过SMA-BNC线连接到示波器测量,采样约20 000 个数据点并计算RMS(Root Mean Square)值。示波器的测量结果如图3所示,其中绿色波形为主时钟,黄色波形为从时钟,采样结果显示时钟偏移为2.026 9 ns。红色波形为几万个数据点的分布图,峰值范围从1.983 4 ns 到2.068 5 ns,时钟抖动为10.992 ps。

图3 示波器测量波形

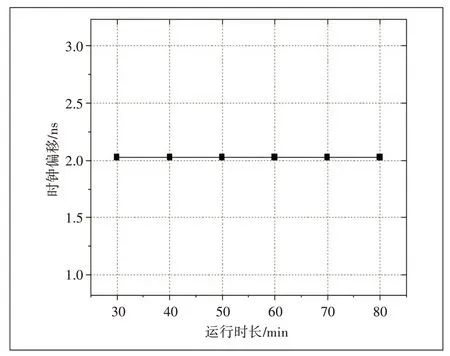

根据示波器的结果,以RMS 值作为有效数据点绘图,测量不同运行时长下的时钟偏移,结果如图4 所示,偏移量维持在一个稳定值。由于时间同步模块可以在一个时钟周期内完成同步,采用的时钟频率为390.625 MHz,因此时钟偏移量不超过2.56 ns。

图4 运行时长对时钟偏移的影响

为考察同步后时钟的稳定性,分别测量不同光纤长度、运行时长和环境温度下的同步结果,数据点的采样方式与图4相同。

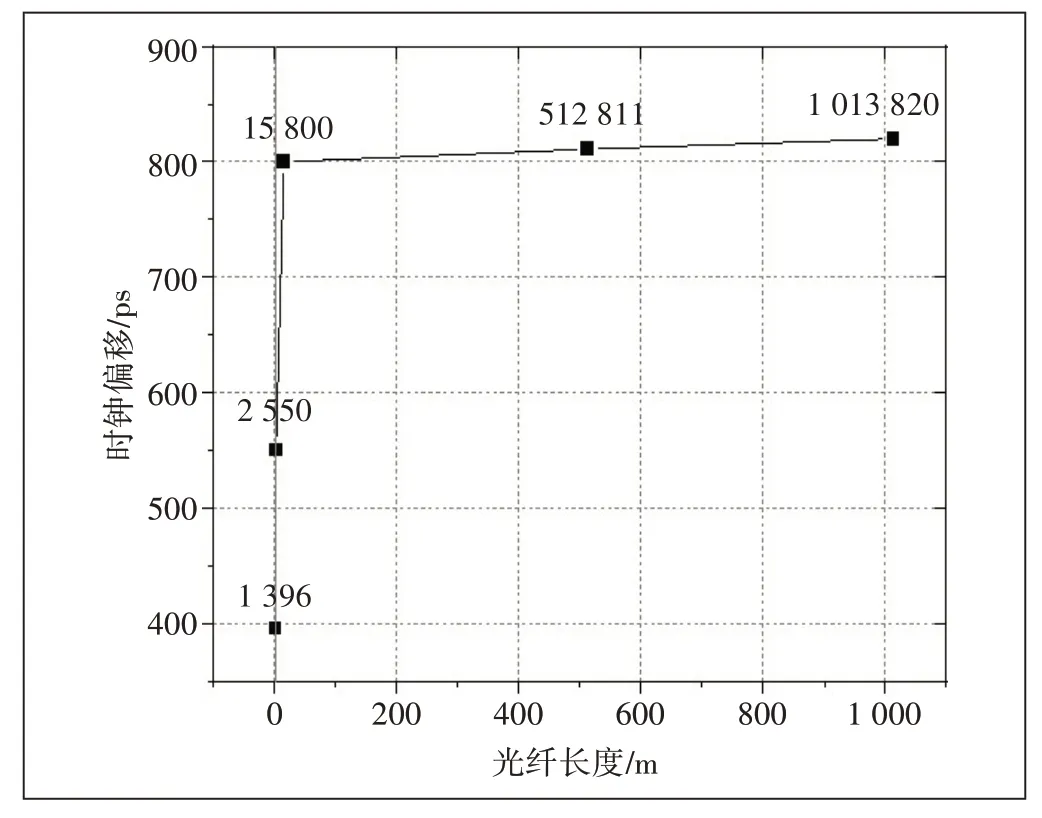

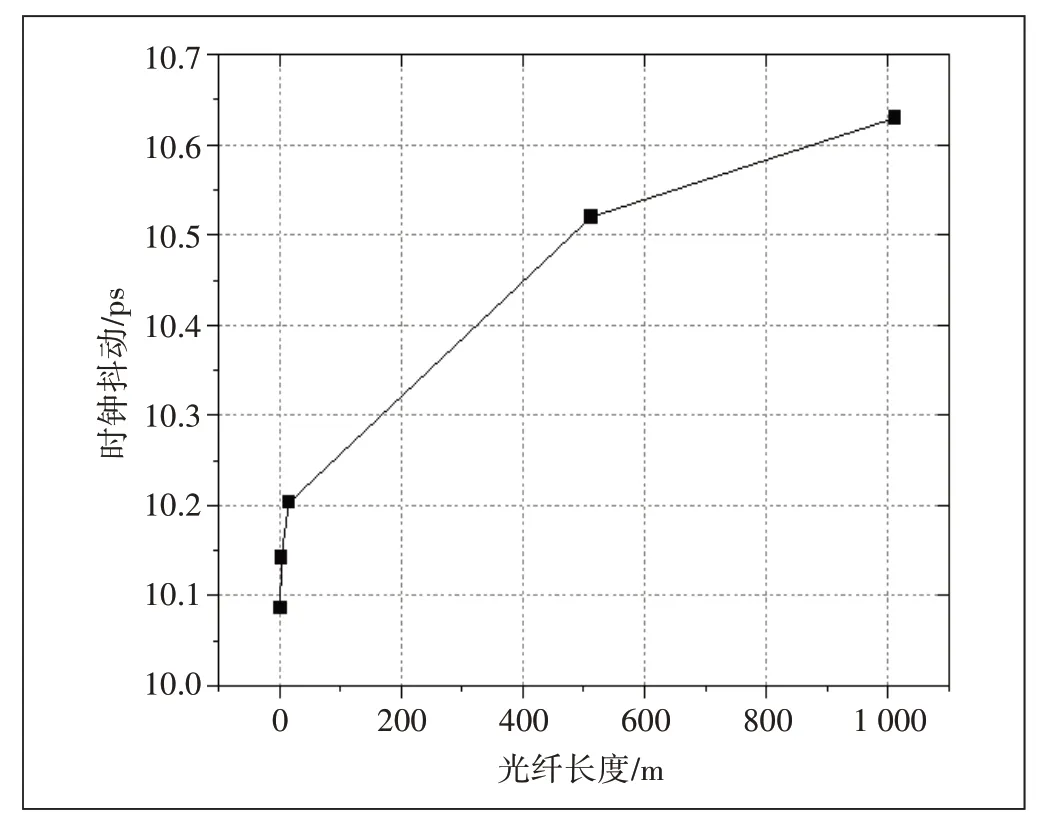

如图5 所示,分别测量了1 m、2 m、15 m、512 m 和1 013 m长度的光纤对时钟偏移的影响,差值保持在皮秒级,虽然在1 m 到15 m 光纤长度下时钟偏移由396 ps 增加到了800 ps,但512 m 和1 013 m 长度下的同步结果基本都在800 ps 左右。由图6 可看出,不同光纤长度下,时钟抖动在10.086 ps 到10.630 ps 之间,稳定性较好。实验结果表明光纤长度对时间同步的结果没有显著影响,不影响纳秒级光交换系统的性能。

图5 光纤长度对时钟偏移的影响

图6 光纤长度对时钟抖动的影响

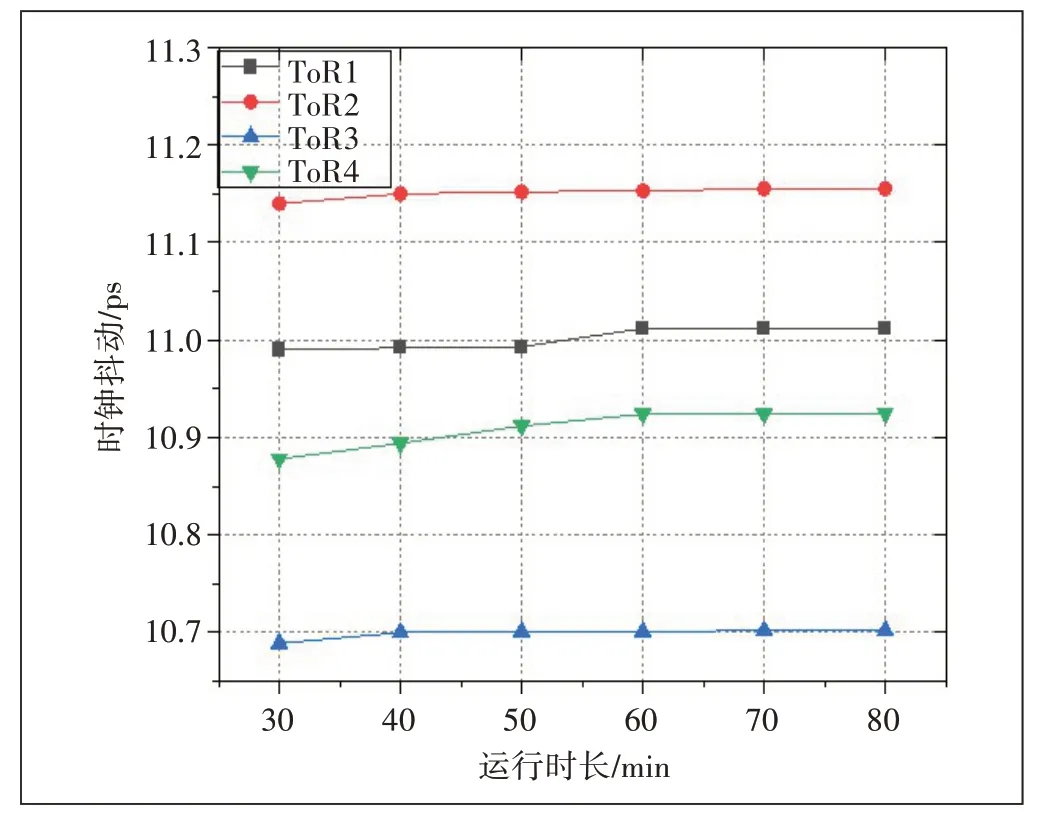

使用1 个FPGA 板作为主端控制器,剩下4 个FPGA 作为从端ToR1~4,对多节点同步的情况下各点的同步效果进行测试,结果如图7 所示。从图7 可以看出,时钟抖动基本保持在一个稳定值,最小值为10.689 ps,最大值为11.155 ps。对不同环境温度下时钟的稳定性进行测试,将代表主从端的FPGA 放在恒温箱中运行,以5℃为一个梯度单位进行测量。实验结果表明在20~50 ℃的温度下,时钟抖动均稳定在13 ps左右(见图8)。

图7 各节点的时钟抖动情况

图8 温度对时钟抖动的影响

5 总结

本文提出了纳秒级时间同步光电混合架构,该架构实现了基于硬件的纳秒级时间同步,保证基于时隙的数据传输,减少了集中调度各架顶交换机所造成的时延。最终结果表明一个同步周期内主从时钟的偏移为纳秒级,时钟偏移量不超过2.56 ns 且稳定性较好,时钟抖动为皮秒级,满足同步需求。