基于Verilog HDL 的简易电子琴控制电路设计与实现

张皓祎,郑冰,卢炽杏,郑惠之,胡锦程

(航天工程大学 信息学院,北京,101401)

0 引言

声音是由振动产生的,不同的振动频率导致了不同的音调[1],目前世界通用的定律方法是十二平均律,根据十二平均律,八度的音程按波长比例被平均分成十二等份,每一等份称为一个半音(小二度),一个大二度则是两等份,称为全音,每两个半音的频率比为4。音高八度音指的是频率加倍,八度音的频率分为十二等分,即分为十二个等比级数,也就是每个音的频率为前一个音的2 的12 次方根。

音名“C,D,E,F,G,A,B”的唱名依次为“do,re,mi,fa,sol,la,si”,对应曲谱中的数字“1,2,3,4,5,6”,低音6 的频率为440Hz,根据十二平均律可计算出低音1 至高音7 的频率如表1 所示。

表1 音名与频率的关系

本设计方案基于Verilog HDL 语言实现。Verilog HDL语言是一种常用的硬件描述语言,用于数字电子系统设计。Verilog HDL 语言提供了编程语言接口,通过该接口可以在模拟、验证期间从设计外部访问设计,包括模拟的具体控制和运行,使用Verilog 描述硬件的基本设计单元是模块(Module),构建复杂的电子电路,主要是通过模块的相互连接调用来实现的。Verilog HDL 语言是目前应用最广泛的一种硬件描述语言之一。

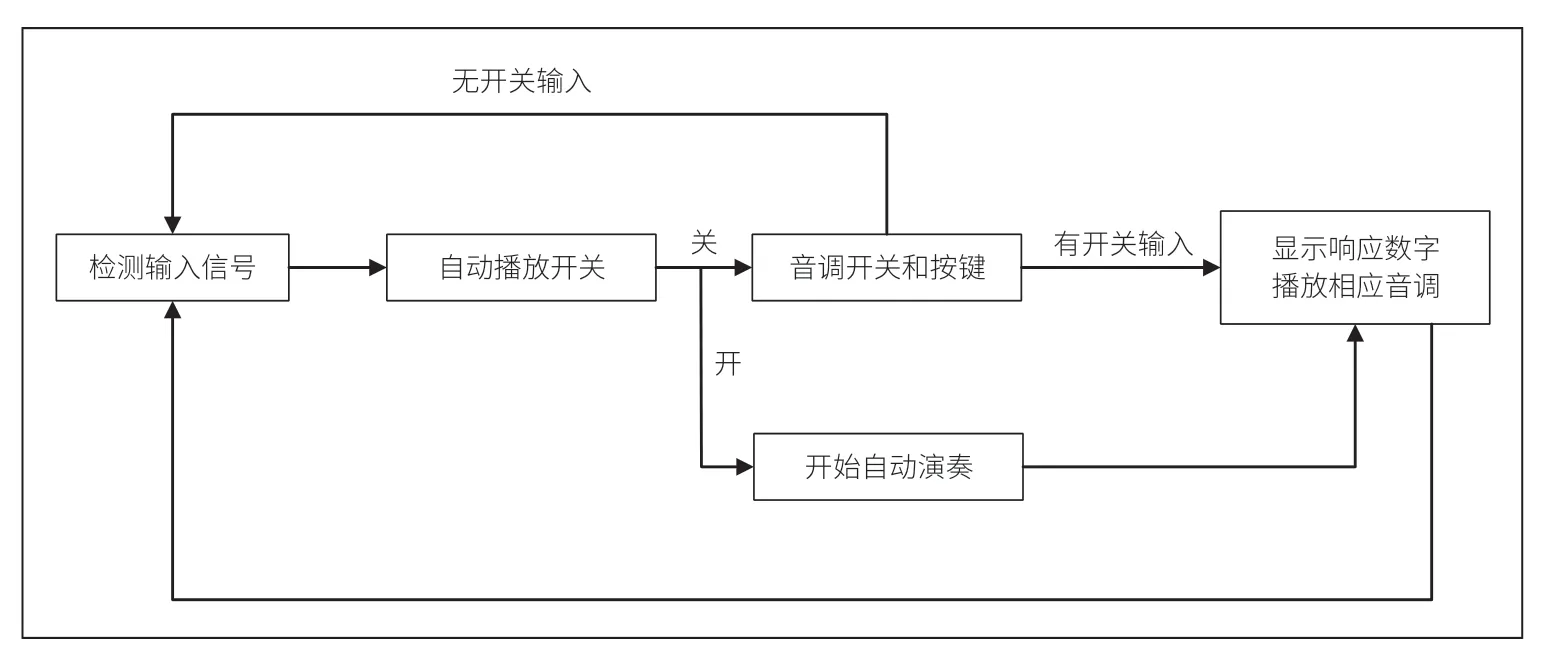

1 系统整体设计

针对设计要求计划实现的基本功能,拟将本电子系统划分为音乐播放模块、数码管显示模块与分频模块。其中,音乐播放模块为顶层模块,在该模块中,根据输入信号的不同决定所播放的音调和传递给数码管显示模块的参数,从而实现简易电子琴的基本功能。

总体设计思路框图如图1 所示。

图1 设计思路框图

2 分块设计

■2.1 顶层模块

音乐播放模块为本方案的顶层模块,在该模块中,通过调用分频模块产生低音、中音、高音三个音域共21 种不同频率的音符,需要注意的是,除了21 个基准频率以外,还需分出一个4Hz 的时钟信号,这是因为大多数简单乐曲为4/4 拍,即以四分音符为一拍,每小节包含四拍,假设一个全音音符持续时间为1s,那么四分音符的持续时间为0.25s,对应需要一个4Hz 的时钟信号来控制信号,从而达到最佳的音乐自动播放效果。

在该模块中,我们设计让自动播放控制信号为高电平状态时工作,因此当自动播放控制信号为高电平时,计算机读取事先存储在只读存储器中的音符,同时用于自动播放的计数器开始计数,通过分频产生不同频率的时钟信号,时钟信号输出到蜂鸣器可产生对应的音调,在读取完整首乐曲音符后,一首音乐便被完美地演奏出来,若控制自动播放控制信号始终为高电平,蜂鸣器则会循环播放预先存储在程序中的乐曲。当自动播放控制信号为低电平时,切换为手动模式,本设计方案通过音调选择按钮SW 的输入检测低、中、高音调,通过BTN1~BTN7 七个按键的输入判定所要演奏的音符,并将完成分频的对应频率时钟信号赋值给输出信号beep,并输出到蜂鸣器,产生对应的音调;同时,根据BTN 信号的输入结果,将所选择的音符信息传输给数码管显示模块,显示音符相对应的数字。

图2 顶层模块执行框图

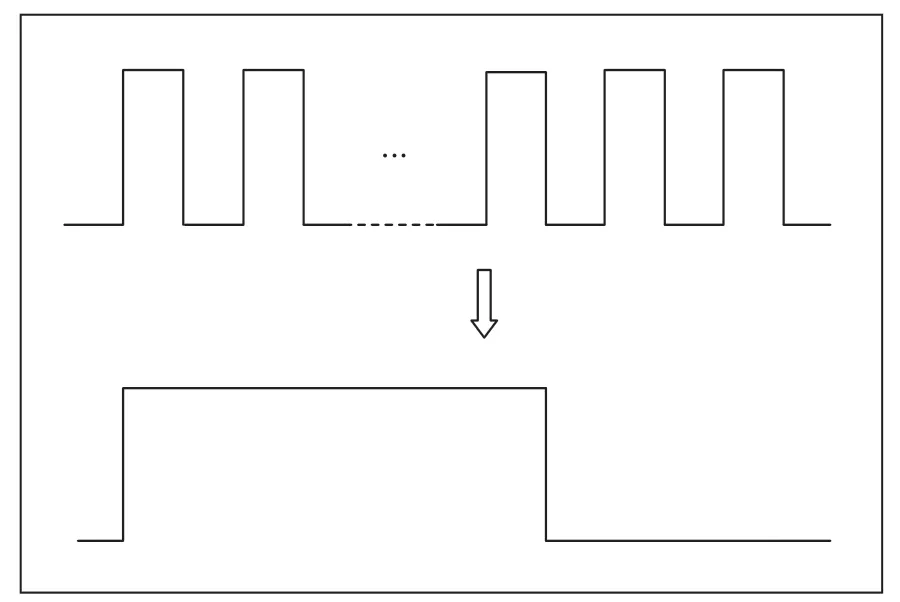

■2.2 音调控制—分频器设计

不同的振动频率能够产生不同的音调,所有不同频率的信号都能通过对一个基频分频得到,为避免逐个分频导致的编译代码冗杂,在本设计方案中定义分频系数为参数,这样在每次分频时,只需调用分频模块并输入所需频率的分频系数即可得到所需的时钟信号[2]。分频原理如图3所示。

图3 分频原理

分频器输入信号为基准时钟信号(本方案中基准时钟信号频率为50MHz),规定输出为clk_out。每经过基准时钟信号的一个时钟信号,分频器中的计数加一,输出的频率信号周期增大一倍,根据分频原理,计数器计数达到分频系数时,clk_out 取反,此时即可得到需要的时钟信号,基于此,可以得到分频系数的计算公式为:

在实际程序运行时,公式计算出的parameter 作为分频系数时的分频效果实际上与以parameter 向下取整的整数作为分频系数的分频效果一致,在现实生活中,由于分频系数大多非整数,本方案统一将parameter 向下取整的整数作为求取不同频率时钟信号的最终分频系数。

■2.3 数码管显示

8 个共阳极七段数码管的 8 个段码,共用 FPGA I/O,固定连接在实验平台中的FPGA_CON1 处,开发板上8 个7段数码管的段码输入端并联在一起,8 个位码相互独立。当相应码段SEG 端输入为高电平,同时需要显示的数码管的共阴极端 CAT 为低电平时,该数码管相应的端就点亮。根据数码管显示原理点亮相应码段,即可显示所需要的数字。

在本方案中,输入CAT 信号选通最右侧七段数码管,通过检测BTN 信号的输入,从而产生相应的SEG 信号,将SEG 信号输出给数码管,数码管即可显示输入音符对应的数字。

3 设计的仿真分析及引脚分配

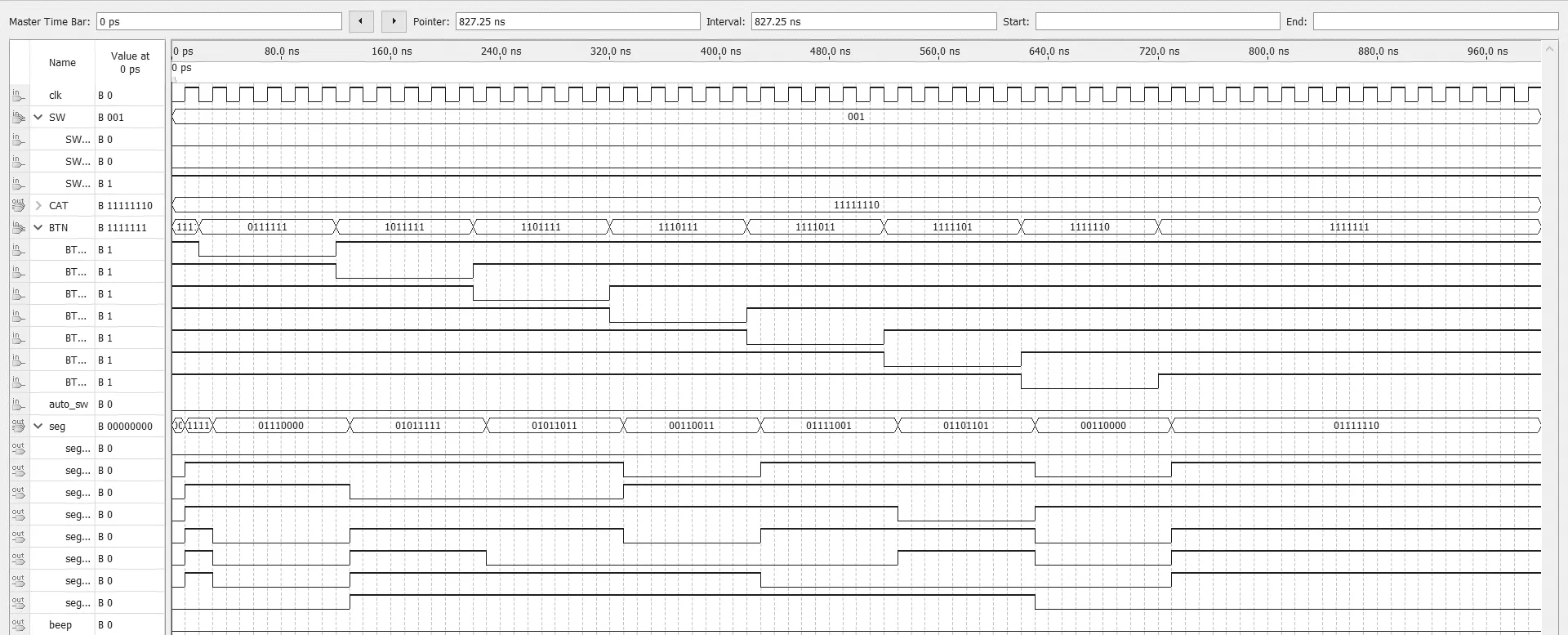

■3.1 数码管显示模块

在该模块的仿真中,通过改变不同时刻的BTN 输入模拟实际按下按键时的行为。仿真波形图如图5 所示。

图4 八个七段数码管原理图

图5 数码管显示模块波形仿真图

从图5 中可以看出,随着按下按键的变化,数码管的输出信号产生了相应不同形式的变化。数码管的输出信号SEG[0]至SEG[7]分别对应了八段数码管的a,b,c,d,e,f,g 七个显示段。BTN 输入信号接综合实验箱上的F1~F7 按键,该按键静息状态为高电平,按下时为低电平,与数码管的结构进行对照可知,BTN[0]至BTN[6]信号分别为低电平时,数码管上显示的数字分别为1,2,3,4,5,6,7。

■3.2 分频模块

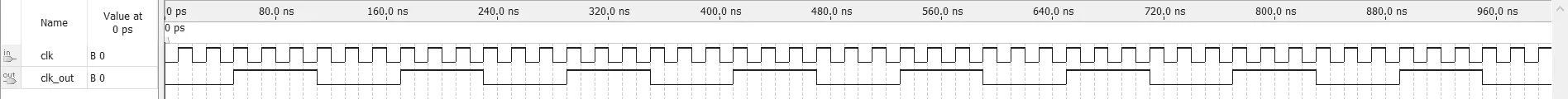

输入clk 为50MHz 的时钟信号,通过改变分频系数,期望得到频率为基准频率六分之一的clk_out 时钟信号。仿真波形图如图6 所示。

图6 分频模块波形仿真图

从图6 可以看出,分频后信号周期为原信号周期的六倍,故分频模块可以达到所需的效果。

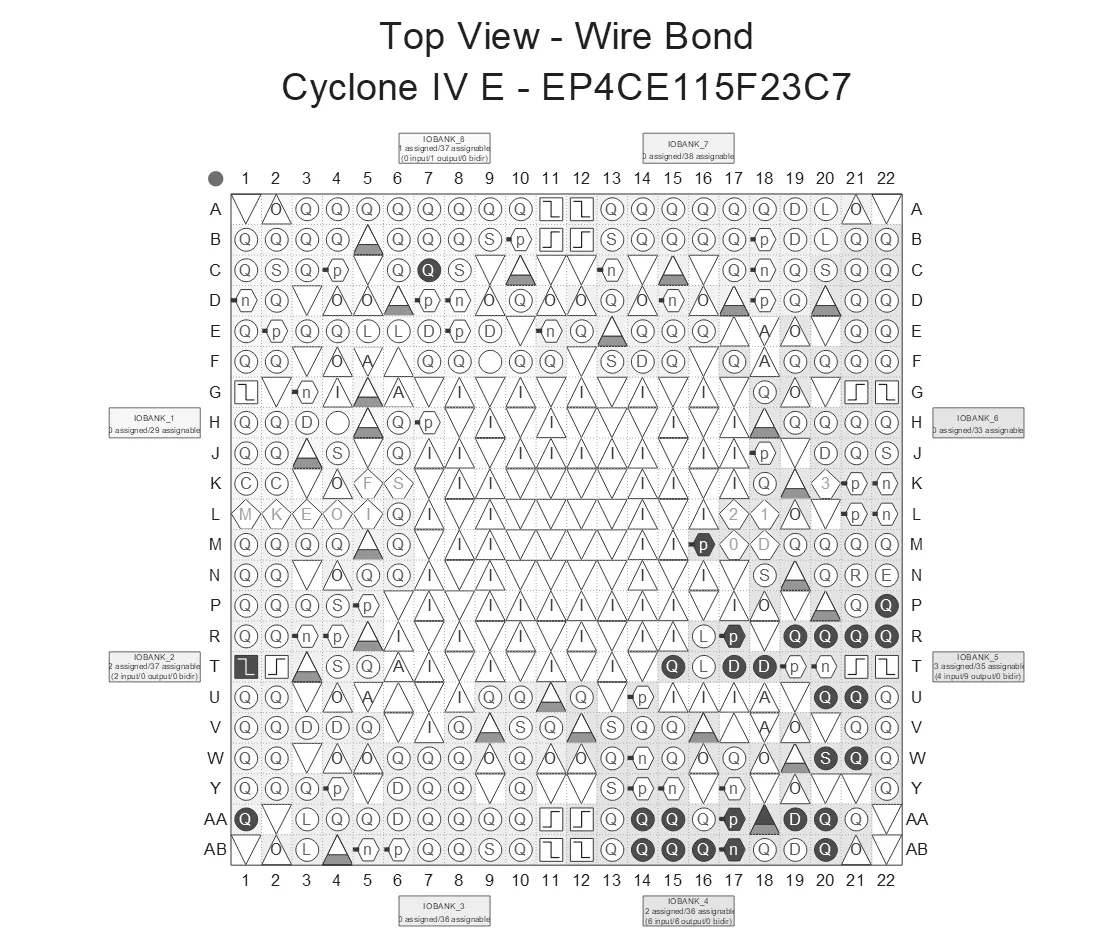

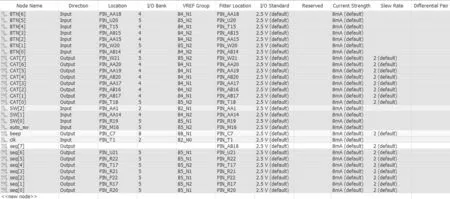

■3.3 FPGA 管脚分配

针对SOPC FPGA 平台的可编程器件实验板,管脚配置情况如图7 与图8 所示。

图7 实验板管脚分配图

图8 管脚分配图

方案中的BTN 输入信号(音符)由实验板上的F1~F7按键控制,按下时为低电平有效信号。SW 音域输入信号、音乐自动播放信号由实验板上的SW 按键进行控制,SW 按键上拨时为高电平有效信号。

基准时钟信号与实验板上的PIN_T1 管脚相连,提供50MHz 的基准频率。

CAT 输入信号为控制八段数码管的共阴极端信号,当CAT 输入位为低电平时,对应数码管才能工作。

SEG 信号为数码管显示信号,与数码管共阳极端相连,当SEG 信号为高电平状态时,对应的数码管显示段将被点亮。

Beep 为蜂鸣器控制信号,当beep 为高电平状态时,蜂鸣器输出对应的音调,否则蜂鸣器将不发声。

4 小结

本文设计并实现了Verilog HDL 的简易电子琴控制电路,主要包括音频播放模块、分频模块和数码管显示模块。分频模块实现不同音调的生成,音频播放模块实现按键弹奏发声与音频自动播放,数码管显示模块实现音符的数字显示。音调准确,节拍符合音乐播放规则,演奏与播放效果较好。