面向物联网安全认证的RO PUF 模型的研究

张学军,曹瑞浒,周寅峰,谷群远,梅年松

(1.盐城市质量技术监督综合检验检测中心,江苏 盐城 224056;2.中国科学院 上海高等研究院,上海 200120;3.中国科学院大学,北京 100049)

近年来,随着移动通信技术的全面普及,物联网设备的数量成几何级增长,其已经融入了人们的日常生活。物联网产生的信息与个人生活息息相关,联接物联网的设备种类多样、型号各异,信息交互的双方需要确保设备和身份安全可信方可建立连接。物联网体系内的身份认证问题需要被足够重视,物理不可克隆函数利用硬件制作过程中的随机差异产生身份信息,提高物联网现有设备的身份认证能力,非常适合在物联网设备现有FPGA 芯片上部署和实现。

1 物联网安全认证

物联网(Internet of Things,IoT)是物与物之间进行通信。在无人工干预下,各种传感器和物体可以作为智能节点,彼此交换信息[1]。我国物联网行业呈高速增长状态,物联网设备在智能电网[2]、医疗保健[3]及智能物流[4]等领域已得到了广泛的应用。中商产业研究院预测,2022 年中国物联网设备连接数将达到105 亿台。伴随5G 商用和产业物联网的稳定渗透,中国物联网设备总连接量在2025 年将达到156亿台。

物联网体系结构自下到上可分为三层:感知层、网络层和应用层[5],如图1 所示。感知层识别物体和采集信息,主要由嵌入式传感器和射频标签(RFID)等设备形成局部网络,对信息进行初步处理后通过各种网络协议把信息传递到网络层。网络层是物联网信息传递的传送纽带,利用无线和有线网络实现互联网与物的连接。应用层是物联网的最顶层结构,通过云端计算力对下层数据进行整理分析,及时向用户反馈,最终实现物与物、人与物的信息交互。物联网与互联网相比,数据量更大、数据更隐私、数据交换更频繁,保护物联网安全[6]是数据安全使用的前提。

图1 物联网体系结构

物联网的三层结构决定了层与层之间、各层设备之间都需要进行身份认证。由不同传感设备组成的物联网,需要识别接入信息源的每个设备的身份是否可信。攻击者可以伪装传感节点设备的身份,向感知层瞒报或错报虚假信息,也可以非法俘获并窃取节点数据信息。由于物联网的服务器与终端设备是一对一身份认证,如果攻击者伪造大量的终端,同时向服务器发送认证请求,导致网络层核心网络服务器过载,会使网络中的信令通道发生拥塞[7],这是对物联网网络层常见的攻击手段。物联网通信前,应当先验证用户和设备的身份是否可信。物联网身份认证技术为加入物联网的设备和用户提供安全可信的环境,是保障物联网安全的关键[8]。如今,物联网提取用户身份的生物特征安全认证已经是司空见惯,如指纹、虹膜、面部信息等。目前对物联网设备的身份认证,通常验证设备预存的ID 信息,但是攻击者可以监听和修改ID号伪造身份,这个难题未来有望通过物理不可克隆函数(Physical Unclonable Function,PUF)来解决。

2 物理不可克隆函数

2.1 PUF技术

物理不可克隆函数通过硬件制造过程中的随机差异[9],生成该芯片独"一无二的身份信息,可用于芯片防伪、身份认证、信息加密等领域,被称为“硬件的DNA”。芯片的身份信息在出厂前注册录入厂商的数据库中[10],用户可在数据库中对比芯片的ID,辨别芯片身份的真假。PUF 技术具有唯一性和不可预测性,攻击者无法制造出一模一样的两枚芯片,所以PUF 能为硬件设备提供最高级别的安全保护。

PUF 的实现机理不同,有非电子PUF、模拟电子PUF 和数字电子PUF。数字电子PUF 容易在嵌入式设备上实现,可分为数字存储型PUF 电路和数字延时型PUF 电路。数字存储型PUF 是提取存储单元的上电初值,因芯片制造过程的差异,一些存储元器件的上电初值随机分布,可直接提取转化为唯一身份信息。数字延时型PUF 信号通过在不同电路中的传播延迟不同来实现差异提取。

2.2 FPGA与RO PUF技术

现场可编程门阵列(Field Programmable Gate Array,FPGA)比普通MCU 有更多数量的I/O 接口,有更好的处理性能和能耗比,其并行处理结构更适合物联网应用大规模高速数据传输的需求。目前,FPGA 在物联网车载设备和智能家居设备上应用广泛,是一款开发环境成熟的产品。

环形振荡器PUF(Ring Oscillator PUF,RO PUF)通过比较信号在两条回路中的延迟时间得到响应信息。每个回路的延迟时间受到元器件的大小、晶体管的浓度、内部和外部噪声等参数的影响,不同芯片之间的参数由于制造工艺差异,都有所不同。组成FPGA 的数千万个可用门电路参数各不相同,为RO PUF 提供了完美的实现条件[11]。

3 混阶并行RO PUF

传统RO PUF 中,振荡环阵列内每个振荡环的反相器个数是相同的。RO PUF 在输入激励信号后选择两个环形振荡器回路,通过计数器记录规定时间内两个回路产生振荡的次数,次数越大说明回路的相对延迟越低。如果第一个回路延迟时间短,则PUF 输出响应为1,否则为0。由于振荡环的延迟时间差异小,且容易被电路中的噪声干扰,所以PUF 的输出结果不稳定。PUF 在相同激励信号下的输出结果越相似,可靠性越高。

与传统模型不同,混阶模型每个振荡器回路中的反相器个数不同,不同回路之间的延迟时间差异将更加明显。在相同的规定时间内,激励信号在阶数不同的两个环路上传递,计数器的结果差别很大。如果反相器个数太少时,振荡环的工作频率过大,计数器的结果可能超过设计的最大值。所以该设计混阶模型与普通模型如图2 所示,选择了14、16、18 和20 个反相器构成的环形振荡器阵列。

图2 混阶模型与普通模型

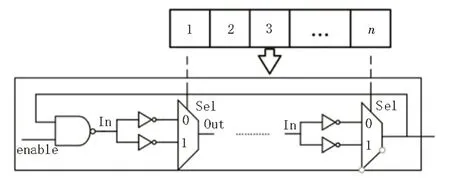

可重构环形振荡器是对PUF 安全性的大幅改进。对于普通的环形结构振荡器结构,每个振荡环的振荡周期是固定的。两个回路之间结果可以被攻击者记录下,从而遍历结果破解输出信息。对于一个有k个振荡环的阵列,攻击者最多只需要比较k×(k-1)/2 种情况,就能得出PUF 内所有振荡环两两比较的结果。简单地增加振荡环的个数非但不能提高PUF 的安全性,而且会消耗大量的硬件资源。因此,该文加入了可重构的路径选择器动态更新信号的振荡回路,如图3 所示。PUF 开始工作后,控制逻辑模块根据激励信号,赋予对应的振荡环的使能信号高电平,振荡环产生自振荡。PUF 工作时,路径选择器的初始值是默认设计者自定义的,n阶路径选择器有2n种选择。根据路径选择寄存器的默认值,振荡信号在设置的路径上传递,路径选择器如图4 所示。输出响应需要多个结果,所以每次的激励信号需要不断更新。第a次比较结果产生后,响应值到n位暂存器的第a位。当n位暂存器填满后,视为一次迭代完成。此时将暂存器的结果填入路径选择器,路径选择器根据产生的新信号传递路径。当迭代次数达到设定值后,enable 输入低电平信号,PUF 工作结束,最后一次暂存器内的数值就是最终响应结果。可重构环形振荡器的特点就是能极大地丰富响应结果,降低PUF 被暴力破解的可能。

图3 可重构环形振荡器

图4 含路径选择器的环形振荡回路

在实际使用中,16 位响应信息是不够的,PUF 输出作为商品的身份ID 号有重复号码的可能性比较大,且攻击者可以通过暴力破解的方式寻找正确的激励响应结果。为了得到较长的64 位身份ID 号,传统的单RO PUF 将每次迭代的16 位响应信息输出,直至补全64 位。这种做法会暴露每次迭代的结果,攻击者可以根据多次迭代的结果对PUF 数学建模进行攻击。如果在前期迭代时受到干扰,产生的响应结果不准确,后续的输出结果也由错误结果生成,必然也是不准确的。因此,该设计采用图5 中的并行架构,四组RO PUF 并行工作,规定统一的迭代次数。输出各组最终的16 位响应信息作为最后的64位ID 号。这种方法使FPGA 硬件资源利用率更高,各组之间信息互不关联,结果比传统的方案更安全稳定。

图5 单RO PUF与并行RO PUF

以混阶模型RO 环作为底层处理单元,用可重构模块进行迭代增加了结果的随机性,最终使用4 组并行架构得到64 位响应信号,整体设计架构如图6所示。

图6 整体设计架构

4 实验效果

该设计在Xilinx 的Spartan6 系列XC6SLX16-2CSG324 FPGA 开发板上进行实物测试,设计采用16 位路径选择器,经过三次迭代,在四个并行模块下响应结果可以达到2192种。通过串口调试助手向PUF 发送八位激励信号。测试时选择了五个激励信号,它们和对应的八位ASCII 码分别是!(00100001)、0(00110000)、A(01000001)、M(01001101)、t(011101 00)。连续向PUF 发送十次相同的激励信号,记录每次的64 位响应信号。统计每组激励响应结果产生的错误位数和对应的可靠性,统计情况如表1所示。

表1 各组激励响应的错误位数和可靠性

实验结果表明,响应结果的准确度最高可达到100%,最差准确度为99.69%,新混阶并行RO PUF 的可靠性非常高。将该设计的效果与其他研究者设计的PUF 类型和可靠性进行对比可知,新RO PUF 结构有更高的可靠性,比较结果如表2 所示。

表2 不同PUF之间的工艺和可靠性比较

5 结束语

该文首先介绍了物联网体系结构,分析在物联网设备日益增长的时代,加强物联网设备之间身份认证的必要性。接着分析可以使用物联网设备上成熟的FPGA 产品,实现RO PUF。该文最后采用一种新颖的RO PUF 结构,使用混阶并行的可重构模型改善PUF 的性能。该设计在Xilinx 的Spartan6 系列XC6SLX16-2CSG324 FPGA 开发板上进行测试,可靠性高达99.69%。