基于内建自测试电路的NAND Flash 测试方法

解维坤,白月芃,季伟伟,王厚军

(1.电子科技大学自动化学院,成都 610097;2.中国电子科技集团公司第五十八研究所,江苏无锡 214035;3.电子科技大学深圳高等研究院,深圳 518110)

1 引言

NAND Flash 因具有非易失性、成本低、存储容量大的优点,在市场中所占比例与日俱增,手机、数码相机等数字移动设备中的存储器大多为Flash 型存储器。随着半导体制造工艺技术的进步,NAND Flash 朝着单元尺寸更小、编程电压更低、存储容量更大的方向发展,这造成了NAND Flash 存储单元间互相影响的概率提高,导致存储器的可靠性下降,因此在使用之前需要排除由于制造工艺、老化等情况而失效的存储器,降低数据损失的可能性,这对NAND Flash 存储器的测试至关重要。常见的测试方法主要利用自动测试机台,通过嵌入式软件或搭建内建自测试(MBIST)电路来完成测试。由于MBIST 可以达到全速测试的模式,并且可以降低测试成本,所以被广泛采用。存储器MBIST 的主要部分是测试算法,因此在进行MBIST 电路设计时重点在于选择一个故障覆盖率高且测试时间花费少的测试算法。本文以NAND Flash的故障类型为基点,分析了已有测试算法的故障覆盖率以及测试时间,March-like 对测试故障覆盖较全,但对读编程干扰故障覆盖不完全并且无法检测读干扰故障,本文提出一种改进的March-like 算法,有效解决了以上问题。

2 NAND Flash 故障类型

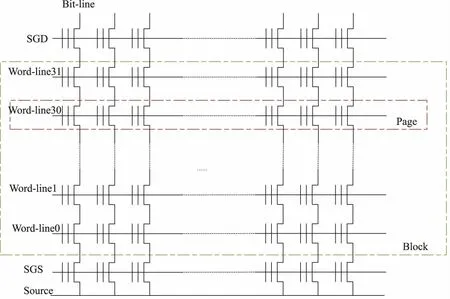

Flash 存储器的基本存储单元是浮栅场效应管,主要是由衬底、隧道氧化层、多晶浮栅(FG)、栅间绝缘层、多晶控制栅(CG)以及源极、漏极组成。根据多晶浮栅中存储的电荷量可以判断存储器存储的数据。NAND Flash 字符串由多个基本存储单元以及两个选择晶体管(SGD,SGS)构成,多个存储单元顺序相连,两个晶体管分别连在源极和漏极,多个NAND Flash字符串组合在一起构成阵列。一条字线上所有单元是一页,多个页构成块。NANDFlash 阵列结构如图1 所示。

图1 NAND Flash 阵列结构

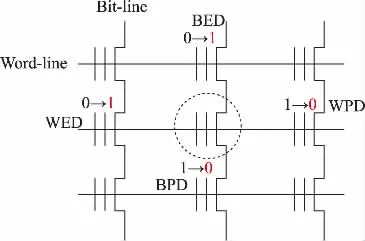

Flash 故障类型包括一般SRAM 型存储器所具有的固定型故障(SAF)、转换故障(TF)、地址译码故障(AF)和固定开路故障(SOF)等。此外,由于Flash 的特殊物理结构,Flash 存储器的很多存储单元都连接到相同的位线或字线上,因此Flash 还存在一些特有故障,如图2 所示。

图2 Flash 中特有的故障

(1)字线擦除干扰(WED),当对一个存储单元进行编程操作的时候,与其位于同一字线上的存储单元被擦除。

(2)位线擦除干扰(BED),当对一个存储单元进行编程操作的时候,与其位于同一位线上的存储单元被擦除。

(3)字线编程干扰(WPD),当对一个存储单元进行编程操作的时候,与其位于同一字线上的存储单元被编程。

(4)位线编程干扰(BPD),当对一个存储单元进行编程操作的时候,与其位于同一位线上的存储单元被编程。

(5)过度擦除干扰(OED),擦除操作导致存储单元的阈值电压降低和位线泄漏,从而导致该单元不能正常编程,需要对其进行连续编程操作后,存储单元可以恢复。

(6)过度编程干扰(OPD),存储单元在编程过程中,有多余的电子进入浮栅层,导致过度编程不被正常擦除,需要对其进行连续擦除操作后,存储单元可以恢复。

(7)读编程干扰(RPD),在读取存储单元时,进行读操作的各个端口的工作电压条件与编程操作的相似,只是电压差不同,因此在读操作过程中可能出现漏端热电子注入从而导致编程操作。

(8)读干扰(RD),在某存储单元连续进行读操作时,对位于同一字线或同一位线的存储单元中存储电量产生影响。

3 测试算法分析

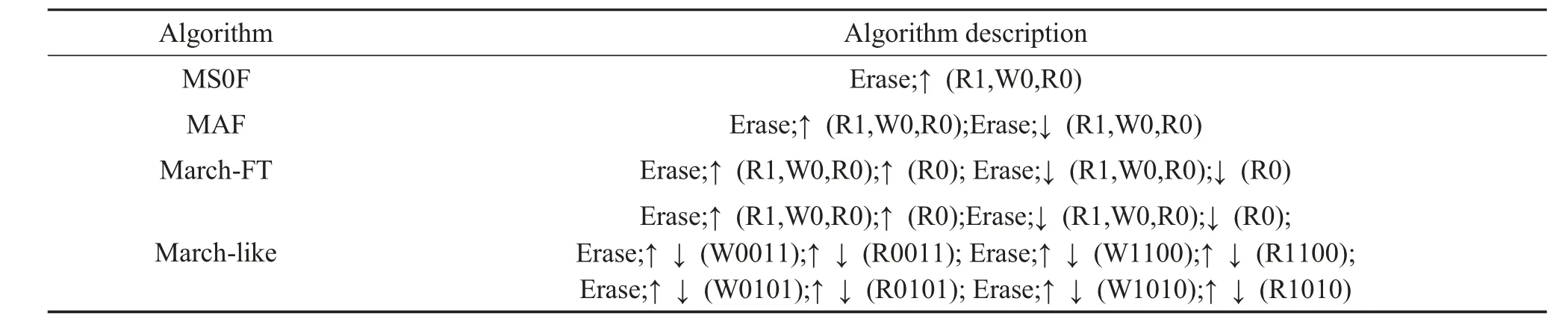

为检测固定故障,根据Flash 擦除特性,可以在擦除后读取逻辑1,再写入逻辑0 即可检验。为检测转换故障,需要进行3 次写入、读取操作,依次写入010 或101 后读取并与期望值比较,对于Flash 仅需完成1 到0 的写入。为检测固定开路故障,需要在擦除后检测是否为1,写入0 后读取,判断结果是否为0。为检测地址译码故障,需要检测经译码电路后实际物理地址与逻辑地址是否对应,擦除后按地址升序,读1、写0、读0,再擦除并按地址降序,读1、写0、读0。针对Flash 的故障,现有的测试算法如表1 所示。Erase 为擦除操作,R为读操作,W 为编程操作,↑为地址升序,↓为地址降序,↑↓为地址升序、降序均可。

表1 现有的Flash 测试算法

对现有测试算法进行分析,March-like 为故障覆盖率较高的测试算法,但无法检测到读干扰故障且对读编程干扰故障检测不全,因为在进行R1111 操作后直接进行编程操作,如果出现读编程干扰故障则无法被检测到。此外,由于Flash 的擦除时间为ms 级,编程时间为μs 级,读取时间为ns 级,为了降低测试所需时间,应尽可能减少擦除和编程的次数,March-like 算法的测试复杂度为6(F)+6n(P)+10n(R),n 为页数,测试复杂度较高且测试效率低。

因此,对March-like 算法进行改进。根据对故障模型的分析,为检测读编程干扰故障,需要有连续两次的读1 操作,但目前的测试算法中并不包含,因此需要在↑(R1,W0,R0)步骤中多添加一次读1 和读0 操作,改为↑(R12,W0,R02),其中R12和R02代表重复读2次。由于读操作所占用的时间仅为ns 级,与擦除和编程操作相比,读取次数增加对总时间的影响甚微。

根据以上分析,本文提出的改进March-like 算法不但提高了测试故障覆盖率,还提高了测试算法的效率,减少了测试所需时间。具体算法如下:

其中Pcheckboard为棋盘格向量,Pcheckboard为棋盘格反向量,R12期望读取响应为1。相较March-like 算法,改进的测试算法复杂度降低,仅为4(F)+4n(P)+12n(R)。由于读取时间较短,因此主要测试复杂度减少了2(F)+2n(P),测试时间约减少30%。测试算法的故障覆盖情况如表2 所示。改进的March-like 可以实现对读编程干扰以及读干扰故障类型的全覆盖,故障覆盖率提升了16.7%。

表2 Flash 测试算法的故障覆盖情况

4 MBIST 电路设计与验证

4.1 MBIST 电路设计

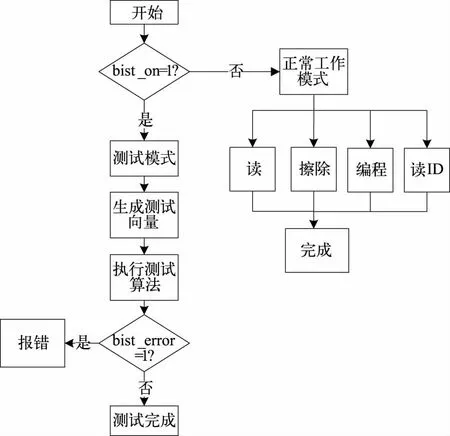

MBIST 具体电路如图3 所示,包括测试地址生成器、测试向量生成器、控制信号生成器以及BIST 控制器和比较器等。BIST 控制器主要以有限状态机的形式来实现,可协调控制各模块。地址生成器用于生成测试地址,完成测试算法中地址的递增、递减,主要采用加法器实现。向量生成器根据测试算法提供测试所需的向量,主要产生4 种不同的向量。比较器对从Flash中读出的向量与向量生成器产生的向量进行比较,以判断Flash 是否存在故障。bist_on 信号控制测试的开始,bist_done 信号为高时表明测试完成,bist_error 为高则表明在测试过程中出现故障。

图3 MBIST 具体电路

BIST 控制器对整个测试过程进行控制,包括对存储器的读写擦除控制、数据产生器测试向量的产生控制、比较器的控制、地址生成器产生升序的地址序列还是降序的地址序列控制。在BIST 控制器中包含了测试算法的状态机。向量生成器结合测试算法的设计,根据需要产生全1、全0、AA、FF 的测试向量激励,并按照不同的地址写入不同的测试向量,构成测试图形。控制信号生成器主要用于控制NAND Flash 的WE、RE、CLE、ALE 等控制信号的产生,在BIST 控制器的作用下产生使NAND Flash 可以工作的时序。采用二进制计数器作为地址生成器,根据NAND Flash的特性,地址只能按顺序进行写入,地址是由页地址加块地址构成的。首先把地址置为0,在测试算法按升序进行时,每执行完一段操作序列后,页地址加1 直到达到块内的最大页地址后,页地址复位为0,块地址加1,重复直至达到NAND Flash 的最大地址。进行降序操作的时候,从最大的块地址进行递减,但由于NAND Flash 的写特性,在块内进行写操作的时候,仍需进行递加操作。

4.2 FPGA 板极验证

MBIST 电路实现流程如图4 所示。根据bist_on信号判断NAND Flash 存储器处于什么工作状态:当bist_on 信号为0 时,NAND Flash 处于正常工作状态,可以通过外部的控制信号对其进行读取、编程等操作;当bist_on 信号为1 时,进入测试工作状态,此时,MBIST 电路中的向量生成器以及地址生成器在BIST控制器的控制下执行测试算法的一系列操作,并且比较器工作,根据对实际向量与期望向量比较的结果控制输出信号bist_error 用于从外部观察内建自测试的结果。为了验证改进March-like 算法的功能应用性以及MBIST 电路的可实施性,通过搭建FPGA 最小系统板进行板级验证。FPGA 最小系统板用尽可能少的硬件达到系统工作的基本条件,主要包括了FPGA 芯片、时钟电路、复位电路、供电电路以及JTAG 下载电路,为了后续工作实现,还包括了RS232 通信电路。

图4 MBIST 电路实现流程

5 实验结果分析

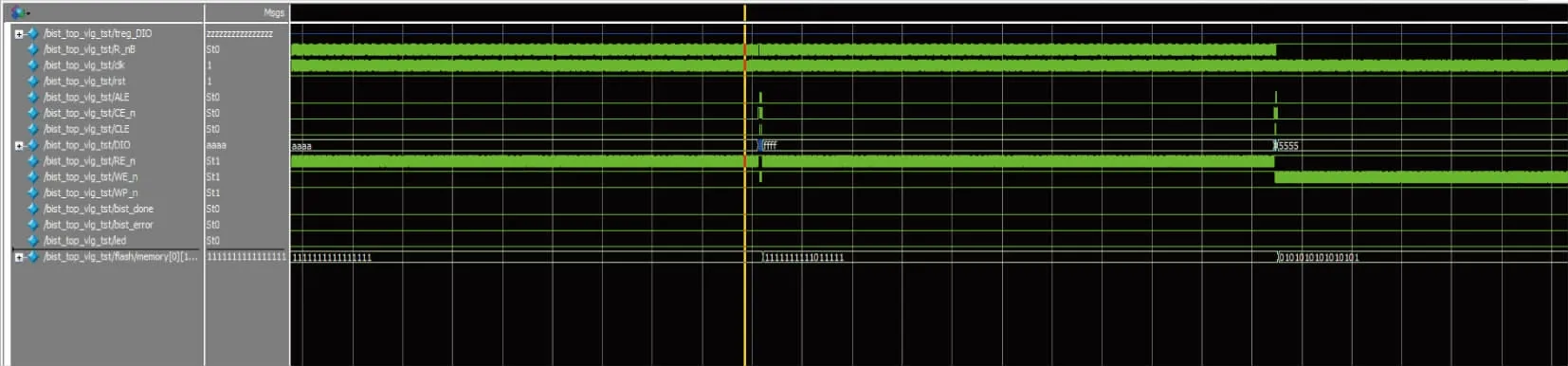

本文采用NAND Flash 的行为模型进行仿真验证,以MT29F16G16 为例,通过在行为模型中加入故障仿真用于完成对故障的检测。在行为模型中的擦除时间和编程时间相应缩短,仅用于验证测试算法的有效性。以测试一个块内存储单元为例,改进算法在存储器MBIST 电路中的仿真结果如图5 所示,bist_done信号拉高证明了测试已经完成,在bist_done 拉高前bist_error 信号一直保持低电平状态,表明在测试过程中未检测到故障。在行为模型中仿真故障类型以验证改进测试算法对于读干扰、读编程干扰故障的覆盖。

图5 改进算法在存储器MBIST 电路中的仿真结果

在NAND Flash 的行为模型中添加读编程干扰故障,首先擦除整个Flash,并在对Flash 的第一个块的读取过程中,随机选择一个地址写入16’hFFFD 用于模拟读编程干扰,March-like 算法对读编程干扰故障的检测结果如图6 所示,在读取后直接进行数据的写入操作,可以观察到bist_error 信号一直保持低电平状态,无法检测到读编程干扰故障。改进March-like 算法对读编程干扰故障的检测结果如图7 所示,改进后的March-like 算法进行两次读取操作,bist-error 信号拉高表明检测到故障的出现,可以检测到单元出现读编程干扰故障。

图6 March-like 算法对读编程干扰故障的检测结果

图7 改进March-like 算法对读编程干扰故障的检测结果

在March-like 算法中没有对读干扰故障的敏化操作,读干扰故障存在于连续读的过程中,在对Flash 的实际使用中,会存在连续读取的操作,因此在故障检测过程中,应包含对存储单元进行连续读取过程中可能会出现的故障的敏化操作。在行为模型中,当对同一页进行一次以上读操作后,对位于同一字线或同一位线的任意存储单元写入16’hFFDF,进行读干扰故障的仿真,结果如图8 所示,bist_error 信号有产生一个高电平,证明改进后的March-like 算法可以检测到读干扰故障。

图8 改进March-like 算法检测读干扰的仿真结果

将March-like 算法与改进后的March-like 算法进行对比分析,被测试的NAND Flash 块擦除时间为3 ms,页编程时间为600 μs,页读取时间为25 μs,改进后的March-like 算法长度为4(F)+4n(P)+12n(R),March-like 算法长度为6(F)+6n(P)+10n(R)。

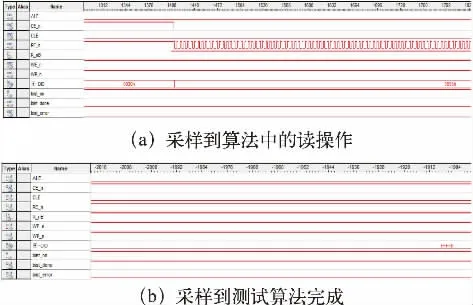

在FPGA 的最小系统板上对搭建的内建自测试电路进行板级验证,为了验证软件仿真结果与硬件板上实测结果是否一致,通过使用Quartus 工具中的SignalTap 进行在线调试。通过FPGA 对实物MT29F16G16 型NAND Flash 进行板级验证,通过SignalTap 采样的波形如图9 所示,可以证明测试已经完成,并且没有检测到故障。

图9 通过SignalTap 采样的波形

6 结论

本文讨论了NAND Flash 存在的故障类型,并对当前被大众采用的测试算法进行分析,针对目前故障覆盖最广泛的March-like 测试算法进行改进,相较于原March-like 算法,改进March-like 可以覆盖到读干扰、读编程干扰故障的检测,并且在测试时间上减少了30%,此外,改进March-like 测试算法也可以应用于NAND Flash 的机台测试。通过故障仿真模型验证了改进March-like 算法的故障覆盖情况(可实现对读干扰故障的全覆盖以及读编程干扰故障的检测),并通过FPGA 对NAND Flash 的测试验证了内建自测试电路可以正常工作。