四通道可拓展射电数字接收机系统

张 浩,王习东,刘高潮,李吉夏,吴锋泉,陈学雷

(1. 三峡大学理学院,湖北 宜昌 443002;2. 三峡大学计算机与信息学院,湖北 宜昌 443002;3. 中国科学院国家天文台,北京 100101)

射电信号观测是天体物理学不可或缺的重要探测手段,在探索宇宙大爆炸、恒星形成、宇宙物质能量特性等宇宙学问题的过程中发挥着极其重要的作用[1-2]。大气层存在一个波长覆盖0.1~104mm的射电观测窗口[3],是近年来射电天文快速发展的基础。虽然地基观测受大气层的限制,但由于建造方式经济,相关技术手段成熟,仍然是射电观测的主要手段[4]。

射电信号采集与处理系统是地基射电观测设备的核心部件[5],目前国外比较具有代表性的射电信号采集与处理系统有美国伯克利CASPER平台[6],最新的系统硬件有ROACH-2,SNAP-2和SKA_RAB等,在许多大型射电望远镜的数字终端中得到应用,如贵州500 m口径球面射电望远镜和上海天马望远镜均使用ROACH2构建终端系统[7];其次是欧洲DBBC系列接收机[8],早在2016年新疆天文台引进DBBC2系统并参与4 Gb/s速率的数据记录,助力天文学家对宇宙中更暗弱的射电源开展毫角秒分辨率的成图观测;除此之外,还有一些应用于空间观测的设备,如OLFAR,SURO等[9]。

国内对射电信号采集与处理系统也进行了一些探索,如文[10]设计的单个接收机模块可通过1 GS/s采样率对中频信号(750 MHz)过采样,实现4通道同步、采集处理及数据的实时传输;文[11]研制了高分辨率25~110 MHz天线阵太阳观测系统;文[12]研发具有自主知识产权的超导成像频谱仪,服役于德令哈13.7 m望远镜,工作频段为85~115 GHz;山东大学先后研制出分辨率为14位、4个输入通道、最高支持3 GSPS采样的射电天文数字接收机[13]和10~50 MHz地基低频射电天文数字接收机[4],前者可以直接对频率低于9 GHz的太阳射电信号进行采样,成本非常高,后者应用于新疆奇台站低频射电观测设备,但模数转换器的采样率为125 MSPS,采样带宽受限。目前,我国正积极推进的 “天籁实验”[14]、 “鸿蒙实验”[14]以及 “SKA-Low”[15]等项目都紧密围绕低频射电观测开展,低频射电信号采集与处理系统面临极大需求。

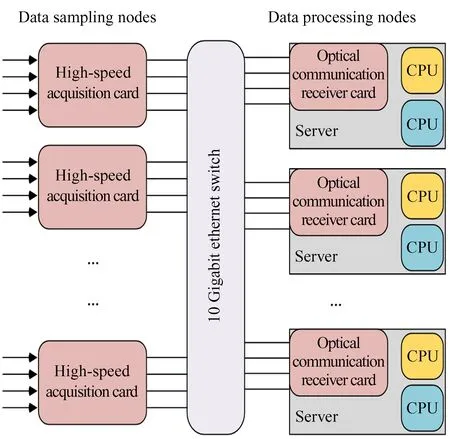

综上所述,目前国内外已有多种射电信号采集与处理系统,但应用在射电观测设备中时,由于缺乏自主知识产权、成本过高、不完全满足需求等因素带来诸多难题。本文针对射电信号采集与处理系统的性能需求和功能需求,基于现场可编程门阵列(Field Programmable Gate Array, FPGA)和高性能模数转换器等器件设计了射电数字接收机系统的两块核心板卡:4通道高速数据采集卡和光通信接收卡。利用这两种板卡可以构建如图1的大规模数据采集和处理系统,只需要增加高速数据采集卡和数据处理服务器的数量,就可以灵活扩展采集通道和数据处理规模,适用于大规模射电干涉阵列系统的建设和迭代更新。

图1 高速数据采集卡和光通信接收卡构建的大规模数据采集和处理系统框图Fig.1 Block diagram of large-scale data acquisition and processing system constructed by the high-speed data acquisition card and optical receiving card

1 系统总体方案设计

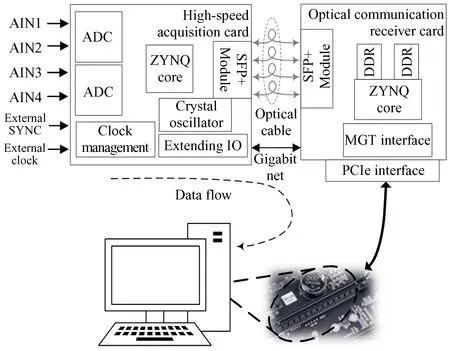

本文设计的高速数字接收机系统总体框架如图2,系统主要由高速数据采集卡、光通信接收卡、服务器3部分组成。图3展示了高速数据采集卡和光通信接收卡的实物及连接关系。高速数据采集卡的功能是实现模拟信号的数字化和信号处理,并将数据以Aurora 64B66B的通信方式上传到光通信接收卡;光通信接收卡在整个系统中是连接高速数据采集卡和服务器的中间组件,同时可以作为服务器的可动态配置协处理器,用于协助服务器端的数据处理;服务器端上位机软件用于控制高速数据采集卡和光通信接收卡的工作流程,并对采样数据进行记录和后处理。高速数据采集卡和光通信接收卡通过4条SFP+光缆和1条1 000 M网线连接,光缆用于大规模的数据传输,1 000 M网线用于两者之间的交互控制;光通信接收卡和服务器之间通过PCIe Gen2.0×8连接,可以完成大规模数据交互和控制交互。

图2 系统总体框架Fig.2 System overall frame

图3 系统实物Fig.3 System physical diagram

整个系统的数据流程如图2。射电观测装备的天线系统接收射电信号,并通过线缆将信号传入高速数据采集卡模拟采样通道AIN1~AIN4中的一个,由模数转换器进行采样、量化,完成射电模拟信号的数字化,数字信号在ZYNQ处理核心中经过时序调整,再通过SFP+模块发送给光通信接收卡。光通信接收卡从SFP+模块接收数据并缓存到DDR存储空间,服务器端上位机软件可通过PCIe接口将缓存在光通信接收卡中的数据提取到服务器中进行存储和后处理。整个系统可以实现4通道同步采样,每个通道都能够实现300 MSPS的独立采样。同时,高速数据采集卡预留扩展IO接口,可接收外同步信号和外部时钟输入,用于实现多元阵列中多机同步机制。

基于上述技术方案,高速数据采集卡和光通信接收卡将模数转化和数据处理的功能分离,数据采集卡可与天线紧密部署,避免模拟信号因长距离传输而导致信号畸变;高速数据采集卡集成4路最高串行速率可达10 Gbps的SFP+光通信接口,通过光信号将数字信号传输到服务器。系统具备线路布设简单、抗干扰能力强、长距离传输的特性,并且该接口可以通过编程部署多种不同的通信协议,用于兼容多种接收设备,能够最大程度地利用已经部署的数据接收与处理设施。基于图1的框架,将高速数据采集卡部署为采样节点并接入10 G局域通信网,可以实现更多通道的同步采集功能,在大规模干涉阵列中,对更多天线单元进行射电信号采集。

2 高速数据采集卡软硬件设计

2.1 方案设计

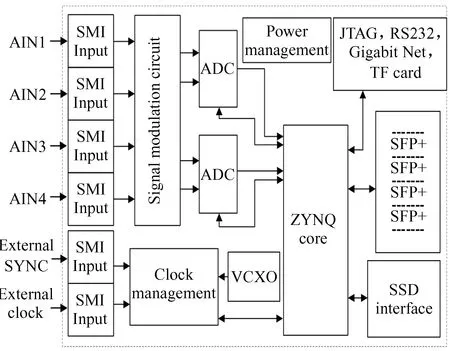

高速数据采集卡需要将输入的4路模拟信号量化成数字信号,最终将数据通过光缆输出到其他设备。如图3,AIN1~AIN4是4路模拟信号的输入接口,信号经过信号调理网络后输入模数转换器,完成模拟信号的数字化,量化结果发送给ZYNQ处理核心,并进行数据的时序调整、预处理,再通过4路SFP+通信接口输出到光通信接收卡。模数转换器和ZYNQ通过JESD204B通信协议实现数据交互。该协议基于SerDes高速串行接口技术,广泛应用于高速模数转换器,可以减少电路设计中的冗余布线。高速数据采集卡通过专用时钟管理器,并结合高性能压控振荡器分别为模数转换器、ZYNQ处理核心等提供高质量的同源时钟,预留多个基础接口和SSD存储接口、SFP+通信接口,满足系统工作和数据处理、存储的需要。

图4为硬件设计方案中对外开放了时钟管理器的外同步输入接口和外部参考时钟输入接口,可分别接入GPSDO[16](GPS驯服频率振荡器)提供的同步触发信号和参考时钟信号,系统基于这两个信号实现多个节点之间的时钟同步,实现多机同步采集。多机同步技术框架如图5。基于此技术方案,我们可以实现高速数据采集板在多元阵列中的部署和应用。

图4 高速数据采集卡硬件框架Fig.4 High-speed data acquisition card hardware framework

图5 多机同步技术框架Fig.5 Multi-machine synchronization technology framework

2.2 硬件设计

高速数据采集卡主要由信号调理电路、两个模数转换器、一个时钟管理器、一个型号为xc7z100的ZYNQ处理核心、SFP光通信接口、SSD存储接口和电源电路等组成。

高速数据采集板中每个模拟输入通道单独适配一个信号调理电路,电路原理如图6。该调理电路由一个通带范围为4.5~3 000 MHz巴伦转换器和RC滤波电路组成,将输入高速数据采集板的单端模拟信号转换为差分信号,滤波后输入模数转换器进行采样和量化,完成模拟信号的数字化。

图6 信号调理电路Fig.6 Signal conditioning circuit

ADS54J60是一款低功耗、1.2 G带宽、16位采样精度、1.0 GSPS采样率的双通道模数转换器,可提供-159 dBFS/Hz的噪底,以超低功耗在宽输入频率范围内提供出色的无杂散动态范围。该器件支持JESD204B通信接口,减少了PCB线路的冗余设计,从而实现比LVDS接口更高的系统集成度。器件内部集成模拟输入缓冲器,可以减少采样保持的毛刺脉冲能量,在宽频率范围内提供统一阻抗。

时钟管理器使用LMK04828,该器件具有集成式压控振荡器(Voltage-Controlled Oscillator, VCO),且符合JESD204B标准对超低噪声时钟抖动的要求,对外提供7组同源差分时钟信号,分别为模数转换器、ZYNQ核心、SSD存储接口等提供稳定可靠、高质量的同源时钟;同时,在多元阵列中应用时,该器件是实现多个设备间同步采样的关键,如图5,将该器件上的同步信号SYNC、一路输入参考时钟信号通过SMA接口向外部开放,通过外部的参考时钟和同步信号实现多个设备的时钟同步,实现设备的阵列化部署。

采集卡主控使用ZYNQ SOC,该器件集成FPGA和ARM,拥有大量的可编程资源如Block RAM,DSP52E1和LUT等。同时,有4组高速串行收发器模块可供使用,是SerDes高速串行接口技术的硬件基础。两个模数转换器、一个SFP+ Quad通信接口、一个SSD存储接口分别占用一组高速串行收发器。同时,ZYNQ处理核心通过3组SPI接口和多个通用IO接口管理和配置模数转换器及LMK04828器件的工作。图7描述了高速数据采集卡中各部分的接口连接关系,其中从时钟管理器输出的虚线指示了由LMK04828器件为各个部分分配的同源时钟路径。图8展示了高速数据采集卡的实物样机。

图7 高速数据采集卡硬件接口图Fig.7 High-speed data acquisition card hardware interface

图8 高速数据采集卡实物样机Fig.8 High-speed data acquisition card physical prototype

2.3 软件设计

图9为高速数据采集卡FPGA程序框架,每片模数转换器芯片可同时对两路模拟信号进行采样,两片模数转换器实现4通道的同步采样。模拟信号输入模数转换器,由模数转换器完成模拟信号的缓冲、量化并通过JESD204B通信协议将数据发送到ZYNQ处理核心,完成数据的时序调整并通过4路SFP+接口将处理后的数据通过光纤输出。两个模数转换器的300 MHz采样时钟信号由时钟管理器LMK04828分别独立提供,ADS54J60器件在该时钟的基础上运行,对AIN1~AIN4输入的模拟信号进行300 MSPS速率的采样和16 bit精度的量化。每片ADS54J60上两个通道的量化结果通过芯片内部JESD204B通信逻辑单元整合打包后发送给ZYNQ处理核心。

图9 高速数据采集卡FPGA程序框架Fig.9 FPGA program framework of high-speed data acquisition card

ZYNQ处理核心和模数转换器之间的通信包含基于通用IO实现的SPI通信和基于高速专用IO实现的JESD204B通信。ZYNQ处理核心中构建的JESD204B通信IP核通过高速串行收发器模块接收模数转换器发送的数据码流并进行解码还原,每个模拟通道的采样数据分别对应一个64位宽的AXI-Stream接口,数据流在数据缓存逻辑中进行时序调整,处理好的数据通过Aurora 64B66B接口逻辑输出,Aurora 64B66B将数据分成4路,通过高速串行收发器模块由4条光缆进行传输。

高速数据采集卡的程序设计分为FPGA和ARM两个部分,图10是开发工具vivado中搭建的高速数据采集卡FPGA工程模块图,主要有Hier_ZYNQ7模块、Hier_ADC模块、AuroraBlock模块、CDC_Buffer模块和AXI Quad SPI模块等。Hier_ADC模块接收模数转换器发送的数据,并将数据传递到CDC_Buffer模块进行帧对齐,随后对齐的数据下发到AuroraBlock模块缓存,并在Aurora 64B66B模块的控制逻辑下将数据通过SFP+光通信输出。Hier_ZYNQ7模块中封装了ARM-A9处理器,可通过AXI-Lite总线控制各个功能模块的寄存器配置,通过AXI GPIO模块复位Hier_ADC模块和外部的器件,通过AXI Quad SPI模块对外部的LMK04828和ADS54J60器件进行功能配置。

图10 高速数据采集卡FPGA工程模块图Fig.10 High-speed data acquisition card FPGA engineering module

ZYNQ处理核心的程序固件包括3部分:FSBL(第1阶段引导程序)、Bitstream(可编程逻辑配置文件)和elf(ARM程序可执行文件)。SOC上电启动,依次加载FSBL,Bitstream和elf文件,ARM应用程序在执行过程中,通过AXI总线访问和控制可编程逻辑中的各功能模块。SOC启动流程如图11。SOC在加载完Bitstream后,可编程逻辑中就实现了图10中的各个功能模块。在ARM端的程序中,依次进行初始化SOC平台、初始化AXI GPIO和AXI Quad SPI等,并完成各功能模块的配置;随后,为模数转换器及时钟等器件上电、复位;完成复位工作后,配置LMK04828时钟芯片,使其正常工作,为各模块提供时钟信号;各个模块的时钟信号输出后,配置ADS54J60模数转换器,使其正常工作。完成以上步骤,程序会在系统运行过程中不断检测系统的工作状况,并将检测的状态参数向用户输出。

图11 高速数据采集卡系统程序流程图Fig.11 High-speed data acquisition card system program flow chart

3 光通信接收卡及上位机软件

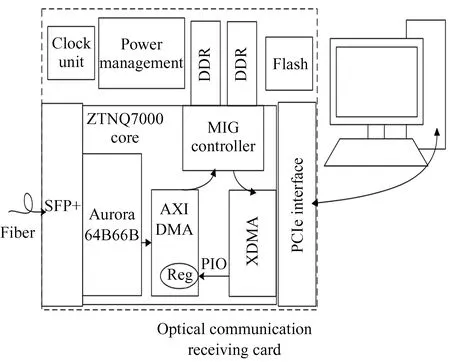

光通信接收卡基于米联客MZ7100FB开发板实现,图12是光通信接收卡FPGA程序框架。高速数据采集卡发送的数据经过光纤传送到光通信接收卡的SFP+接口,ZYNQ 处理器中可编程逻辑的Aurora 64B66B模块驱动SFP+接口模块接收数据,并通过AXI-Stream接口发送到AXI-DMA模块,AXI-DMA模块在XDMA模块的控制下将数据流指向写入DDR缓存。板卡的PCIe接口连接到服务器的PCIe插槽,服务器主机通过PCIe协议与光通信板卡中的XDMA功能模块交互。上位机软件通过XDMA功能模块的PIO功能接口对板卡内AXI-DMA功能模块进行配置,同时,通过XDMA功能模块的AXI-full接口访问光通信接收卡中DDR的缓存空间并获取数据到服务器。

图12 光通信接收卡FPGA程序框架Fig.12 FPGA program framework of optical communication receiving card

光通信接收卡只涉及FPGA的程序设计,图13是开发工具vivado中搭建的光通信接收卡FPGA工程模块图,其中hier_aurora功能模块驱动SFP+光电转换器接收光纤传输的数据信息,并从AXI-Stream接口输出有效数据到PreDMATrans逻辑处理模块进行组帧处理;AXI4-Stream Clock Convert逻辑模块完成时钟域的转换,将hire_aurora模块的数据同步到MIG模块的接口时钟域,随后利用AXI-DMA模块批量缓存到DDR空间;hire_xdma功能模块是光通信板卡与服务器进行数据交互的核心模块,是服务器读写光通信板卡中各个模块的寄存器配置、快速访问DDR存储器数据的基础。

图13 光通信接收卡FPGA工程模块图Fig.13 Optical communication receiving card FPGA engineering module

光通信接收卡的程序执行流程如图14。首先,程序执行AXI-DMA的配置工作,然后开启DMA传输,将hire_aurora模块AXI-Stream接口输出的数据缓存到hire_DDR模块的片外DDR存储空间,等完成128 MB数据缓存,便通过hire_xdma模块向服务器发送一个中断信号,告知服务器数据帧缓存完成,上位机软件可通过hire_XDMA功能模块获取DDR存储空间中的数据。光通信接收卡在完成128 MB数据缓存后发出中断信号的同时,程序的逻辑会对当前帧编码进行区分,如果是奇数就将下一帧的地址空间分配到偶数帧存储空间,如果是偶数帧就将下一帧的地址空间分配到奇数帧存储空间,即基于乒乓操作的地址重定向,其中帧地址是DDR中预分配存储块的基地址,将写操作的地址空间和读操作的地址空间进行隔离,有效避免数据冲突。测试过程中,上位机软件通过PCIe接口向光通信板卡的一块8 MB的DDR存储空间进行数据读写,并计算数据吞吐率。图15是上位机软件进行PCIe带宽测试的效果图,结果表明,服务器和光通信板卡的PCIe通信带宽可达到1 450 MB/s。

图14 光通信接收卡程序流程Fig.14 Optical communication receiving card program flow

图15 PCIe带宽测试Fig.15 PCIe bandwidth test experimental renderings

4 测试与实验

4.1 幅频特性

实验过程中,通过RIGOL DG4062信号发生器产生一个幅度为2 000 mV、频率范围为10 kHz~50 MHz的正弦波线性扫频信号,经过1分4功分器分成4个幅度相同且相位一致的信号。由同轴线缆分别输出到高速数据采集板的模拟输入端口AIN1~AIN4,并通过上位机软件记录采样的扫频数据。利用Matlab工具还原数据并绘制如图16(a)幅度频率响应图,图16(b)展示了多个幅度相同、频率不同输入信号的局部波形。实验表明,本系统在4.5~50 MHz的频带是一段相对平坦的频率响应区间,模数转换器量化幅度相对于输入信号幅度衰减约6.5 dB。结合奈奎斯特定理,系统理论上可采样的模拟信号频率范围覆盖4.5~150 MHz,后期将在具体的应用场景中进行参数标定。

图16 系统幅频关系曲线Fig.16 Amplitude-frequency characteristic curve of system

4.2 幅相特性

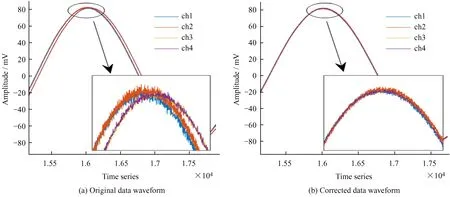

实验过程中,通过RIGOL DG4062信号发生器产生一个2 000 mV@10 MHz的正弦波信号,经过一个1分4功分器分成幅度相同且相位一致的4个信号,并由同轴线缆同步输出到高速数据采集板的模拟输入端口AIN1~AIN4。通过上位机软件记录采样数据并利用Matlab绘制出图17(a)幅相一致性测试结果图。经过分析,属于同一片模数转换器芯片的两个独立采样通道幅度、相位几乎一致;两片模数转换器之间存在固定42个采样时钟的相位延时,且经过相位调整后4个独立通道间相位延时小于3.3 ns,修正后的效果如图17(b)。

图17 幅相一致性测试结果Fig.17 Consistency test results

4.3 噪声特性

实验过程中,将高速数据采集板的4个模拟输入通道分别接入信号发生器产生的10 mV白噪声,通过上位机记录高速数据采集板采集信号的数据,考虑50 Ω输入阻抗情况下,在Matlab中计算得到4个通道的噪声功率谱密度分布如图18,底部噪声分布在-129 dBm/Hz,与频谱仪观测到的结果吻合。

图18 噪声功率谱密度图Fig.18 Noise power density spectrum

通过图18可以发现,系统在100 MHz和75 MHz处有两个相对较强的噪声点,但都小于-100 dBm/Hz,其中100 MHz处的噪声可能是压控振荡器的信号耦合到输入通道导致的。实验通过对频率固定为10 MHz,幅度不同的模拟信号进行采样,经过多组测试,结果表明,系统对频率为10 MHz的模拟信号进行采样时的动态幅度范围为4~4 000 mV。通过对4 mV小信号和4 000 mV大信号进行采样,经Matlab对采样数据进行还原并绘制如图19(a)、图19(b)的时域波形。从图19(c)可知4 mV信号相对于噪声仍具有较高的辨识度,通过滤波处理后,得到图19(e)还原后波形;由图19(d)可知,在输入信号幅度为4 000 mV时,噪声几乎无影响。

图19 无失真信号采集实验结果Fig.19 Distortion-free signal acquisition experimental results

4.4 功率谱特性

实验过程中,通过RIGOL DG4062信号发生器产生一个16 V@10 MHz的正弦波信号,经1分4功分器分成4路幅度相同、频率相同、相位一致的信号,并通过同轴连接线输入高速数据采集卡的4个模拟输入通道,上位机记录系统采样数据并经过Matlab对数据进行8 192个样本点的快速傅里叶变换处理,得到如图20功率谱分析结果,系统性能参数测试结果如表1。

表1 系统性能参数测试结果Table 1 Test results of system performance parameters

图20 信号采样功率谱分析结果Fig.20 Results of signal sampling power spectrum analysis

5 结 论

本文基于ADS54J60,LMK04828和ZYNQ7000 SOC等核心器件设计实现了一种适用于射电观测的4通道高速数字接收机系统。该系统由高速数据采集卡、光通信接收卡和服务器3部分硬件设备组成,采用基于Serdes的高速串行接口技术,实现高带宽数据吞吐;采用FPGA+光通信+FPGA的技术方案,不仅可以应用于采样点与数据中心距离较远的场景,同时后期可以通过FPGA的并行计算能力加速数据的预处理流程;使用GPSDO实现多机同步机制,为多元阵列中的同步采样难题提供解决方案。本文研制的高速数据采集板卡和光通信接收卡,可以应用在未来大规模可拓展射电干涉阵列的数据采集系统中,同时为下一步通过更详细的射电时域信息分析射电现象的研究提供数据来源。