基于数字中频预处理专用芯片的SiP设计

张 帆

基于数字中频预处理专用芯片的SiP设计

张 帆

(中国电子科技集团公司第二十研究所,西安 710068)

随着电子科学技术的快速发展,系统级封装(SiP)技术成为实现信号处理系统小体积、轻重量、低功耗及低成本方面要求的又一有效途径。针对数字中频预处理应用要求,提出了一种将波形产生、数字滤波处理、数字信号上传和下发及时钟和同步等复杂预处理功能集成设计的方法,采用PBGA225封装形式,大大缩小了系统体积和功耗。

中频预处理专用芯片;系统级封装;微系统仿真

0 引言

随着电子科学技术的快速发展,工业、军工等行业对半导体芯片的轻重量、低成本、小型化以及性能的要求越来越高,先进的制造工艺水平和模块化的系统架构同样促使信号预处理系统的设计思想发生了根本性的变化。系统级封装(System in Package,SiP)技术是一种可以把多种功能芯片在有限空间外壳中结合成整体系统的封装技术,在功能上实现信息感知、传输、处理、分析、决策和执行的融合,在信号预处理系统中采用SiP设计技术,能够在有限空间中保持系统存储大小和性能指标不变,同时还能降低系统的尺寸、重量以及能耗,这对信号预处理系统的小型化、高可靠性、高性能以及轻量化等方面具有重大意义[1-4]。

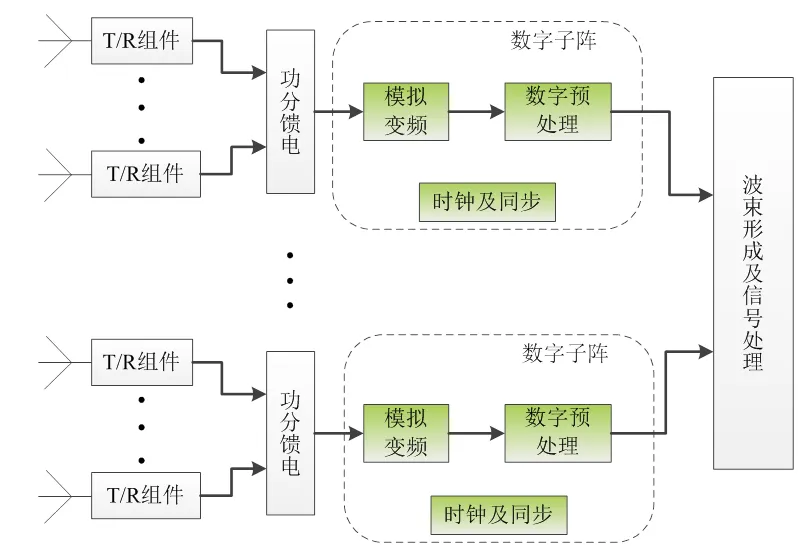

中频数字接收机因其性能优秀、灵活性强,目前广泛应用于各种无线电接收系统[5]。以某相控阵雷达阵面系统为例,其框图如图1所示,发射时,数字子阵负责将一路数字基带信号,经过数字预处理和数模变换(Digital to Analog Convertor,DAC),两次上变频及一系列放大之后,功分至发射/接收组件(Transmitter and Receiver,T/R),经末级功放推动后,由宽带微带天线辐射至空间;接收时,对回波信号经多路T/R通道后,合成为一路回波信号,然后再经过两次下变频及系列放大后产生中频信号送至数字子阵,经由模数转换(Analog to Digital Convertor,ADC)、数字下变频及预处理后将数据流通过光纤传送给数字波束形成及信号处理分机。

图1 阵面系统组成框图

当前雷达阵面系统中数字子阵主要通过分立器件在硬件电路板实现,其基本功能框图如图2所示,主要采用现场可编程逻辑器件(Filed- Programmable Gate Array,FPGA)、ADC、DAC及锁相环芯片(Phase Locked Loop,PLL)等核心元器件实现宽带数字信号的波形产生、数字滤波处理、数字信号的上传和下发及时钟和同步等复杂预处理功能[6-7]。该解决方案体积大、功耗高,最重要的是无法满足阵面级高精度同步的要求,严重影响了雷达性能和精度;以某型小型化数字子阵模块为例,该解决方案外形尺寸300 mm×800 mm×8 mm左右,功耗约8 W,在动辄上装近千个数字子阵模块的系统中,体积和散热成为限制系统指标进一步优化的瓶颈[8]。

图2 当前成熟数字子阵原理框图

采用微系统设计方法,以数字中频预处理专用芯片为基础,搭配成熟模拟变频芯片及必要的外围存储和阻容网络,在单个封装内实现数字中频预处理系统核心功能,将大大减小数字子阵系统体积,满足数字子阵的小型化、轻型化设计需求;在功耗和成本优化方面成效显著。基于中频预处理的SiP系统原理框图如图3所示。

图3 基于中频预处理芯片的SiP原理框图

1 研制流程概述

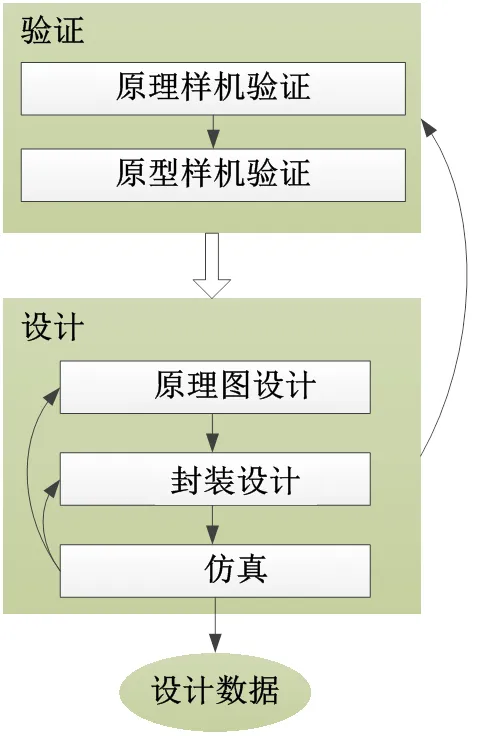

SiP设计开发步骤主要包括方案设计及验证、基板和封装设计、制造加工共三部分[9],本文主要完成方案和设计两部分。

方案设计及验证主要包含原理样机验证和原型样机验证两部分,以当前成熟产品为测试硬件平台,依托FPGA实现数字预处理功能,主要验证整体系统方案的可行性;原型系统验证为以封装片为硬件载体形式,搭建自研芯片+模拟变频芯片+FLASH的测试硬件平台,进行SiP方案验证。

基板及封装设计主要包括原理图设计、封装设计和仿真验证三部分,原理图设计主要包含互连关系设计、供电方案设计等,封装设计主要包含布局设计、基板设计、走线设计和键合方式设计等,仿真验证主要包含热、电、机械性能仿真等,最终生成可用于加工制造的基板数据和封装加工要求。研制流程图具体如图4所示。

图4 研制流程

2 方案设计及验证

原型验证系统主要完成SiP系统功能验证,最终制定SiP具体实施方案,在初样研制阶段,SiP原理图设计过程中,通过对系统功能分析,结合裸芯应用电路分析,最终完成SiP原理图设计,主要包括内部互连关系、电源分配、外部接口设计、外部引脚(Ballmap)文件制定、测试接口规划、外部应用电路分析及初步确定等。在原理图设计过程中,需要随时通过原型验证系统对SiP原理图进行验证。

原理图设计完成后,通过基板版图设计及仿真,确定最终的基板制造方案,主要完成基板尺寸规划、裸芯叠层设计、电源规划及分析、基板走线及电性能仿真,并通过热、机械及电性能仿真结果进行调整,最终形成SiP设计数据交由加工制造厂进行基板制造和封装。

3 基板及封装设计和仿真

基板是SiP封装中承载裸芯的物理载体,根据裸芯型号和SiP功能要求的不同,SiP的基板都需要经过详细设计,在设计过程中,通过信号完整性、电源完整性、机械和热等方面的仿真,对详细设计作出调整,最终生成用于加工制造的设计数据 文件[10]。具体的设计实现步骤如下:

1)基板设计

封装基板的设计是一个反复验证的过程,需要考虑整体方案要求、封装结构特点、组装工艺的可行性等因素,经反复验证后形成最终设计,将封装的风险降到最低,满足项目整体的可实施性及后续可能涉及的可靠性等问题。该过程针对封装的结构、内部集成的芯片选型、封装工艺的选择、封装基板的工艺选择等问题,进行充分的调研和分析,确保项目的可实施性、可设计性和可制造性都能满足需求。封装设计主要有以下步骤:

(1)通过前期方案的论证,根据裸片信息以及连接关系等附件,绘制封装的原理图,并确认电气连接的正确性。

(2)根据项目的指标要求,给出设计时采用的叠层结构、材料、厚度、布线层以及电源地层的分布要求,同时给出布线时需要采用的工艺等级规范(线宽、线距)、阻抗要求规范、长度要求规范以及相关的引脚分布。

(3)根据阻抗、叠层和长度,以及平面的完整性、参考回路的完整性、电源通道的合理性、封装的组装工艺可实施性等进行基板设计。

(4)封装基板设计完成后结合仿真进行相应的调整直至设计完成。

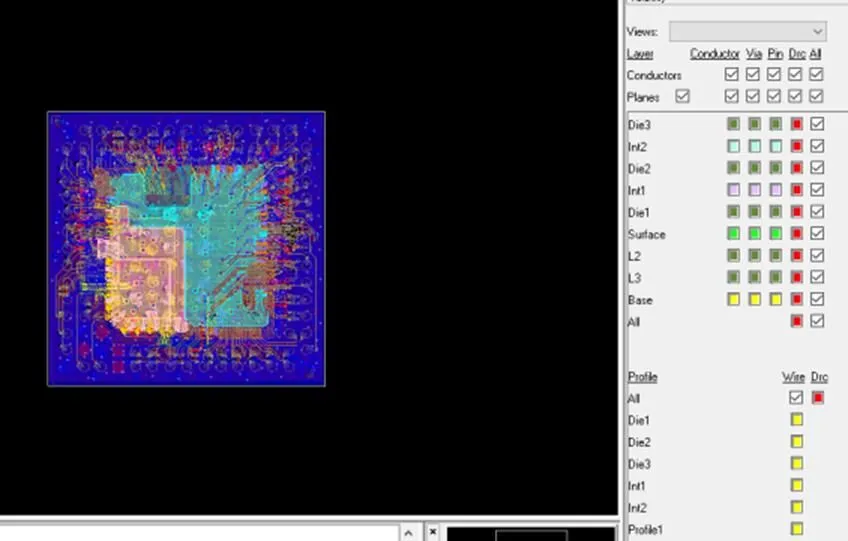

基于数字中频预处理专用芯片的SiP封装基板采用4层板,整体厚度400 μm,层叠设置表如表1所示。最终的基板设计图和各层布板设计如图5所示。

表1 SiP层叠设置表

图5 SiP封装基板设计图

2)设计仿真

在微系统设计中,复杂的互联以及传输链路中的各种不连续结构,例如金线、过孔、绕线和被动元器件等,都会对整个系统性能造成影响;系统内部的各种电磁干扰问题和信号完整性问题,各种过孔间耦合、线间耦合,以及这些耦合间的相互作用都会给系统带来额外的不确定因素,都会影响产品的可靠性。需要借助仿真软件对产品进行模拟分析,精确定位到具体的设计问题,找出其中的薄弱环节,对其进行优化,从而提前规避可能出现的风险,提高产品的可靠性。基于数字中频预处理专用芯片的SiP应用与设计主要包含信号完整性仿真、电源完整性仿真、机械仿真和热仿真四个方面。

(1)信号完整性仿真

信号完整性仿真主要为了保证SiP设计中信号走线的电性能满足设计要求,主要包括走线阻抗计算、前仿真和后仿真三部分,以下以过孔为例对信号完整性进行说明。

①走线阻抗计算

走线阻抗计算是根据版图叠层信息计算走线线宽,为版图设计提供指导。仿真采用传输线建模和分析软件TmlExpert,TmlExpert提供了一个三维小型化系统封装内信号通道,包括键合金线和基板走线的阻抗控制的快速分析方法,它可以很方便地计算传输线特征阻抗、传输线等效集总参数、时域反射阻抗、多路信号间的近端串扰和远端串扰、能量耦合、信号传输和信号串扰比和,同时还能看到信号时延和信号抖动,根据这些参数,可以直接找出设计中的阻抗不匹配点并改变线宽或间距来优化串扰耦合。在TmlExpert软件中调用单端微带线和差分微带线模板,计算出TOP、Bottom走线层单端和差分线线宽分别为20 μm和40 μm。

②过孔、管脚阻抗前仿真

通过软件自带的过孔和管脚参数化模板,在版图布局布线前优化过孔和管脚等阻抗不连续结构,减少对信号链路的影响,为版图设计提供指导。采用SiP管脚优化工具ViaExpert和SiP封装S参数模型分析工具SnpExpert。SiP管脚优化工具提供了一种快速和准确的方法来分析过孔的影响,可同时适用于前仿和后仿阶段。S参数模型分析工具提供快速了解系统中无源互连器件电气特性的方法;支持多线程快速导入各种版本的封装S参数数据,支持多端口的单端或差分封装S参数批处理分析。

利用ViaExpert中集成的过孔模板快速创建3D过孔模型,在过孔模板中一次编辑Stackup、Signal Via和Ground Via等区域,在优化过孔阻抗时,通常采用优化Antipad的方式达到优化过孔阻抗的目的。点击工具Project→Model→3D view查看建立的3D模型,如图6所示。

图6 过孔3D视图

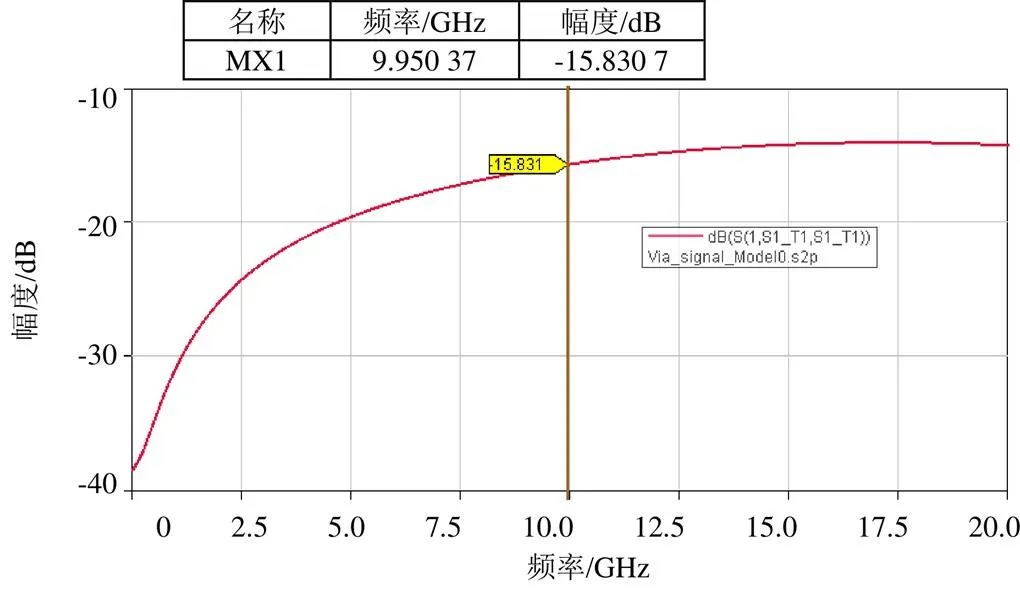

模型建好后,设置求解器中扫频方式和起止频率等求解参数并运行ViaExpert,根据仿真结果图7可知:10 GHz带宽以下回损小于-15 dB,因此过孔引入的阻抗不连续对信号链路影响较小,本设计为中频信号处理,走线信号频率远小于10 GHz;过孔阻抗最大跳变为52.4 Ω。

图7 通孔回损仿真图

③过孔及信号链路后仿真

基板及封装完成版图设计后,通过后仿真可以分析版图设计中过孔和管脚等结构对信号链路的影响,解决封装基板布局布线的管脚优化和走线间相互串扰问题。仿真工具与前仿真一致。

过孔后仿真先导入版图设计文件,选择需要导入的网络,为防止仿真数据庞大,按照布局对版图进行切割,并对选中的信号进行建模,包括对基板层叠信息、端口分布等参数进行设置,采用插值扫频,求解器采用三维全波高精度电磁仿真精确模式,仿真带宽到1 GHz。根据仿真结果图8可以看出有效数据信号链路在1 GHz频段内有较好的阻抗匹配,回损在-30 dB以下。

图8 回损仿真结果

信号链路仿真优化主要是评估封装版图中高速、时钟、控制信号等关键信号阻抗和串扰大小等信号完整性问题。采用Hermes 3D和高速射频通道模型分析工具ChannelExpert来完成。导入版图设计文件后进行版图切割,并进行层叠信息设置,添加端口信息,网格剖分采用adaptive精确模式进行仿真。根据仿真结果可知低频信号链路在1.5 GHz频段内有较好的阻抗匹配,回损在-15 dB以下。

(2)电源完整性仿真

电源完整性仿真主要用于评估封装版图中电源网络直流压降、电流密度及过孔和金线等通流问题。采用Hermes PSI进行仿真,加载版图设计软件,创建直流仿真流程,指定仿真的电源网络,为电源网络中的电阻赋置模型,设置电源网络电压及负载电流大小。由仿真结果可知:1.8 V电源网络的直流压降最大值为3.6 mV,小于设计规范的54 mV,版图设计中1.8 V电源不存在压降风险,电流密度分布均匀,不存在通流瓶颈区域。

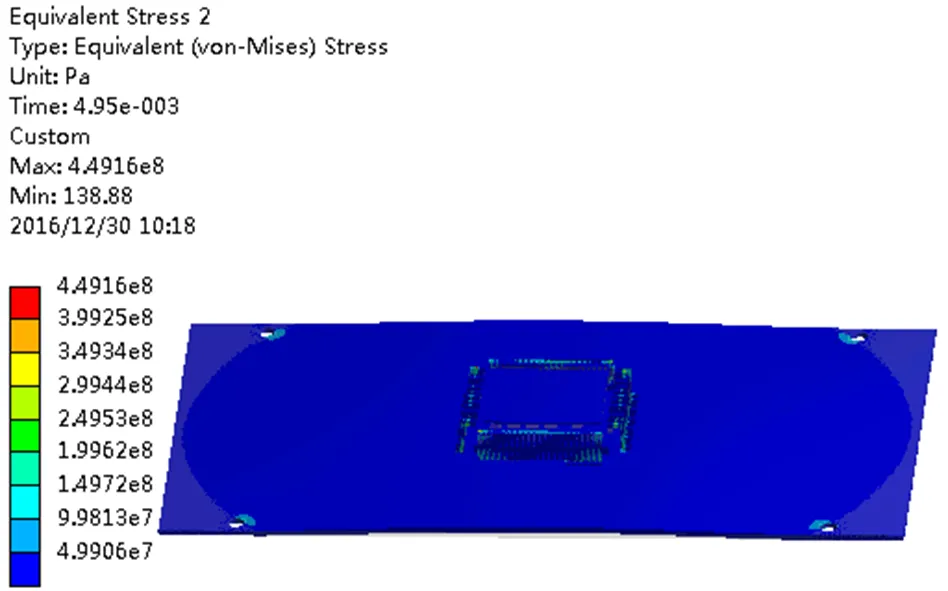

(3)机械仿真

封装过程中,要经历无源器件焊接、芯片贴片、打金线、灌封和植球等过程,温度会发生剧烈变化,即从25℃升到160℃,再到250℃,随后快速冷却至常温25℃,在升温与降温过程中,封装基板、贴片胶和Molding Compound等材料的热膨胀系数(Coefficient of Thermal Expasion,CTE)之间的匹配与整个封装结构受力息息相关,CTE失配会导致封装结构产生形变、翘曲,当形变及翘曲发生一定程度时,表贴(Surface Mount Technology,SMT)焊点、封装内部焊点及芯片等都会被拉裂损坏;同时,在各种冲击振动及离心力实验过程中所导致的焊点、芯片及封装管壳的形变及应力都必须满足它们所承受的形变应力范围,通过机械仿真可以对此类情况进行评估和优化,保证封装体机械性能。基于ANSYS软件在保证结构基本特征的前提下对产品封装进行简化,保留对结构力学性能影响较大的关键因素,250℃版图机械仿真结果如图9所示,可知封装版图上无应力集中现象。

图9 机械仿真结果

(4)热仿真

热仿真主要基于产品功耗参数评估SiP中各芯片最高结温及版图温度分布,规避SiP散热问题。采用Hermes PSI软件热仿真模块Therma进行仿真。导入SiP封装设计文件后,进行热参数设置,启动热仿真流程,热仿真结果如图10所示,可知结温温度为82.3℃,满足器件125℃结温约束。

图10 热仿真结果

4 加工封装

设计数据完成之后,通过基板准备、晶圆减薄、划片、装片及SMT回流焊接、键合、包封、打标、植球、切割和光检等封装流程,最终完成SiP加工。

5 结语

本文从研制流程、基板及封装设计、电、力和磁仿真等方面对基于数字中频预处理专用芯片的SiP设计过程进行了介绍,针对该微系统的特殊要求,提出了具体有效的解决措施,并给出了最终设计结果。

[1] 李扬,刘杨. SiP系统级封装设计与仿真[M]. 北京:电子工业出版社,2012.

[2] Christopher M. SiP(系统级封装)技术的应用与发展趋势[J]. 中国集成电路,2004(12):55-59.

[3] Choudhury D. 3D integration technologiesfor emerging microsystems[C]//Proceeding of IEEE MTT-S Int. Anaheim,CA,USA,2010:1-4.

[4] Gaio N,Gao L,Cai J,et al. System-in-package solution for a low-power acive electrode module[C]. Engineering in Medicine & Biology Society. ConfProc IEEE Eng Med BioSoc,2014:5016-5019.

[5] Interactive Circuits & System Ltd. Software Defined Radio(SDR)Products for Radio and Radar[EB/OL]. http://www.ICS.com,1999-09-26.

[6] 闫温合,胡永辉,李瑾琳,等. 应用于数字下变频中CORDIC算法的FPGA实现[J]. 时间频率学报,2014,37(1):34-40.

[7] 杜勇. 数字滤波器的MATLAB与FPGA实现[M]. 2版. 北京:电子工业出版社,2014.

[8] 马跃,牛涛涛. 基于Cortex M3的雷达中频处理SoC芯片设计[J]. 电子世界,2019(6):162-163.

[9] GARROU P E,TURLIK L. 多芯片组件技术手册[M]. 王传声,叶天培,等,译. 北京:电子工业出版社,2006.

[10] 李扬. SiP系统级封装设计仿真技术[J]. 电子技术应用,2017,43(7):47-50+54.

Design of SiP Based on Intermediate Frequency Pre-Processing ASIC

ZHANG Fan

With the fast development of electromagnetic technology, System in Package (SiP) becomes another effective way to realize small size, light weight, low power and low cost in signal processing system. Aimed at matching the application request of digital intermediate frequency pre-processing system, a method of integration of wave generation, digital filter, uploading and distribution of digital signal thus clock and synchronization is proposed. PBGA225 package which decreases the volume and power obviously is adopted.

Intermediate Frequency Pre-Processing ASIC; System in Package; SiP Simulation

TN915.04

A

1674-7976-(2023)-05-358-06

2023-06-19。

张帆(1985.09—),陕西咸阳人,硕士,高级工程师,主要研究方向为微电子。