红外焦平面列级数字化技术

李敬国,袁 媛,于 艳

(中国电子科技集团公司第十一研究所,北京 100015)

1 引 言

随着红外技术和集成电路技术的发展,列级数字化技术已经成为红外探测器数字化的一种重要技术途径,列级数字化技术不仅对外部噪声具有很好的抗干扰能力,同时可以有效规避红外探测器外部电子系统的非线性和功耗,提高红外探测器灵敏度、小型化、智能化水平。

2 数字化技术

红外焦平面数字化技术途径主要分为三种:芯片级数字化技术、列级数字化技术、像素级数字化技术。

2.1 芯片级数字化技术

传统芯片级数字化技术是在读出电路芯片上通过一个ADC完成所有像元信号的模数转换,对于M(列)×N(行)阵列,芯片级数字化一帧数据的转换速率为:

(1)

式中,τADC为ADC的采样时间,即:采样频率fs的倒数;τRO为读出1位数字信号所需要的时间,取决于主时钟的频率;nbit为ADC转换的分辨率。nparallel为并行输出的位数;因此,在一定的帧频条件下,对芯片级ADC的转换速率要求非常高,比如:规格1280×1024,帧频50 Hz,ADC的采样速率为66 Msps(Mega-sample per second)。

2.2 列级数字化技术

列级数字化技术是一种在读出电路列级实现模数转换的技术,像素阵列的每列有一个ADC或者1个以上的ADC同时工作。列级数字化技术是目前最流行和应用最广的技术途径。

主要有几个明显的优点:其一,可以大幅提升一帧数据的转换频率,列级数字化一帧数据的转换速率如公式(2)所示,提高帧频:

(2)

其二,ADC的转换频率可以大幅降低,如果读出电路每列具有一个ADC,规格1280×1024,帧频为50 Hz,则ADC的采样速率为52 ksps(kilo-samples per second),即:行频。其三,功耗可以比较低,甚至低于模拟电路的功耗,主要是由于列级数字化技术消除了原有的高速模拟电路,列级数字信号可以非常高的速度读出。

列级数字化的主要挑战主要包括几方面:第一,列级ADC的版图设计会受到列级宽度的限制,潜在消除了大部分ADC架构在列级的应用;第二,由于列级ADC呈列级排布,存在模拟域、数字域信号分布以及串扰问题,特别是将几千个中高分辨率的ADC集成在一个芯片上,需要精心设计时钟树电路和高功耗模拟驱动电路;第三,需要考虑多个ADC的输出码流,外部的处理电路能够对输出的码流进行正确的解码。

2.3 像素级数字化技术

像素级数字化技术是一种将ADC集成在单个像元面积内的技术,像素级数字化技术的发展主要得益于CMOS集成电路制造工艺线宽的不断减小,使得在有限的像元面积内可以高密度的集成晶体管。每个像元输出单独的数字信号,极大地提高数字信号的读出速度,像素级数字化一帧数据转换速率为:

(3)

像素级ADC技术ADC转换频率可以非常低,如果每个像素具有一个完整的ADC结构,规格1280×1024,帧频50 Hz,则ADC的采样速率为50 sps(samples per second)。

像素级ADC主要优点:①在所有的数字化技术具有最高的带宽;②极大提升了电荷处理能力和动态范围,弱化了最大信号和最小噪声的关系;③像素单元可以很快重构不同大小的阵列。其主要挑战主要包括几方面:①像素级数字化技术明显受到像元面积限制;②功耗比较大,每个像元都会产生与辐射强度成正比的动态功耗;③受像元面积限制,ADC电路的设计尺寸通常比较小,恶化了电路的非均匀性和低频噪声。

2.4 三种实现方式对比

根据三种数字化实现方式转换速率公式,典型值M=N,τADC=1 μs,τRO=10 ns,nbit=nparallel=12绘制转换速率图如1所示。可以看出采用多个ADC方式,无论像素级数字化方式还是列级数字化方式,转换速率明显高于芯片级实现方式;当像素阵列规模比较小时,芯片级数字化可以实现比较高转换速率,当阵列规模比较大时(比如:1280×1024),列级数字化技术与像素级数字化技术转换速率已经非常接近[1]。

芯片级数字化技术优点是可以利用专业ADC公司的IP,降低开发风险,图像重构和校正比较简单;其缺点是当读出电路的分辨率要求比较高时,带宽、码率、功耗会成为明显的瓶颈,要满足百万像素中等规模读出电路的动态范围和可接受的数据速率,采用芯片级ADC技术实现是非常困难,几乎是不可以实现的;列级数字化技术对工作于视频速率甚至更高速率的百万像素级别的读出电路是一种比较好的选择;像素级ADC技术比较适合规模中等、间距较大、动态范围和带宽要求比较高的读出电路,同时容忍比较高的功耗。

3 列级模数转换技术

将多个ADC集成在读出电路的列级,可以实现比较高的帧数据转换速率;但由于受列级间距限制和ADC并行排布的特点,ADC在分辨率、噪声、速度、功耗方面提出了新的要求。

3.1 列级ADC指标[1]

3.1.1 ADC的分辨率

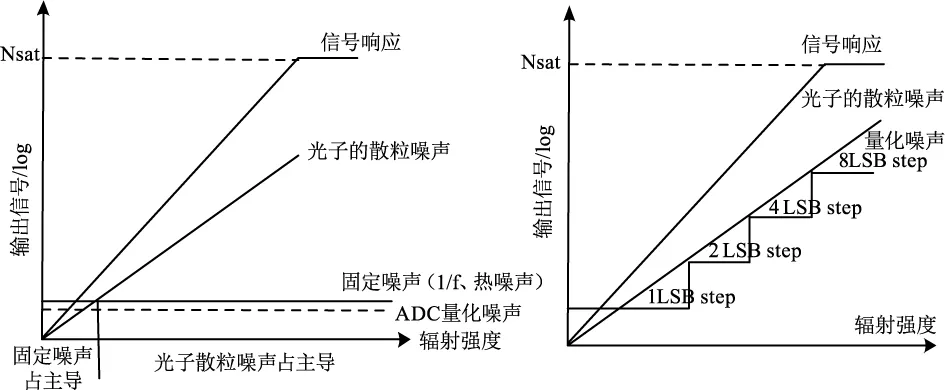

从图2可以看出,随着辐射强度的增加,当辐射强度达到一定程度时,光子散粒噪声在整个红外探测器系统中噪声占主导,利用此辐射特点,当背景温度较高时,实际上可以放松ADC量化的精度[2],具体如公式:

(4)

式中:k,量化步长的倍数,取值1,2,4,8,…;

r,量化噪声与光子噪声之比,保持定值,光子噪声增加,量化噪声可以相应增加;

Nsat,饱和电子数,与ADC输入范围一致;

Nsig,ADC量化步长翻倍时对应的信号大小。

3.1.2 ADC的噪声和面积

将多个ADC集成在读出电路列级会引起随机噪声,同时,由于不同列ADC电路存在失配,将会产生列级固定图形噪声,图像上会存在列信号差异。

列级ADC对单个ADC的版图设计约束比较严格,如果每列具有一个ADC,则ADC版图设计宽度必须小于等于像素单元的宽度,进而会限制ADC种类。

3.1.3 ADC的速度与功耗

ADC的速度是一个非常重要指标,ADC的速度与NADC的数量、Npixels、τF、τRO、nbits、nparallel的关系如公式(5)所示。ADC的数量NADC越大,ADC的速度要求越低。ADC的速度在读出速度、像素阵列大小和输出吞吐量存在折中关系。

(5)

式中:τF为帧周期;

τRO为读出一位数字信号所需要的时间,取决于主时钟的频率;

nbit为ADC转换的分辨率;

nparallel为并行输出的位数;

NADC为像素阵列所拥有的ADC的数量。

由于红外焦平面工作在深低温环境中,因此,ADC的功耗控制非常关键,列级数字化读出电路的功耗主要由列级ADC的功耗和后续读出电路的功耗决定,功耗与转换速度存在折中设计,功耗会随着分辨率和帧率线性增加。

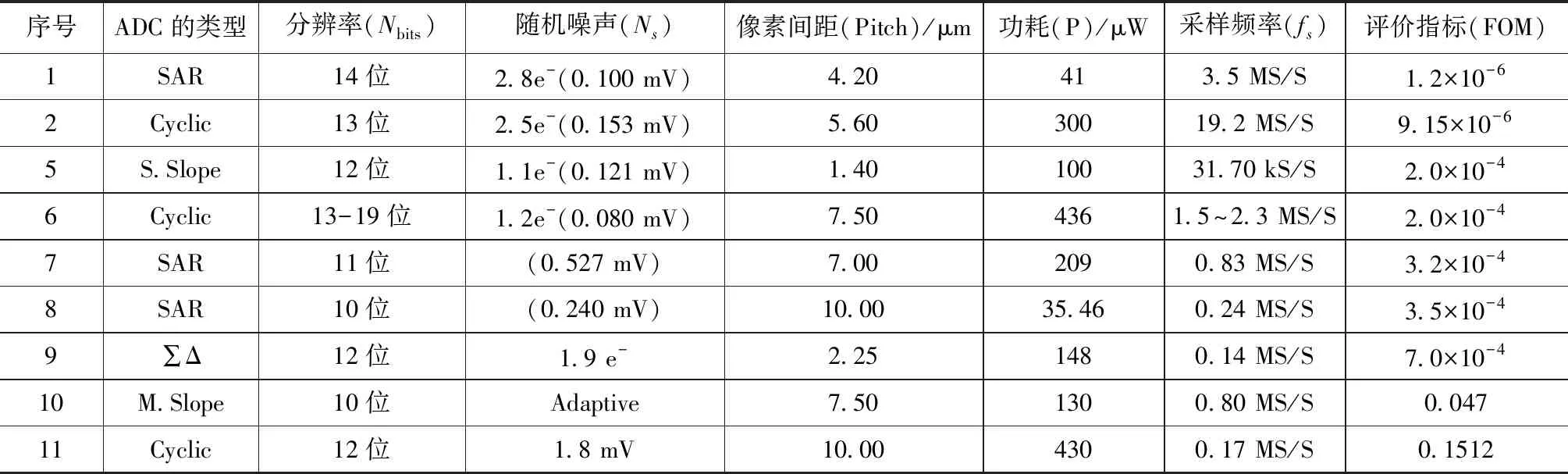

3.2 适用于列级实现的ADC技术

目前,列级数字化技术已经广泛应用在可见光领域,表1列出了部分CMOS可见光芯片采用的ADC类型,用在可见光领域的列级模数转换技术包括SAR、Cyclic、Single Slope、Sigma-Delta以及Multiple-Ramp ADC技术。由于制冷型红外焦平面阵列应用要求高分辨(有效位≥13)、低功耗、小像素间距,下面重点介绍适用于红外焦平面读出电路的DRSS(Dual Ramp Single Slope)技术和Sigma-Delta ADC技术。

表1 各种列级ADC架构指标对比[1]

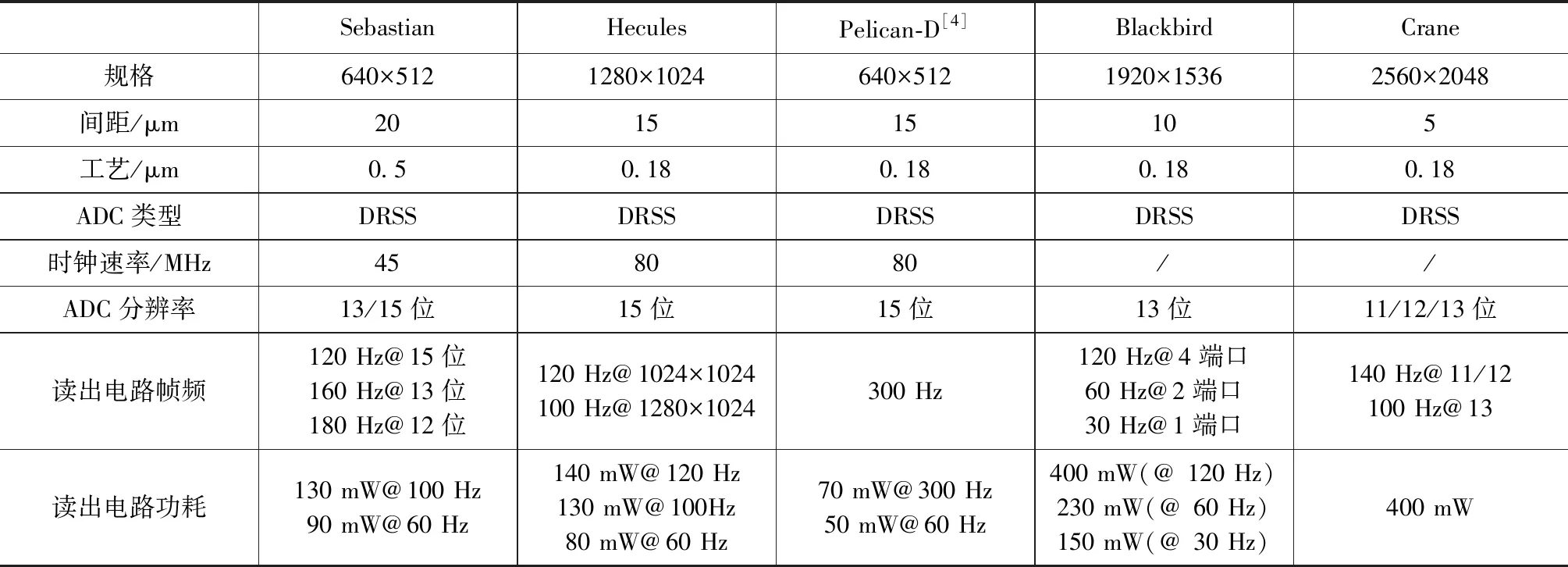

表2 SCD 基于DRSS技术的读出电路指标

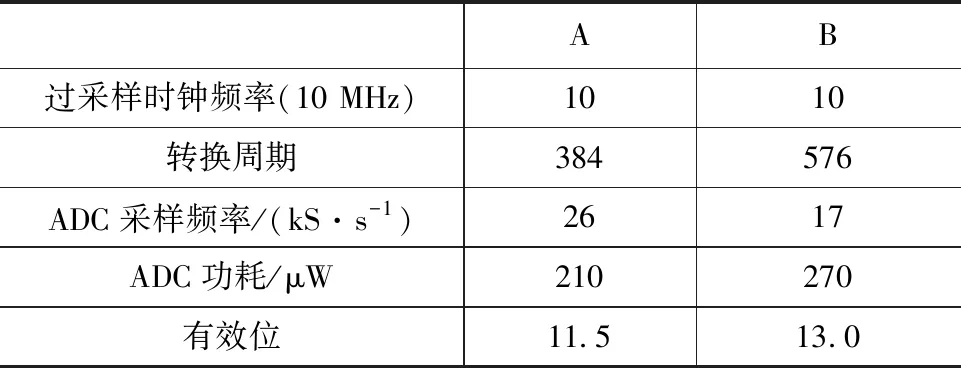

表3 CEA_LETI ADC技术指标

(6)

3.2.1 双斜坡单斜率ADC(Dual Ramp Single Slop ADC)[2]

列级ADC技术在CMOS可见光领域已经很普及,主要得益于列级ADC有助于大面阵的信号的高速读出。列级ADC通常会采用单斜率ADC架构,其优点是列级仅仅需要一个比较器,减小了列级面积开支,列级电路的均匀性、匹配性可以做的比较好;其缺点是ADC的转换时间随着位数呈指数级别增加,限制了高分辨率红外焦平面读出电路的读出速度。

(1)Single Slop ADC

单斜率ADC电路原理图如图3所示,主要由可复位的积分器、比较器和计数器组成,其中积分器主要产生精准参考斜坡信号。ADC转换时刻,计数器清零,积分器复位,输入级信号接入比较器,积分器开始产生斜坡信号,同时,计数器开始计数,模拟信号通过对脉冲信号计数转换成时间信号,最终获得时间-数字信号转换。ADC的精度取决于时钟生成器、积分器的RC时间常数以及参考电压Vref的精度,如公式(7)和(8)所示。

(7)

(8)

单斜率转换速度受限于时钟速度,N位分辨率的ADC需要的转换速度为2N+K时钟周期,K为RAMP复位时间和转换结果锁存时间,适用于地行频、低分辨率的应用场合,比如:分辨率N=12位的单斜率ADC,其转换时间为4096个时钟,当时钟速度位50 MHz时,行周期应大于82 μs,这么低的行频对读出电路而言是不可接受的。

(2)Dual Ramp Single Slop ADC[3]

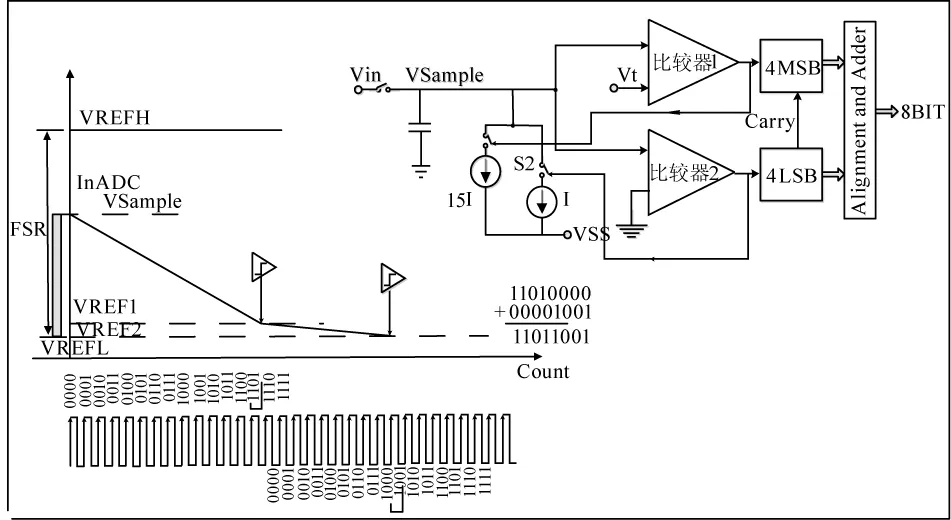

双斜坡单斜率ADC是多斜坡单斜率ADC的一种,主要是为降低单斜率ADC的转换时间,其原理图如图4所示。

双斜坡单斜率ADC电路主要包括:反相采样保持电路、两个参考电流源、比较器1和比较器2、时钟产生器和计数器。

ADC转换开始时,计数器清零,S3开关闭合,信号在电容C上积分,S1和S2开关断开,电容C不会发生电荷泄放;S3断开,输入信号Vin在C上完成采样保持;然后S1闭合,电流源以I的大小对电容C进行放电,直至积分器的输出达到Vt值,在放电t1期间,粗分计数器完成计数脉冲的计数,粗分计数器最大计数值为255;比较器1探测到预阈值电压Vt时,S1断开,S2闭合,另一个电流源以I/256值对电容C继续放电,直到比较器2探测到0,放电期间t2,细分计数器开始计数。如果细分计数器的值大于255,则向粗分计数器产生进位,粗分计数器加1。通过这种方式,可以获得16位的数字输出信号,ADC的转换速度可以提高128倍,即2N/2/2倍。

图5为DRSS ADC 工作原理图,要实现8位的分辨率,DRSS只需要32时钟,普通的单斜率ADC需要256个时钟,提高了8倍。

以色列SCD公司基于DRSS ADC技术路线成功设计了系列列级数字化读出电路,列级ADC的分辨率为15位,FoMPE为100 fJ/LSB,数据密度为85 ksps/20 μm,时钟速率为45 MHz,转换时间为2×256个时钟,帧频100 Hz,功耗130 mW[4]。

3.2.2 Sigma Delta ADC(Δ∑ ADC)

Sigma-DeltaADC引入了过采样和噪声整形,可大幅度降低电容噪声的影响,而且对于元件失配不敏感,可以小面积实现。传统Sigma-delta ADC适用于连续时间信号进行持续采样,面积和功耗开销比较大,而增量式Sigma-Delta ADC可以实现点对点的A/D转换,非常适合应用在红外焦平面读出电路阵列中。

(1)增量式1阶Δ∑ADC结构

增量式1阶Sigma-Delta ADC原理如图6所示。

内嵌∑Δ调制器,通过噪声整形获得比较高的精度,每次数据转换需要M个时钟周期,然后RST复位信号对调制器和抽取滤波器的所有存储单元进行清零。增量式ADC工作是间歇性的,采取采样-转换循环工作方式,适用于低频高精度转换,增量式1阶Sigma-Delta ADC 转化速度非常慢,如果分辨率为N,则1阶结构完成一次转换需要2N时钟周期,不适合大阵列高帧频高分辨率的应用。为了提高转速速度,需要提升增量式Δ∑ADC结构的阶数。

(2)增量式2阶Δ∑ADC结构

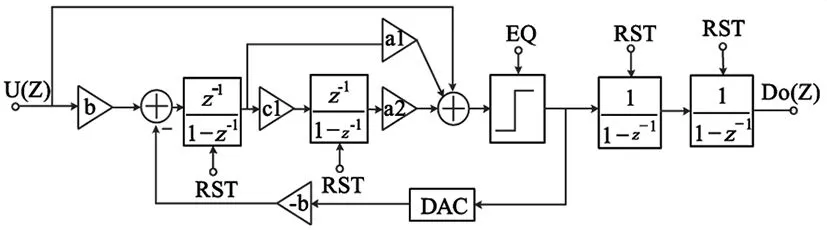

增量式2阶Δ∑ADC结构如图7所示。

CEA_LETI基于增量式2阶Δ∑ADC结构,完成了ADC性能的测试,其性能表所示。

(3)增量式3阶Δ∑ADC结构[5]

增量式3阶Δ∑ADC结构如图8所示。在每个转换器周期开始时,用Reset信号对每个积分器进行复位,以清除前一个转换的记忆效应。后续的数字抽取滤波器采用3阶串联的数字积分器,Reset信号也用于对数字积分器进行复位。

增量式3阶Δ∑ADC有效位与转换周期的关系如公式(9)所示。从公式可以清楚的得知,随着转换周期M的增加,有效位数也相应的增加;但公式(9)c1,c2,b比例因子不能独立选择,否则会影响环路的稳定性。如果输入信号接近VREF,增量式高阶Δ∑ADC环路将会变得非常不稳定,一般情况下,增量式2阶Δ∑ADC的输入Vin应≤0.9VREF,增量式3阶Δ∑ADC的输入Vin应≤0.75VREF。当每次转换脉冲数M越大,为了避免积分器过载,c1,c2,b比例因子必须越小,因此转换周期数M需要最优选择。如果分辨率需要16位,输入信号V≤0.67VREF,采用增量式2阶Δ∑ADC结构,每次转换周期需要537个时钟周期,采用增量式3阶Δ∑ADC结构,每次转换周期需要158个时钟周期。

≈3log2(M)+log2(c2c1b)-2.6

(9)

数字抽取滤波器的原理框图如图9所示。对应于3阶Δ∑ADC调制器,数字抽取滤波器由三级数字积分器构成。首先,Δ∑调制器所输出的1位数字码流进入第一级积分器(8位计数器),计数得到的数据再经过两级累加(14位& 19位accumulator),最后得到16位的A/D转换结果。

3阶1位 CIFF结构SDM和抽取滤波器的仿真结果如图10所示。可以看到采用目前SDM ADC结构,结合过采样率OSR=80和160,信噪比可以达到80 dB以上。

图1 不同数字化方式转换频率

图2 利用光子的散粒噪声,通过二进制方式抬高ADC的量化噪声

图3 单斜率ADC原理图

图4 双斜坡单斜率ADC原理图

图5 DRSS ADC工作原理图

图6 增量型一阶Δ∑ ADC工作原理图

图7 增量式2阶Δ∑ADC架构

图8 增量式3阶SDM ADC设计架构

图9 抽取滤波器结构

图10 三阶 Δ∑OSR与SNDR的关系

4 结 论

通过对比三种数字化的实现方式特点,像素级数字化方式和列级数字化方式的帧转换速率明显高于芯片级实现方式;当阵列规模比较小时,芯片级数字化可以实现比较高转换速率,当阵列规模比较大时,列级数字化技术与像素级数字化技术转换速率已经非常接近。列级数字化技术由于不完全受像元面积限制,已经成为主流的读出电路数字化方式,单斜率ADC由于电路结构简单,广泛应用在CMOS可见光领域,但由于转换速度极慢,不太适用高帧频、高分辨率的红外焦平面应用;双斜坡单斜率不仅结构简单,而且转换速度提高了2N/2/2倍,比较适合列级集成和高端红外应用。Sigma-Delta ADC引入了过采样和噪声整形,模拟电路对于元件失配不敏感,有利于列级窄面积实现,而增量式Sigma-Delta ADC可以实现点对点的A/D转换,非常适合应用在红外焦平面读出电路阵列中。